印制電路板屏蔽要點通過有遠(yuǎn)見的設(shè)計和精確的裝配,使用印制電路板屏蔽可顯著節(jié)約成本[hide][/hide]

2009-10-13 08:18:00

的原理和一些基本布局、布線原則。然后通過大量的實踐,在實踐中摸索、領(lǐng)悟并掌握布局、布線原則,積累經(jīng)驗,才能不斷地提高印制電路板的設(shè)計水平。 印制電路板上的干擾及抑制 干擾現(xiàn)象在整機調(diào)試中經(jīng)常出現(xiàn),其

2018-09-19 16:16:06

印制電路板上的地線怎么處理?

2021-04-26 06:04:03

`請問印制電路板分層設(shè)計的原則有哪些?`

2020-02-27 16:55:19

印制電路板制作的基礎(chǔ)知識制造印刷電路板的基本步驟

2021-04-21 06:59:09

`請問印制電路板制造的關(guān)鍵技術(shù)有哪些?`

2020-01-13 16:30:35

,是印制電路板的可靠性設(shè)計的一種常規(guī)做法,配置原則如下: ●電源輸入端跨接一個10~100uF的電解電容器,如果印制電路板的位置允許,采用100uF以上的電解電容器的抗干擾效果會更好。 ●為每個集成電路芯片

2018-09-18 15:40:00

`請問印制電路板屬于集成電路產(chǎn)業(yè)嗎?`

2019-08-30 17:50:07

` 誰來闡述一下印制電路板常用的基材有哪些?`

2019-12-19 16:37:06

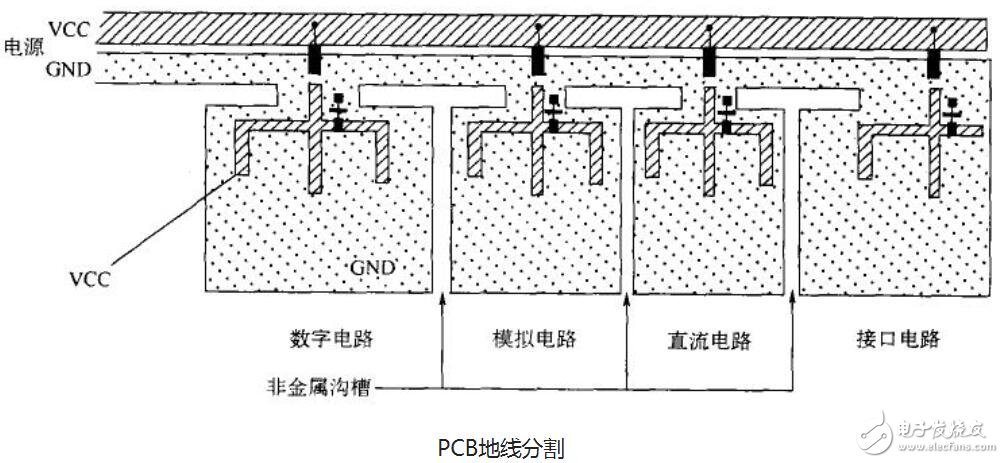

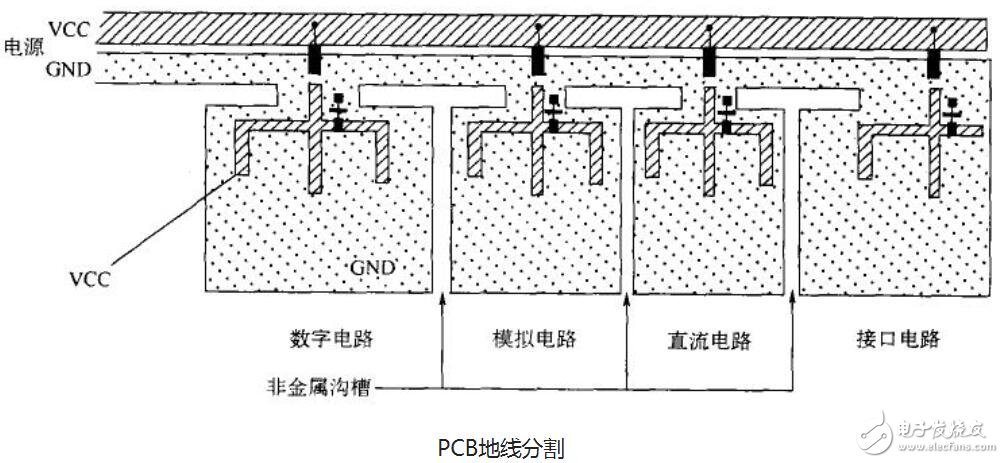

影響。例如,如果印制板兩條細(xì)平行線靠得很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,在設(shè)計印制電路板的時候,應(yīng)注意采用正確的方法。一、地線設(shè)計 在電子設(shè)備中,接地是控制干擾的重要方法。如能

2018-08-24 16:48:13

印制電路板手動測試原理是什么?印制電路板手動測試的方法有哪些?

2021-04-25 08:42:51

誰來闡述一下印制電路板有哪幾部分構(gòu)成?

2019-12-18 16:09:36

印制電路板溫升因素分析熱設(shè)計原則元器件的排布要求布線時的要求

2021-02-22 07:36:28

本帖最后由 eehome 于 2013-1-5 10:03 編輯

以印制電路板的電磁兼容性為核心,分析了電磁干擾的產(chǎn)生機理,介紹在設(shè)計、裝配印制電路板時應(yīng)采取的抗干擾措施。

2012-03-31 14:33:52

印制電路板時可采取的抗干擾措施。 關(guān)鍵詞:印制電路板;干擾;噪聲;電磁兼容性 引言 印制電路板的設(shè)計質(zhì)量不僅直接影響到電子產(chǎn)品的可靠性,還關(guān)系到產(chǎn)品的穩(wěn)定性,甚至是設(shè)計成敗的關(guān)鍵。因此,在設(shè)繪印制板圖

2013-09-09 11:01:48

印制電路板的抗干擾設(shè)計

2012-08-17 23:49:52

` 誰來闡述一下印制電路板的作用是什么?`

2019-12-18 15:46:17

`請問誰能詳細(xì)介紹下印制電路板的元器件裝焊技術(shù)?`

2020-03-24 16:12:34

三層和三層以上導(dǎo)電圖形和絕緣材料層壓合成的印制板為多層印制電路板。在絕緣基板上制成三層以上印制電路的印制板稱為多層印制電路板。它由幾層較薄的單面板或雙面板粘合而成,其厚度一股為1,2~2.5

2018-09-03 10:06:12

本帖最后由 gk320830 于 2015-3-7 18:54 編輯

印制電路板的可靠性設(shè)計-設(shè)計原則-抗干擾措施PCB設(shè)計的一般原則 要使電子電路獲得最佳性能,元器件的布且及導(dǎo)線的布設(shè)是很重

2013-08-26 15:42:16

,焊盤最小直徑可取(d+1.0)mm。 PCB及電路抗干擾措施 印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計的幾項常用措施做一些說明。1.電源線設(shè)計 根據(jù)印制

2018-08-29 16:36:43

很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,在設(shè)計印制電路板的時候,應(yīng)注意采用正確的方法。 在電子設(shè)備中,接地是控制干擾的重要方法。如能將接地和屏蔽正確結(jié)合起來使用,可解決大部分干擾

2018-08-28 11:58:34

的噪聲,是印制電路板的可靠性設(shè)計的一種常規(guī)做法,配置原則如下: ●電源輸入端跨接一個10~100uF的電解電容器,如果印制電路板的位置允許,采用100uF以上的電解電容器的抗干擾效果會更好。 ●為每個

2018-09-12 15:34:27

由于印制電路板從整體上看比較“雜亂無章”,因此印制電路板的識圖步驟和識圖要領(lǐng)如下。 1.找到印制電路板的接地點 在印制電路板中可以明顯看到大面積的銅箔線,可以將其作為接地點,檢測時都以接地

2021-02-05 15:55:12

印制電路板設(shè)計原則及抗干擾措施

2012-08-05 21:41:45

采用自動的方法進(jìn)衍印制電路板設(shè)計和生成布線圖,以及到一個什么樣的程度,取決于很多因素。每一種方法都有它最合適的使用范圍以供選擇。 1.手工設(shè)計和生成布線圖 對于簡單的單面板和雙面板,用手

2018-09-07 16:26:40

電子設(shè)備的可靠性產(chǎn)生不利影響。例如,如果印制板兩條細(xì)平行線靠得很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,建議設(shè)計印制電路板的時候,應(yīng)注意接地是控制干擾的重要方法。如能將接地和屏蔽

2018-02-26 12:15:21

板的布局: 印制電路板上的元器件放置的通常順序: 放置與結(jié)構(gòu)有緊密配合的固定位置的元器件,如電源插座、指示燈、開關(guān)、連接件之類,這些器件放置好后用軟件的LOCK功能將其鎖定,使之以后不會被誤移動

2012-04-23 17:38:12

信號的相互干擾。 (5)排版連線圖的設(shè)計 排版連線圖是指:用簡單線條表示印制導(dǎo)線的走向和元器件的連接關(guān)系的圖樣。如圖6所示。 (6)根據(jù)電原理圖繪制印制電路板圖的草圖 首先要選定排版方向及確定

2023-04-20 15:21:36

d為引線孔徑。對高密度的數(shù)字電路,焊盤最小直徑可取(d+1.0)mm。12PCB及電路抗干擾措施印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計的幾項常用措施做一些說明。13

2018-09-11 10:03:18

盤外徑D一般不小于(d+1.2)mm,其中d為引線孔徑。對高密度的數(shù)字電路,焊盤最小直徑可取(d+1.0)mm。 12、PCB及電路抗干擾措施 印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里

2018-09-20 11:12:35

點,印制板地線形成網(wǎng)格要足夠?qū)挼取! ?)軟件抗干擾技術(shù)。除了硬件上要采取一系列的抗干擾措施外,在軟件上也要采取數(shù)字濾波、設(shè)置軟件陷阱、利用看門狗程序冗余設(shè)計等措施使系統(tǒng)穩(wěn)定可靠地運行。特別地,當(dāng)儲能

2018-09-03 11:18:48

印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計的幾項常用措施做一些說明。1.電源線設(shè)計:根據(jù)印制線路板電流的大小,盡量加租電源線寬度,減少環(huán)路電阻。同時、使電源線、地線

2018-08-07 11:06:19

形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,在設(shè)計印制電路板的時候,應(yīng)注意采用正確的方法。 1 接地麥斯艾姆 地線設(shè)計在電子設(shè)備中,接地是控制干擾的重要方法。如能將接地和屏蔽正確結(jié)合起來

2012-12-15 10:05:06

。對高密度的數(shù)字電路,焊盤最小直徑可取(d+1.0)mm。 PCB及電路抗干擾措施 印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計的幾項常用措施做一些說明。 1.電源線

2018-09-14 16:22:33

本帖最后由 gk320830 于 2015-3-7 09:05 編輯

PCB設(shè)計原則和抗干擾措施印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著

2013-10-23 11:09:50

本帖最后由 gk320830 于 2015-3-7 15:28 編輯

PCB設(shè)計原則和抗干擾措施印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著

2013-09-25 10:23:46

的數(shù)字電路,焊盤最小直徑可取(d+1.0)mm。 PCB及電路抗干擾措施 印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計的幾項常用措施做一些說明。 1.電源線設(shè)計 根據(jù)

2018-09-10 16:56:41

的數(shù)字電路,焊盤最小直徑可取(d+1.0)mm。 PCB及電路抗干擾措施 印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計的幾項常用措施做一些說明。 1.電源線設(shè)計 根據(jù)印制

2018-08-31 11:53:51

印制電路板設(shè)計原則和抗干擾措施

2021-04-25 06:48:40

設(shè)計的一種常規(guī)做法,配置原則如下: ●電源輸入端跨接一個10~100uF的電解電容器,如果印制電路板的位置允許,采用100uF以上的電解電容器的抗干擾效果會更好。 ●為每個集成電路芯片配置一個0.01uF

2014-11-19 13:49:12

光電印制電路板的概念光電印制電路板的發(fā)展現(xiàn)狀光電印制電路的板的光互連結(jié)構(gòu)原理

2021-04-23 07:15:28

可能使其互連線最短; 印制板上高頻連線的元件盡可能靠近走線短; 以減少高頻信號的分布參數(shù)和電磁干擾, 這樣才能夠提高敏感信號源的抗干擾能力。3.1.3 減小線路板邊緣的耦合回路印制電路板的板邊處理是否合理

2011-07-16 11:50:08

能力差(與剛性印制電路板相比而言) ,所以必須提供足夠的導(dǎo)線寬度。圖12-8 中給出了電流在1A 以上時,選擇導(dǎo)線寬度的原則。一些承載大電流的導(dǎo)線彼此面對面或鄰近放置時,考慮到熱量集中的問題,必須給出

2013-09-10 10:49:08

僅在ˉ面有導(dǎo)電圖形的印制板稱為單面印制電路板。厚度為0,2~5,0 mm的絕緣基板上一面覆有銅箔,另一面沒有覆銅。通過印制和腐蝕的方法,在銅箔上形成印制電路,無覆銅一面放置元器件。囚其只能在單面

2018-09-04 16:31:22

印刷電路板的抗干擾設(shè)計原則數(shù)字電路、單片機的抗干擾設(shè)計切斷干擾傳播路徑的常用措施提高敏感器件抗干擾性能的常用措施

2021-03-17 08:00:01

印刷電路板的抗干擾設(shè)計原則是什么?

2021-11-11 06:53:46

兩面都有導(dǎo)電圖形的印制板為雙面印制電路板。在絕緣基板的兩面均覆有銅箔,可在兩面制成印制電路,它兩面都可以布線,需要用金屬化孔連通。由于雙面印制電路的布線密度較高,所以能減小設(shè)備的體積。適用于一般要求的電子設(shè)備,如電子計算機、電了儀器、儀表等。

2018-09-04 16:31:24

如何提高印制電路板的識圖速度?有什么技巧嗎?

2021-04-21 06:35:11

預(yù)防印制電路板在加工過程中產(chǎn)生翹曲印制電路板翹曲整平方法

2021-02-25 08:21:39

的射頻電路的性能指標(biāo)直接影響整個產(chǎn)品的質(zhì)量,射頻電路印制電路板( PCB)的抗干擾設(shè)計對于減小系統(tǒng)電磁信息輻射具有重要的意義。射頻電路PCB的密度越來越高, PCB設(shè)計的好壞對抗干擾能力影響很大,同一

2018-11-23 11:03:18

印制電路板的抗干擾規(guī)劃關(guān)于減小系統(tǒng)電磁信息輻射具有重要的含義。射頻電路板的密度越來越高,射頻PCB印制電路板規(guī)劃的好壞對立干擾影響很大,同一電路,不同的射頻PCB印制電路板規(guī)劃結(jié)構(gòu),其功能目標(biāo)會相差很大

2023-06-08 14:48:14

曲線獲取中采用各種測試手段、技術(shù)和方法,為建立最佳圖形提供指導(dǎo)。 14)IPC-TR-460A:印制電路板波峰焊接故障排除清單。為可能由波峰焊接引起的故障而推薦的一個修正措施清單。 15)IPC

2018-09-20 11:06:00

變化而產(chǎn)生的噪聲,是印制電路板的可靠性設(shè)計的一種常規(guī)做法。配置原則如下:電源輸入端跨接一個10~100uF的電解電容器,如果印制電路板的位置允許,采用100uF以上的電解電容器的抗干擾效果會好。為每個

2015-02-09 15:37:15

慮的主要因素�闡述了外形與布局�層數(shù)與厚度�孔與焊盤�線寬與間距的影響因素�設(shè)計原則及其計算關(guān)系�文中結(jié)合生產(chǎn)實踐對重點制作過程加以說明�關(guān)鍵詞� � 多層印制電路板� 設(shè)計� 制作� 黑化� 凹蝕

2008-08-15 01:14:56

深圳市印制電路板行業(yè)清潔生產(chǎn)技術(shù)指引目錄1 總論 11.1 概述 11.2 編制依據(jù)和原則 11.3 適用范圍 22 印制電路板行業(yè)主要生產(chǎn)工藝及污染環(huán)節(jié)分析 42.1 主要生產(chǎn)工藝 42.2 主要

2019-04-09 07:35:41

直徑可取(d+1.0)mm。PCB及電路抗干擾措施印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計的幾項常用措施做一些說明。 (1)電源線設(shè)計根據(jù)印制線路板電流的大小,盡量

2018-08-30 10:49:11

為完成印制電路板檢測的要求,已經(jīng)產(chǎn)生了各種各樣的檢測設(shè)備。自動光學(xué)檢測( AOI) 系統(tǒng)通常用于成層前內(nèi)層的測試;在成層以后,X 射線系統(tǒng)監(jiān)控對位的精確性和細(xì)小的缺陷;掃描激光系統(tǒng)提供了在回流

2018-11-22 15:50:21

印制電路板的檢測要領(lǐng)是什么?組裝并焊接的印制電路板存在哪些缺陷?

2021-04-23 07:16:25

隨著通信技術(shù)的發(fā)展,無線射頻電路技術(shù)運用越來越廣,其中的射頻電路的性能指標(biāo)直接影響整個產(chǎn)品的質(zhì)量,射頻電路印制電路板( PCB)的抗干擾設(shè)計對于減小系統(tǒng)電磁信息輻射具有重要的意義。射頻電路PCB

2020-11-23 12:17:20

如題高頻電路 印制電路板設(shè)計 在實際布線中需要注意些什么? 怎樣避免線路之間的干擾?

2013-02-27 11:17:20

印制電路板基本原則是什么?

2021-04-21 06:45:37

請問印制電路板是怎樣應(yīng)用互聯(lián)技術(shù)的?

2021-04-21 06:36:39

信號的分布參數(shù)和電磁干擾, 這樣才能夠提高敏感信號源的抗干擾能力。 3.1.3 減小線路板邊緣的耦合回路 印制電路板的板邊處理是否合理, 決定著是否能夠更加有效地抑制信號的對外干擾。為防止高速數(shù)字電路

2018-09-12 15:01:56

印制電路板設(shè)計規(guī)范:規(guī)范印制電路板工藝設(shè)計,滿足印制電路板可制造性設(shè)計的要求,為硬件設(shè)計人員提供印制電路板工藝設(shè)計準(zhǔn)則,為工藝人員審核印制電路板可制

2008-12-28 17:00:45 68

68 印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著電于技術(shù)的飛速發(fā)展,PGB的密度越來越高。PCB設(shè)計的好壞對抗干擾能力影響

2009-04-25 16:44:40 66

66 印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著電于技術(shù)的飛速發(fā)展,PGB的密度越來越高。PCB設(shè)計的好壞對抗

2009-10-16 16:43:39 85

85 介紹了電子線路在進(jìn)行印制電路板設(shè)計(PCB)的過程中應(yīng)該遵循的設(shè)計方法,以及按照PCB設(shè)計的一般原則的同時,如何進(jìn)行抗干擾及抑制噪聲的設(shè)計。

2010-08-04 15:07:42 0

0

印制電路板設(shè)計原則和抗干擾措施

2006-06-30 19:40:49 1155

1155 印制電路板的分類

印制電路板根據(jù)制作材料可分為剛性印制板和撓性印制板。

剛性印制板有酚醛紙質(zhì)層壓板、環(huán)

2009-03-08 10:33:40 1768

1768 印制電路板的設(shè)計基礎(chǔ)電子設(shè)計人員的電路設(shè)計思想最終要落實到實體,即做成印制電路板。印制電路板的基材及選用,組成電路各要素的物理特性,如過孔、槽、

2009-03-08 10:35:43 1606

1606 印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著電于技術(shù)的飛速發(fā)展,PGB的密度越來越高。PCB設(shè)計的好壞對抗干

2009-07-03 14:05:03 549

549 PCB設(shè)計原則和抗干擾措施

印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著

2009-11-16 16:52:27 671

671 印制電路板的印制圖案要寬而短

印制電路板圖上的印制導(dǎo)線是將敷銅板需要的銅箔保存下來,構(gòu)成連接元器件的導(dǎo)線,本書將這

2009-11-19 09:07:20 400

400 印制電路板設(shè)計原則和抗干擾措施 印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著電于

2009-11-19 14:49:02 496

496 印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計的幾項常用措施做一些說明。

1.

2010-10-22 16:25:01 903

903 印刷電路板的抗干擾設(shè)計原則,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-15 17:54:07 0

0 EMC-制作印制電路板的基本原則,有需要的下來看看。

2016-03-29 16:49:35 0

0 印制電路板的抗干擾設(shè)計,有需要的下來看看。

2016-03-29 15:07:10 15

15 單片機系統(tǒng)設(shè)計中印制電路板_PCB_的抗干擾技術(shù),感興趣的小伙伴們可以看看。

2016-07-18 15:06:45 0

0 印制電路板的抗干擾設(shè)計,有需要的下來看看

2016-07-29 19:05:18 30

30 印制電路板設(shè)計原則和抗干擾措施,下來看看。

2017-01-10 21:35:23 0

0 PCB電路板是電子產(chǎn)品中電路元件和器件的支撐件。即使電路原理圖設(shè)計正確,印制電路板設(shè)計不當(dāng),也會對電子產(chǎn)品的可靠性產(chǎn)生不利影響。在設(shè)計印制電路板的時候,應(yīng)注意采用正確的方法,遵守PCB設(shè)計的一般原則

2017-09-22 14:39:12 15

15 本文首先闡述了印制線路板的制造原理,其次介紹了印制電路板的質(zhì)量控制和印制電路板質(zhì)量認(rèn)證的基本要求,最后介紹了印制電路板設(shè)計質(zhì)量的要求。

2018-05-03 09:33:49 4744

4744

本文首先闡述了為什么叫印制電路板以及印制電路板來源與發(fā)展,其次介紹了印制電路板的優(yōu)點和制作工藝,最后介紹了印制電路板在下游各領(lǐng)域中的運用及未來發(fā)展趨勢。

2018-05-03 09:59:53 7382

7382 本文開始介紹了設(shè)計印制電路板的大體步驟,其次介紹了印制電路板設(shè)計遵循的原則與印制電路板的裝配,最后介紹了簡單DIY印制電路板設(shè)計制作詳細(xì)步驟與過程。

2018-05-03 14:55:15 48073

48073 PCB是電子產(chǎn)品中電路元件和器件的支撐件。即使電路原理圖設(shè)計正確,印制電路板設(shè)計不當(dāng),也會對電子產(chǎn)品的可靠性產(chǎn)生不利影響。在設(shè)計印制電路板的時候,應(yīng)注意采用正確的方法,遵守的一般原則,并應(yīng)符合抗干擾設(shè)計的要求。

2019-05-06 14:20:00 4288

4288 本文首先介紹了印制電路板的一般布局原則,其次介紹了印制電路板(PCB)行業(yè)深度分析,最后介紹了印制電路板的前景。

2019-05-17 17:48:59 3554

3554

印制電路板的抗干擾設(shè)計與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計的幾項常用措施做一些說明。

2019-08-29 09:41:29 1020

1020 本文檔的主要內(nèi)容詳細(xì)介紹的是印制電路板的設(shè)計基礎(chǔ)教程免費下載主要內(nèi)容包括了:1 印制電路板概述,2 印制電路板布局和布線原則,3 Protel99SE印制板編輯器,4 印制電路板的工作層面

2019-10-10 14:53:39 0

0 原理圖設(shè)計正確,印制電路板設(shè)計不當(dāng),也會對電子產(chǎn)品的可靠性產(chǎn)生不利影響。例如,如果印制板兩條細(xì)平行線靠得很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,在設(shè)計印制電路板的時候,應(yīng)注意采用正確的方法,遵守PCB設(shè)計的一般原則,并應(yīng)符合抗干擾設(shè)計的要求。

2020-05-05 14:41:00 2955

2955 印刷電路板的抗干擾設(shè)計原則

2022-12-30 09:21:14 2

2

68

68 66

66 85

85 0

0 1606

1606 549

549 671

671 400

400 496

496 903

903 0

0 15

15 4744

4744

7382

7382 48073

48073 4288

4288 3554

3554

1020

1020 0

0 2955

2955 電子發(fā)燒友App

電子發(fā)燒友App

評論