PCB板上的高速信號需要進(jìn)行仿真串擾嗎?

2023-04-07 17:33:31

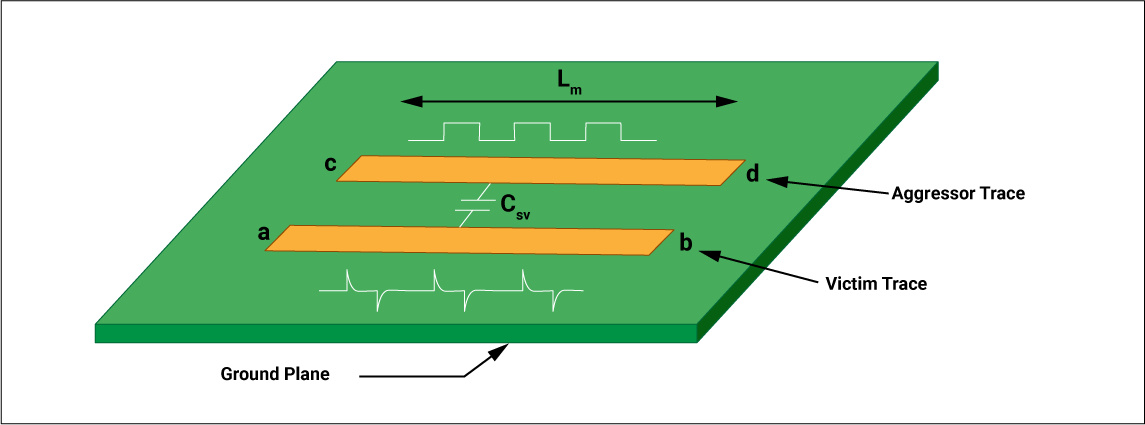

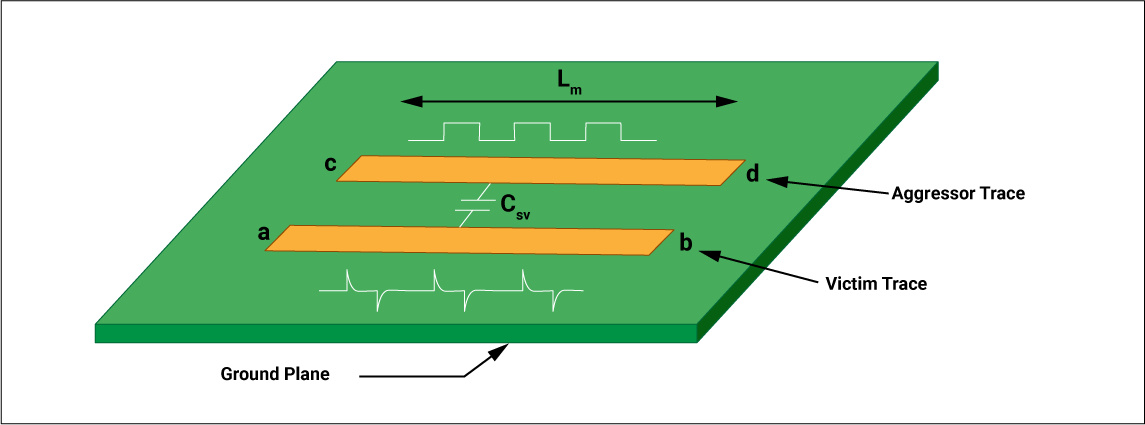

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串擾僅發(fā)生在信號跳變的過程當(dāng)中,并且

2018-08-29 10:28:17

請問PCB設(shè)計中如何避免平行布線?

2020-01-07 15:07:03

請問PCB設(shè)計中如何避免平行布線?

2020-02-26 16:39:38

PCB設(shè)計中如何處理串擾問題 變化的信號(例如階躍信號)沿

2009-03-20 14:04:47

現(xiàn)如今,PCB設(shè)計的技術(shù)雖然不斷提升,但不代表PCB設(shè)計工藝過程中沒有問題。其實(shí),任何領(lǐng)域或多或少都存在問題。本文我們就說說PCB設(shè)計中存在的那些漏洞,希望各位工程師遇到同樣問題可以避免入坑!

2020-10-30 07:55:32

強(qiáng)度,而在高頻電路中,滿足這一要求卻可以減少高頻信號對外的發(fā)射和相互間的耦合。 4、注意信號線近距離平行走線引入的“串擾” 高頻電路布線要注意信號線近距離平行走線所引入的“串擾”,串擾是指沒有直接

2018-09-17 17:36:05

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串擾僅發(fā)生在信號跳變的過程當(dāng)中,并且信號

2020-06-13 11:59:57

而非EMC專長的我們來說,其實(shí)也只能回答個大概,實(shí)話實(shí)說,在EMC領(lǐng)域我們也還在不斷的學(xué)習(xí)中,所以這篇文章也只是基于我們對EMC 的一些認(rèn)識,從PCB 設(shè)計中如何去盡量的避免問題的發(fā)生,其中說得

2016-07-29 18:37:23

?對串擾有一個量化的概念將會讓我們的設(shè)計更加有把握。1.3W規(guī)則在PCB設(shè)計中為了減少線間串擾,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時,則可保持大部分電場不互相干擾,這就是3W規(guī)則。如(圖1

2014-10-21 09:53:31

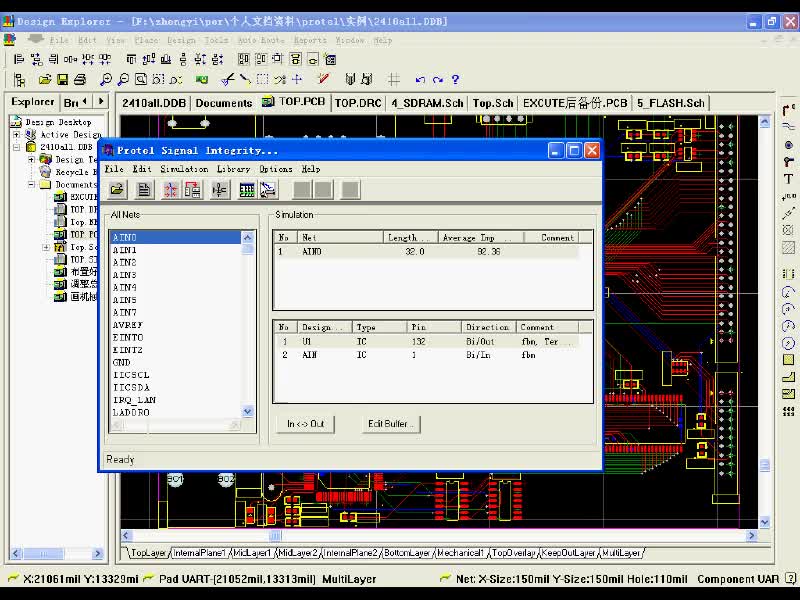

作者:一博科技SI工程師陳德恒3. 仿真實(shí)例在ADS軟件中構(gòu)建如下電路: 圖2圖2為微帶線的近端串擾仿真圖,經(jīng)過Allegro中的Transmission line Calculators軟件對其疊

2014-10-21 09:52:58

、PCB設(shè)計中,如何避免串擾?變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串擾僅發(fā)生在信號跳變

2017-04-29 15:11:46

的系統(tǒng),ESD的影響也會相對明顯。雖然大的系統(tǒng)有時ESD影響并不明顯,但設(shè)計時還是要多加注意,盡量防患于未然。70、PCB設(shè)計中,如何避免串擾?變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線

2014-08-29 14:16:58

1.PCB設(shè)計中,如何避免串擾? 變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串擾僅

2019-05-29 17:12:35

1.PCB設(shè)計中,如何避免串擾?變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串擾僅發(fā)生

2019-06-03 10:54:45

、PCB設(shè)計中,如何避免串擾? 變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信 號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串擾僅發(fā)生在信號跳變

2015-01-09 11:43:09

PCB設(shè)計中的3W規(guī)則主要是為了減少線間串擾,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時,則可保持70%的電場不互相干擾, 稱為3W規(guī)則。 如要達(dá)到98%的電場不互相干擾, 可使用10W的間距。

2019-05-21 09:40:51

信號層直接相鄰,以減少串擾。 主電源盡可能與其對應(yīng)地相鄰,構(gòu)成平面電容,降低電源平面阻抗。 兼顧層壓結(jié)構(gòu)對稱,利于制板生產(chǎn)時的翹曲控制。 以上為層疊設(shè)計的常規(guī)原則,在實(shí)際開展層疊設(shè)計時,PCB

2023-04-12 15:12:13

PCB設(shè)計需要避免得5個問題

2021-03-17 07:18:24

。兩根線(也包括PCB的薄膜布線)獨(dú)立的情況下,相互間應(yīng)該不會有電氣信號和噪聲等的影響,但尤其是兩根線平行的情況下,會因存在于線間的雜散(寄生)電容和互感而引發(fā)干擾。所以,串擾也可以理解為感應(yīng)噪聲

2018-11-29 14:29:12

在選擇模數(shù)轉(zhuǎn)換器時,是否應(yīng)該考慮串擾問題?ADI高級系統(tǒng)應(yīng)用工程師Rob Reeder:“當(dāng)然,這是必須考慮的”。串擾可能來自幾種途徑從印刷電路板(PCB)的一條信號鏈到另一條信號鏈,從IC中的一個

2019-02-28 13:32:18

于模擬接地。在數(shù)字電路設(shè)計中,有經(jīng)驗的PCB布局和設(shè)計工程師會特別注意高速信號和時鐘。在高速情況下,信號和時鐘應(yīng)盡可能短并鄰近接地層,因為如前所述,接地層可使串擾、噪聲和輻射保持在可控制的范圍。數(shù)字信號也

2023-12-19 09:53:34

串擾是由于線路之間的耦合引發(fā)的信號和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時代是字如其意、一目了然的表達(dá)。兩根線(也包括PCB的薄膜布線)獨(dú)立的情況下,相互間應(yīng)該不會有電氣信號

2019-08-08 06:21:47

的固著強(qiáng)度,而在高頻電路中,滿足這一要求卻可以減少高頻信號對外的發(fā)射和相互間的耦合。 4、注意信號線近距離平行走線引入的“串擾” 高頻電路布線要注意信號線近距離平行走線所引入的“串擾”,串擾是指沒有

2017-01-20 11:44:22

。4、PCB設(shè)計中,如何避免串擾?變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串擾僅發(fā)生

2018-03-30 17:32:52

幾個電源畢竟是不太實(shí)際的。但如果你有具體的條件,可以用不同電源當(dāng)然干擾會小些。6、PCB設(shè)計中,如何避免串擾?變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號

2018-03-23 17:03:15

產(chǎn)品的供電電源15V,而往往強(qiáng)電和弱點(diǎn)布線走的比較近,為避免強(qiáng)電串擾,在15V輸入到電路板后,需要在電路板上添加共模電感,減小串擾,該選擇什么樣型號的電感,還有這樣做對不對?

2013-07-21 10:16:05

。兩根線(也包括PCB的薄膜布線)獨(dú)立的情況下,相互間應(yīng)該不會有電氣信號和噪聲等的影響,但尤其是兩根線平行的情況下,會因存在于線間的雜散(寄生)電容和互感而引發(fā)干擾。所以,串擾也可以理解為感應(yīng)噪聲

2019-03-21 06:20:15

串擾的概念是什么?到底什么是串擾?

2021-03-05 07:54:17

什么是串擾?互感和互容電感和電容矩陣串擾引起的噪聲

2021-02-05 07:18:27

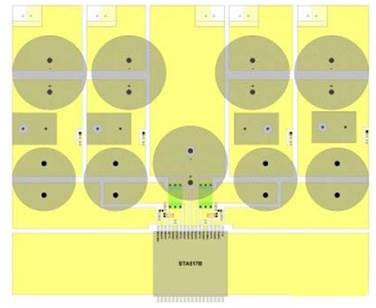

。對于8Gbps及以上的高速應(yīng)用更應(yīng)該注意避免此類問題,為高速數(shù)字傳輸鏈路提供更多裕量。本文針對PCB設(shè)計中由小間距QFN封裝引入串擾的抑制方法進(jìn)行了仿真分析,為此類設(shè)計提供參考。那么,什么是小間距QFN封裝PCB設(shè)計串擾抑制呢?

2019-07-30 08:03:48

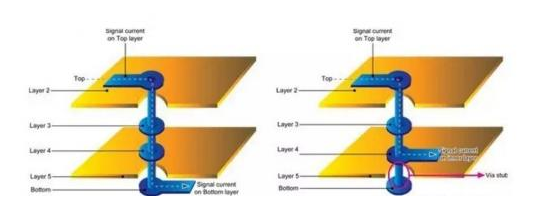

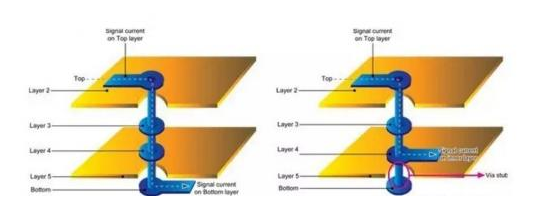

間耦合以及繞線方式等有關(guān)。隨著PCB走線信號速率越來越高,對時序要求較高的源同步信號的時序裕量越來越少,因此在PCB設(shè)計階段準(zhǔn)確知道PCB走線對信號時延的影響變的尤為重要。本文基于仿真分析DK,串擾,過孔

2015-01-05 11:02:57

的PCB設(shè)計中,要均衡考慮布線空間與串擾控制,遵循的規(guī)則可以理解為上面“3W”、“ 5H”兩種規(guī)則的結(jié)合體:“3H規(guī)則”,即傳輸線之間的間距不小于3倍的傳輸線與參考平面的距離H。另外,信號在互連鏈路中

2016-10-10 18:00:41

形成邊長超過200MIL的自環(huán)(14)建議相鄰層的布線方向成正交結(jié)構(gòu)說明:相鄰層的布線避免走成同一方向,以減少層間串擾,如果不可避免,特別是信號速率較高時,應(yīng)考慮用地平面隔離各布線層,用地信號隔離各信號線。

2017-01-23 16:04:35

形成邊長超過200MIL的自環(huán)(14)建議相鄰層的布線方向成正交結(jié)構(gòu)說明:相鄰層的布線避免走成同一方向,以減少層間串擾,如果不可避免,特別是信號速率較高時,應(yīng)考慮用地平面隔離各布線層,用地信號隔離各信號線。更多技術(shù)干貨可關(guān)注【快點(diǎn)PCB學(xué)院】公眾號

2017-01-23 09:36:13

、時序剖析、信號回流、串擾處置、單板EMC/EMI、電源地平面完好性等。而且,單板的設(shè)計密度也越來越大。這些PCB設(shè)計工作量比較大,如果全部由硬件工程師負(fù)責(zé),則大大延長了產(chǎn)品開發(fā)和上市的時間。 4

2020-06-23 15:43:12

在PCB設(shè)計中應(yīng)如何避免軌道塌陷?

2014-10-24 15:25:39

在設(shè)計fpga的pcb時可以減少串擾的方法有哪些呢?求大神指教

2023-04-11 17:27:02

傳輸線上出現(xiàn),它將和任何其它信號一樣的傳播,最終被傳輸?shù)絺鬏斁€末端的接收機(jī)上,這種串擾將會影響到接收機(jī)所能承受的噪聲的裕量。在低端的模擬應(yīng)用中,小到0.01%的串擾也許是可以接受的,在高速數(shù)字應(yīng)用中,一般

2019-07-08 08:19:27

的影響一般都是負(fù)面的。為減少串擾,最基本的就是讓干擾源網(wǎng)絡(luò)與***擾網(wǎng)絡(luò)之間的耦合越小越好。在高密度復(fù)雜PCB設(shè)計中完全避免串擾是不可能的,但在系統(tǒng)設(shè)計中設(shè)計者應(yīng)該在考慮不影響系統(tǒng)其它性能的情況下,選擇適當(dāng)

2018-09-11 15:07:52

不斷出現(xiàn),PCB設(shè)計人員還必須繼續(xù)應(yīng)對電磁兼容性和干擾問題。技巧4:去耦電容去耦電容可減少串擾的不良影響,它們應(yīng)位于設(shè)備的電源引腳和接地引腳之間,這樣可以確保交流阻抗較低,減少噪聲和串擾。為了在寬頻

2022-06-07 15:46:10

靜態(tài)存儲器SRAM是一款不需要刷新電路即能保存它內(nèi)部存儲數(shù)據(jù)的存儲器。在SRAM 存儲陣列的設(shè)計中,經(jīng)常會出現(xiàn)串擾問題發(fā)生。那么要如何減小如何減小SRAM讀寫操作時的串擾,以及提高SRAM的可靠性呢

2020-05-20 15:24:34

在PCB設(shè)計中,電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當(dāng)今電路板設(shè)計和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下。本文給大家分享如何在PCB設(shè)計中避免出現(xiàn)電磁問題。

2021-02-01 07:42:30

的;我試了好幾種方式,覺得可能是數(shù)字地和模擬地之間的串擾,AGND和GND我是單點(diǎn)用0歐姆電阻連接的,有人說要用AGND包住8978,但看demo板并不是這樣解決,發(fā)射wm8978中我用咪頭輸入,去掉了耳機(jī)部分電路,原理圖:PCB

2019-07-23 04:36:16

在嵌入式系統(tǒng)硬件設(shè)計中,串擾是硬件工程師必須面對的問題。特別是在高速數(shù)字電路中,由于信號沿時間短、布線密度大、信號完整性差,串擾的問題也就更為突出。設(shè)計者必須了解串擾產(chǎn)生的原理,并且在設(shè)計時應(yīng)用恰當(dāng)?shù)姆椒ǎ?b class="flag-6" style="color: red">串擾產(chǎn)生的負(fù)面影響降到最小。

2019-11-05 08:07:57

。對于8Gbps及以上的高速應(yīng)用更應(yīng)該注意避免此類問題,為高速數(shù)字傳輸鏈路提供更多裕量。本文針對PCB設(shè)計中由小間距QFN封裝引入串擾的抑制方法進(jìn)行了仿真分析,為此類設(shè)計提供參考。二、問題分析在PCB設(shè)計

2018-09-11 11:50:13

8Gbps及以上的高速應(yīng)用更應(yīng)該注意避免此類問題,為高速數(shù)字傳輸鏈路提供更多裕量。本文針對PCB設(shè)計中由小間距QFN封裝引入串擾的抑制方法進(jìn)行了仿真分析,為此類設(shè)計提供參考。

2021-03-01 11:45:56

的布線可以抑制線間的串擾。規(guī)則六:高速PCB設(shè)計中的拓?fù)浣Y(jié)構(gòu)規(guī)則在高速PCB設(shè)計中,線路板特性阻抗的控制和多負(fù)載情況下的拓?fù)浣Y(jié)構(gòu)的設(shè)計,直接決定著產(chǎn)品的成功還是失敗。規(guī)則七:走線長度的諧振規(guī)則檢查信號線

2016-07-07 15:52:45

傳輸線,將走線高度限制在高于地線平面范圍要求以內(nèi),可以顯著減小串擾。 4、在布線空間允許的條件下,在串擾較嚴(yán)重的兩條線之間插入一條地線,可以起到隔離的作用,從而減小串擾。傳統(tǒng)的PCB設(shè)計由于缺乏高速

2018-12-11 19:48:52

本帖最后由 dianzijie5 于 2011-6-15 15:54 編輯

隨著PCB設(shè)計復(fù)雜度的逐步提高,對于信號完整性的分析除了反射,串擾以及EMI之外,穩(wěn)定可靠的電源供應(yīng)也成為設(shè)計者們

2011-06-15 15:54:23

布線技術(shù)實(shí)現(xiàn)信號串擾控制的設(shè)計策略EMC的PCB設(shè)計技術(shù)CADENCE PCB設(shè)計技術(shù)方案基于高速FPGA的PCB設(shè)計技術(shù)解析高速PCB設(shè)計中的時序分析及仿真策略闡述基于Proteus軟件的單片機(jī)仿真

2014-12-16 13:55:37

、電路板的設(shè)計、串擾的模式(反向還是前向)以及干擾線和***擾線兩邊的端接情況。下文提供的信息可幫助讀者加深對串擾的認(rèn)識和研究,從而減小串擾對設(shè)計的影響。 研究串擾的方法 為了盡可能減小PCB設(shè)計中的串

2018-11-27 10:00:09

在PCB電路設(shè)計中有很多知識技巧,之前我們講過高速PCB如何布局,以及電路板設(shè)計最常用的軟件等問題,本文我們講一下關(guān)于怎么解決PCB設(shè)計中消除串擾的問題,快跟隨小編一起趕緊學(xué)習(xí)下。 串擾是指在一根

2020-11-02 09:19:31

為什么這十個PCB設(shè)計錯誤要避免

2021-03-17 06:22:30

請問如何去避免PCB設(shè)計限制D類放大器的性能?

2021-04-21 06:25:09

。對于8Gbps及以上的高速應(yīng)用更應(yīng)該注意避免此類問題,為高速數(shù)字傳輸鏈路提供更多裕量。本文針對PCB設(shè)計中由小間距QFN封裝引入串擾的抑制方法進(jìn)行了仿真分析,為此類設(shè)計提供參考。二、問題分析在PCB設(shè)計

2022-11-21 06:14:06

變高,邊沿變陡,印刷電路板的尺寸變小,布線密度加大等都使得串擾在高速PCB設(shè)計中的影響顯著增加。串擾問題是客觀存在,但超過一定的界限可能引起電路的誤觸發(fā),導(dǎo)致系統(tǒng)無法正常工作。設(shè)計者必須了解串擾產(chǎn)生

2009-03-20 13:56:06

,或是布局布線后的仿真,都是為了使PCB板能快速達(dá)到最小的干擾。因此需要在設(shè)計過程中運(yùn)用以前的經(jīng)驗來解決現(xiàn)在的問題,以下就是有效避免布局布線中串擾的經(jīng)驗總結(jié):

?????? 1)容性耦合和感性耦合

2018-08-28 11:58:32

同名網(wǎng)絡(luò)DRC錯誤,兼容設(shè)計除外。(5)PCB設(shè)計完成后沒有未連接的網(wǎng)絡(luò),具PCB網(wǎng)絡(luò)與電路圖網(wǎng)表一致。(6)不允許出現(xiàn)Dangline Line。(7)如明確不需要保留非功能焊盤,光繪文件中必須去除

2017-02-10 10:42:11

形成邊長超過200MIL的自環(huán)(14)建議相鄰層的布線方向成正交結(jié)構(gòu)說明:相鄰層的布線避免走成同一方向,以減少層間串擾,如果不可避免,特別是信號速率較高時,應(yīng)考慮用地平面隔離各布線層,用地信號隔離各信號線。

2017-02-16 15:06:01

。 問:在高速PCB設(shè)計中,串擾與信號線的速率、走線的方向等有什么關(guān)系?需要注意哪些設(shè)計指標(biāo)來避免出現(xiàn)串擾等問題? 答:串擾會影響邊沿速率,一般來說,一組總線傳輸方向相同時,串擾因素會使邊沿速率變慢

2019-01-11 10:55:05

Z方向的并行距離遠(yuǎn)大于水平方向的間距時,就要考慮高速信號差分過孔之間的串擾問題。順便提一下,高速PCB設(shè)計的時候應(yīng)該盡可能最小化過孔stub的長度,以減少對信號的影響。如下圖所1示,靠近Bottom層

2018-09-04 14:48:28

方向的間距時,就要考慮高速信號差分過孔之間的串擾問題。順便提一下,高速PCB設(shè)計的時候應(yīng)該盡可能最小化過孔stub的長度,以減少對信號的影響。如下圖所1示,靠近Bottom層走線這樣Stub會比較短。或者

2020-08-04 10:16:49

高速PCB設(shè)計中的信號完整性概念以及破壞信號完整性的原因高速電路設(shè)計中反射和串擾的形成原因

2021-04-27 06:57:21

法避免平行分布,可在平行信號線的反面布置大面積“地”來大幅減少干擾;(4)在數(shù)字電路中,通常的時鐘信號都是邊沿變化快的信號,對外串擾大。所以在設(shè)計中,時鐘線宜用地線包圍起來并多打地線孔來減少分布電容,從而

2015-05-18 17:36:09

` 本帖最后由 cooldog123pp 于 2020-4-28 08:22 編輯

1.PCB設(shè)計中,如何避免串擾? 變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號

2019-05-31 13:19:06

避免PCB設(shè)計限制D類放大器性能的實(shí)踐設(shè)計經(jīng)驗:如果沒有遵循一些基本的布局指南,PCB設(shè)計將會限制D類放大器的性能或降低其可靠性。下面描述了D類放大器一些好的PC板布局實(shí)踐經(jīng)

2009-08-21 22:36:38 58

58 如何避免高速PCB設(shè)計中傳輸線效應(yīng)

1、抑止電磁干擾的方法

很好地解決信號完整性問題將改善PCB板的電磁兼容性(EMC)。其中非常重要的是保證PCB板有很好的接

2009-11-20 11:17:00 799

799 避免PCB設(shè)計限制D類放大器性能的實(shí)踐設(shè)計經(jīng)驗

介紹如果沒有遵循一些基本的布局指南,PCB設(shè)計將會限制D類放大器的性能或降低其可靠性。下面描述了D類放大器

2010-04-08 16:58:24 892

892

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復(fù)到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串?dāng)_僅發(fā)生在信號跳變的過程當(dāng)中,并且信號沿的變化(轉(zhuǎn)換率)越快,產(chǎn)生的串?dāng)_也就越大。 空間中耦合的電磁場可以提取為無數(shù)耦合電容和耦合電感的集合,其中由耦合電容產(chǎn)生的串?dāng)_信號在受害網(wǎng)絡(luò)上可以分成前向串?dāng)_和反向串?dāng)_Sc,這個兩個信號極性相同;由耦合電感產(chǎn)生的串?dāng)_

2017-11-29 14:13:29 0

0 其次從PI的角度考慮也是避免EMC問題的一個關(guān)鍵,把電源設(shè)計好,你的產(chǎn)品也可以說就成功了一半。

2019-01-06 09:16:47 803

803 電路板同時又要避免振鈴、噪聲引致的差錯,和地電位跳動等問題,實(shí)在相當(dāng)困難的。但是,當(dāng)你添加那些易受噪聲影響的模擬訊號線路逼近於方波激勵的數(shù)碼式數(shù)據(jù)線路,問題更為嚴(yán)重。

2019-04-30 12:00:00 382

382 焊橋當(dāng)電路板上未設(shè)計為電氣連接的兩個點(diǎn)被PCB焊接掩模的頂部無意中通過焊料連接時形成。

2019-09-05 14:02:00 10819

10819 在 PCB 設(shè)計中,您希望時鐘信號迅速到達(dá)其集成電路( IC )的目的地。但是,一種稱為時鐘偏斜的現(xiàn)象會導(dǎo)致時鐘信號早晚到達(dá)某些 IC 。當(dāng)然,這會導(dǎo)致各個 IC 的數(shù)據(jù)完整性不一致。 什么是時鐘

2020-09-16 22:59:02 1937

1937 對于EMI,一條叫做“侵犯走線”,另一條則是“受害走線”。電感和電容耦合會因為電磁場的存在而影響“受害”走線,從而在“受害走線”上產(chǎn)生正向和反向電流。這樣的話,在信號的發(fā)送長度和接收長度幾乎相等的穩(wěn)定環(huán)境中就會產(chǎn)生紋波。

2021-01-14 15:03:36 1580

1580

在PCB設(shè)計中,電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當(dāng)今電路板設(shè)計和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下。本文給大家分享如何在PCB設(shè)計中避免出現(xiàn)電磁問題。

2021-01-20 14:38:13 371

371 在PCB設(shè)計中,電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當(dāng)今電路板設(shè)計和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下。本文給大家分享如何在PCB設(shè)計中避免出現(xiàn)電磁問題。

2021-01-22 09:54:18 20

20 電子發(fā)燒友網(wǎng)為你提供PCB設(shè)計需要避免得5個問題資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-03 08:47:23 4

4 在PCB設(shè)計中,經(jīng)常出現(xiàn)電磁問題,如何有效避免呢,有以下七個小技巧。對于高頻信號,必須使用屏蔽電纜,其正面和背面均接地,消除EMI干擾。

2023-03-31 17:37:11 535

535

空間中耦合的電磁場可以提取為無數(shù)耦合電容和耦合電感的集合,其中由耦合電容產(chǎn)生的串?dāng)_信號在受害網(wǎng)絡(luò)上可以分成前向串?dāng)_和反向串?dāng)_Sc,這個兩個信號極性相同;由耦合電感產(chǎn)生的串?dāng)_信號也分成前向串?dāng)_和反向串?dāng)_SL,這兩個信號極性相反。

2023-08-21 14:26:46 218

218 從設(shè)計的角度來看,一個過孔主要由兩個部分組成,一是中間的鉆孔(drill hole),二是鉆孔周圍的焊盤區(qū)。這兩部分的尺寸大小決定了過孔的大小。很顯然,在高速,高密度的PCB設(shè)計時,設(shè)計者總是希望過孔越小越好,這樣板上可以留有更多的布線空間

2024-01-05 15:36:55 108

108

在PCB設(shè)計中,如何避免串?dāng)_? 在PCB設(shè)計中,避免串?dāng)_是至關(guān)重要的,因為串?dāng)_可能導(dǎo)致信號失真、噪聲干擾及功能故障等問題。 一、了解串?dāng)_及其原因 在開始討論避免串?dāng)_的方法之前,我們首先需要

2024-02-02 15:40:30 594

594

電子發(fā)燒友App

電子發(fā)燒友App

評論