?對(duì)串擾有一個(gè)量化的概念將會(huì)讓我們的設(shè)計(jì)更加有把握。1.3W規(guī)則在PCB設(shè)計(jì)中為了減少線間串擾,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時(shí),則可保持大部分電場(chǎng)不互相干擾,這就是3W規(guī)則。如(圖1

2014-10-21 09:53:31

作者:一博科技SI工程師陳德恒3. 仿真實(shí)例在ADS軟件中構(gòu)建如下電路: 圖2圖2為微帶線的近端串擾仿真圖,經(jīng)過(guò)Allegro中的Transmission line Calculators軟件對(duì)其疊

2014-10-21 09:52:58

PCB設(shè)計(jì)中如何處理串擾問(wèn)題 變化的信號(hào)(例如階躍信號(hào))沿

2009-03-20 14:04:47

變化的信號(hào)(例如階躍信號(hào))沿傳輸線由A到B傳播,傳輸線C-D上會(huì)產(chǎn)生耦合信號(hào),變化的信號(hào)一旦結(jié)束也就是信號(hào)恢復(fù)到穩(wěn)定的直流電平時(shí),耦合信號(hào)也就不存在了,因此串擾僅發(fā)生在信號(hào)跳變的過(guò)程當(dāng)中,并且

2018-08-29 10:28:17

變化的信號(hào)(例如階躍信號(hào))沿傳輸線由A到B傳播,傳輸線C-D上會(huì)產(chǎn)生耦合信號(hào),變化的信號(hào)一旦結(jié)束也就是信號(hào)恢復(fù)到穩(wěn)定的直流電平時(shí),耦合信號(hào)也就不存在了,因此串擾僅發(fā)生在信號(hào)跳變的過(guò)程當(dāng)中,并且信號(hào)

2020-06-13 11:59:57

串擾是信號(hào)完整性中最基本的現(xiàn)象之一,在板上走線密度很高時(shí)串擾的影響尤其嚴(yán)重。我們知道,線性無(wú)緣系統(tǒng)滿足疊加定理,如果受害線上有信號(hào)的傳輸,串擾引起的噪聲會(huì)疊加在受害線上的信號(hào),從而使其信號(hào)產(chǎn)生畸變

2019-05-31 06:03:14

。兩根線(也包括PCB的薄膜布線)獨(dú)立的情況下,相互間應(yīng)該不會(huì)有電氣信號(hào)和噪聲等的影響,但尤其是兩根線平行的情況下,會(huì)因存在于線間的雜散(寄生)電容和互感而引發(fā)干擾。所以,串擾也可以理解為感應(yīng)噪聲

2018-11-29 14:29:12

所謂串擾,是指有害信號(hào)從一個(gè)傳輸線耦合到毗鄰傳輸線的現(xiàn)象,噪聲源(攻擊信號(hào))所在的信號(hào)網(wǎng)絡(luò)稱為動(dòng)態(tài)線,***擾的信號(hào)網(wǎng)絡(luò)稱為靜態(tài)線。串擾產(chǎn)生的過(guò)程,從電路的角度分析,是由相鄰傳輸線之間的電場(chǎng)(容性)耦合和磁場(chǎng)(感性)耦合引起,需要注意的是串擾不僅僅存在于信號(hào)路徑,還與返回路徑密切相關(guān)。

2019-08-02 08:28:35

在選擇模數(shù)轉(zhuǎn)換器時(shí),是否應(yīng)該考慮串擾問(wèn)題?ADI高級(jí)系統(tǒng)應(yīng)用工程師Rob Reeder:“當(dāng)然,這是必須考慮的”。串擾可能來(lái)自幾種途徑從印刷電路板(PCB)的一條信號(hào)鏈到另一條信號(hào)鏈,從IC中的一個(gè)

2019-02-28 13:32:18

是ADI的SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號(hào)處理之后再畫到顯示屏上顯示實(shí)時(shí)波形。

調(diào)試發(fā)現(xiàn)顯示的信號(hào)有串擾,表現(xiàn)為某一路信號(hào)懸空之后,相鄰的那一路信號(hào)

2023-12-18 08:27:39

是ADI的SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號(hào)處理之后再畫到顯示屏上顯示實(shí)時(shí)波形。 調(diào)試發(fā)現(xiàn)顯示的信號(hào)有串擾,表現(xiàn)為某一路信號(hào)懸空之后,相鄰的那一路信號(hào)上

2018-09-06 14:32:00

串擾是由于線路之間的耦合引發(fā)的信號(hào)和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時(shí)代是字如其意、一目了然的表達(dá)。兩根線(也包括PCB的薄膜布線)獨(dú)立的情況下,相互間應(yīng)該不會(huì)有電氣信號(hào)

2019-08-08 06:21:47

了各自的見解,比如串擾,繞線,過(guò)孔,跨分割等等。本期我們就以不同模態(tài)下的串擾對(duì)信號(hào)時(shí)延的影響繼續(xù)通過(guò)理論分析和仿真驗(yàn)證的方式跟大家一起進(jìn)行探討。在開始仿真之前我們先簡(jiǎn)單的了解一下什么是串擾以及串擾

2023-01-10 14:13:01

串擾是信號(hào)完整性中最基本的現(xiàn)象之一,在板上走線密度很高時(shí)串擾的影響尤其嚴(yán)重。我們知道,線性無(wú)緣系統(tǒng)滿足疊加定理,如果受害線上有信號(hào)的傳輸,串擾引起的噪聲會(huì)疊加在受害線上的信號(hào),從而使其信號(hào)產(chǎn)生畸變

2019-04-18 09:30:40

為什么CC1101信道出現(xiàn)串擾現(xiàn)象?各位大神,我在使用CC1101的時(shí)候,遇到如下問(wèn)題,我購(gòu)買的是模塊,并非自己設(shè)計(jì),所有參數(shù),使用smart rf生成,參數(shù)如下:base frequency

2016-03-11 10:01:10

多了,這樣我想有個(gè)問(wèn)題就是,在正常采集時(shí),這幾個(gè)通道間會(huì)不會(huì)有互相串擾的問(wèn)題。謝謝。

另外我想知道互相串擾產(chǎn)生原因,如果能成放大器內(nèi)部解釋更好

2023-11-21 08:15:40

。兩根線(也包括PCB的薄膜布線)獨(dú)立的情況下,相互間應(yīng)該不會(huì)有電氣信號(hào)和噪聲等的影響,但尤其是兩根線平行的情況下,會(huì)因存在于線間的雜散(寄生)電容和互感而引發(fā)干擾。所以,串擾也可以理解為感應(yīng)噪聲

2019-03-21 06:20:15

什么是串擾?互感和互容電感和電容矩陣串擾引起的噪聲

2021-02-05 07:18:27

航空通信系統(tǒng)變得日益復(fù)雜,我們通常需要在同一架飛機(jī)上安裝多條天線,這樣可能會(huì)在天線間造成串擾,或稱同址干擾,影響飛機(jī)運(yùn)行。在本教程模型中,我們利用COMSOL Multiphysics 5.1 版本模擬了飛機(jī)機(jī)身上兩個(gè)完全相同的天線之間的干擾,其中一個(gè)負(fù)責(zé)發(fā)射,另一個(gè)負(fù)責(zé)接收,以此來(lái)分析串擾的影響。

2019-08-26 06:36:54

一、引言隨著電路設(shè)計(jì)高速高密的發(fā)展趨勢(shì),QFN封裝已經(jīng)有0.5mm pitch甚至更小pitch的應(yīng)用。由小間距QFN封裝的器件引入的PCB走線扇出區(qū)域的串擾問(wèn)題也隨著傳輸速率的升高而越來(lái)越突出

2019-07-30 08:03:48

數(shù)百毫伏的差分幅度。入侵(aggressor)信號(hào)與受害(victim)信號(hào)出現(xiàn)能量耦合時(shí)會(huì)產(chǎn)生串擾,表現(xiàn)為電場(chǎng)或磁場(chǎng)干擾。電場(chǎng)通過(guò)信號(hào)間的互電容耦合,磁場(chǎng)則通過(guò)互感耦合。方程式(1)和(2)分別是入侵信號(hào)

2019-05-28 08:00:02

串擾信號(hào)產(chǎn)生的機(jī)理是什么串擾的幾個(gè)重要特性分析線間距P與兩線平行長(zhǎng)度L對(duì)串擾大小的影響如何將串擾控制在可以容忍的范圍

2021-04-27 06:07:54

面對(duì)串擾,包地是萬(wàn)能的嗎?請(qǐng)看不一樣的解答

2016-12-30 16:29:07

相互作用時(shí)就會(huì)產(chǎn)生。在數(shù)字電路系統(tǒng)中,串擾現(xiàn)象相當(dāng)普遍,串擾可以發(fā)生在芯片內(nèi)核、芯片的封裝、PCB板上、接插件上、以及連接線纜上,只要有臨近的銅互連鏈路,就存在信號(hào)間的電磁場(chǎng)相互作用,從而產(chǎn)生串擾現(xiàn)象

2016-10-10 18:00:41

如果您給某個(gè)傳輸線的一端輸入信號(hào),該信號(hào)的一部分會(huì)出現(xiàn)在相鄰傳輸線上,即使它們之間沒(méi)有任何連接。信號(hào)通過(guò)周邊電磁場(chǎng)相互耦合會(huì)產(chǎn)生噪聲,這就是串擾的來(lái)源,它將引起數(shù)字系統(tǒng)的誤碼。一旦這種噪聲在相鄰

2019-07-08 08:19:27

變小,布線密度加大等都使得

串擾在高速

PCB設(shè)計(jì)中的影響顯著增加。

串擾問(wèn)題是客觀存在,但超過(guò)一定的界限可能引起電路的誤觸發(fā),導(dǎo)致系統(tǒng)無(wú)法正常工作。設(shè)計(jì)者必須了解

串擾產(chǎn)生的機(jī)理,并且在設(shè)計(jì)中應(yīng)用恰當(dāng)?shù)姆椒?/div>

2018-09-11 15:07:52

靜態(tài)存儲(chǔ)器SRAM是一款不需要刷新電路即能保存它內(nèi)部存儲(chǔ)數(shù)據(jù)的存儲(chǔ)器。在SRAM 存儲(chǔ)陣列的設(shè)計(jì)中,經(jīng)常會(huì)出現(xiàn)串擾問(wèn)題發(fā)生。那么要如何減小如何減小SRAM讀寫操作時(shí)的串擾,以及提高SRAM的可靠性呢

2020-05-20 15:24:34

在嵌入式系統(tǒng)硬件設(shè)計(jì)中,串擾是硬件工程師必須面對(duì)的問(wèn)題。特別是在高速數(shù)字電路中,由于信號(hào)沿時(shí)間短、布線密度大、信號(hào)完整性差,串擾的問(wèn)題也就更為突出。設(shè)計(jì)者必須了解串擾產(chǎn)生的原理,并且在設(shè)計(jì)時(shí)應(yīng)用恰當(dāng)?shù)姆椒ǎ?b class="flag-6" style="color: red">串擾產(chǎn)生的負(fù)面影響降到最小。

2019-11-05 08:07:57

一、引言隨著電路設(shè)計(jì)高速高密的發(fā)展趨勢(shì),QFN封裝已經(jīng)有0.5mm pitch甚至更小pitch的應(yīng)用。由小間距QFN封裝的器件引入的PCB走線扇出區(qū)域的串擾問(wèn)題也隨著傳輸速率的升高而越來(lái)越突出

2018-09-11 11:50:13

隨著電路設(shè)計(jì)高速高密的發(fā)展趨勢(shì),QFN封裝已經(jīng)有0.5mm pitch甚至更小pitch的應(yīng)用。由小間距QFN封裝的器件引入的PCB走線扇出區(qū)域的串擾問(wèn)題也隨著傳輸速率的升高而越來(lái)越突出。對(duì)于

2021-03-01 11:45:56

消除串擾的方法合理的PCB布局-將敏感的模擬部分與易產(chǎn)生干擾的數(shù)字部分盡量隔離,使易產(chǎn)生干擾的數(shù)字信號(hào)走線上盡量靠近交流地,使高頻信號(hào)獲得較好的回流路徑。盡量減小信號(hào)回路的面積,降低地線的阻抗,采用多點(diǎn)接地的方法。使用多層板將電源與地作為獨(dú)立的一層來(lái)處理。合理的走線拓樸結(jié)構(gòu)-盡量采用菊花輪式走線

2009-06-18 07:52:34

本文討論了串擾的組成,并向讀者展示了如何利用泰克的TDS8000B系列采樣示波器或CSA8000B系列通信信號(hào)分析儀來(lái)測(cè)量單面PCB板上的串擾。 隨著通信、視頻、網(wǎng)絡(luò)和計(jì)算機(jī)技術(shù)領(lǐng)域中數(shù)字系統(tǒng)

2018-11-27 10:00:09

雙絞線的性能在一直不斷的提高,但有一個(gè)參數(shù)一直伴隨著雙絞線,并且伴隨著雙絞線的發(fā)展,這個(gè)參數(shù)也越來(lái)越重要,它就是串擾 (Crosstalk)。串擾是影響數(shù)據(jù)傳輸最嚴(yán)重的因素之一。它是一個(gè)信號(hào)對(duì)另外一個(gè)

2018-01-19 11:15:04

在PCB電路設(shè)計(jì)中有很多知識(shí)技巧,之前我們講過(guò)高速PCB如何布局,以及電路板設(shè)計(jì)最常用的軟件等問(wèn)題,本文我們講一下關(guān)于怎么解決PCB設(shè)計(jì)中消除串擾的問(wèn)題,快跟隨小編一起趕緊學(xué)習(xí)下。 串擾是指在一根

2020-11-02 09:19:31

是SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號(hào)處理之后再畫到顯示屏上顯示實(shí)時(shí)波形。 調(diào)試發(fā)現(xiàn)顯示的信號(hào)有串擾,表現(xiàn)為某一路信號(hào)懸空之后,相鄰的那一路信號(hào)上就會(huì)出現(xiàn)噪聲。將采樣的時(shí)間延長(zhǎng)也無(wú)法消除串擾。想請(qǐng)教一下各路專家,造成串擾的原因和如何消除串擾,謝謝。

2019-05-14 14:17:00

高頻數(shù)字信號(hào)串擾的產(chǎn)生及變化趨勢(shì)串擾導(dǎo)致的影響是什么怎么解決高速高密度電路設(shè)計(jì)中的串擾問(wèn)題?

2021-04-27 06:13:27

一、引言隨著電路設(shè)計(jì)高速高密的發(fā)展趨勢(shì),QFN封裝已經(jīng)有0.5mm pitch甚至更小pitch的應(yīng)用。由小間距QFN封裝的器件引入的PCB走線扇出區(qū)域的串擾問(wèn)題也隨著傳輸速率的升高而越來(lái)越突出

2022-11-21 06:14:06

高速PCB串擾分析及其最小化 1.引言 &

2009-03-20 13:56:06

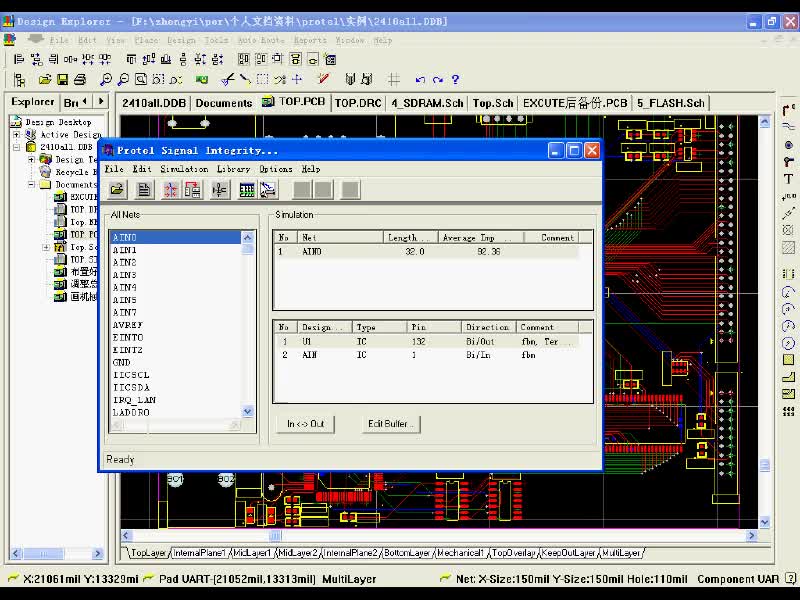

信號(hào)完整性問(wèn)題。因此,在進(jìn)行高速板級(jí)設(shè)計(jì)的時(shí)候就必須考慮到信號(hào)完整性問(wèn)題,掌握信號(hào)完整性理論,進(jìn)而指導(dǎo)和驗(yàn)證高速PCB的設(shè)計(jì)。在所有的信號(hào)完整性問(wèn)題中,串擾現(xiàn)象是非常普遍的。串擾可能出現(xiàn)在芯片內(nèi)部,也

2018-08-28 11:58:32

高速數(shù)字設(shè)計(jì)領(lǐng)域里,信號(hào)完整性已經(jīng)成了一個(gè)關(guān)鍵的問(wèn)題,給設(shè)計(jì)工程師帶來(lái)越來(lái)越嚴(yán)峻的考驗(yàn)。信號(hào)完整性問(wèn)題主要為反射、串擾、延遲、振鈴和同步開關(guān)噪聲等。本文基于高速電路設(shè)計(jì)的信號(hào)完整性基本理論,通過(guò)近端

2010-05-13 09:10:07

和解決方法。高速差分過(guò)孔間的串擾對(duì)于板厚較厚的PCB來(lái)說(shuō),板厚有可能達(dá)到2.4mm或者3mm。以3mm的單板為例,此時(shí)一個(gè)通孔在PCB上Z方向的長(zhǎng)度可以達(dá)到將近118mil。如果PCB上有0.8mm

2018-09-04 14:48:28

方向的間距時(shí),就要考慮高速信號(hào)差分過(guò)孔之間的串擾問(wèn)題。順便提一下,高速PCB設(shè)計(jì)的時(shí)候應(yīng)該盡可能最小化過(guò)孔stub的長(zhǎng)度,以減少對(duì)信號(hào)的影響。如下圖所1示,靠近Bottom層走線這樣Stub會(huì)比較短。或者

2020-08-04 10:16:49

串擾問(wèn)題產(chǎn)生的機(jī)理是什么高速數(shù)字系統(tǒng)的串擾問(wèn)題怎么解決?

2021-04-25 08:56:13

高速電路信號(hào)完整性分析與設(shè)計(jì)—串擾串擾是由電磁耦合引起的,布線距離過(guò)近,導(dǎo)致彼此的電磁場(chǎng)相互影響串擾只發(fā)生在電磁場(chǎng)變換的情況下(信號(hào)的上升沿與下降沿)[此貼子已經(jīng)被作者于2009-9-12 10:32:03編輯過(guò)]

2009-09-12 10:31:08

高速PCB設(shè)計(jì)中的信號(hào)完整性概念以及破壞信號(hào)完整性的原因高速電路設(shè)計(jì)中反射和串擾的形成原因

2021-04-27 06:57:21

在PCB O/S測(cè)試和AOI檢測(cè)時(shí)﹐會(huì)在PCB的最外層﹐綠漆下發(fā)現(xiàn)一種短路﹐我們叫做細(xì)絲短

2006-04-16 21:45:28 687

687 如何解決PCB組裝中焊接橋連缺陷

印刷線路板組裝包含的技術(shù)范圍很廣,從單面通孔插裝到復(fù)雜的雙面回焊組裝,以及需

2009-04-07 17:11:49 1445

1445 在PCB板的設(shè)計(jì)當(dāng)中,可以通過(guò)分層、恰當(dāng)?shù)牟季植季€和安裝實(shí)現(xiàn)PCB的抗ESD設(shè)計(jì)。在設(shè)計(jì)過(guò)程中,通過(guò)預(yù)測(cè)可以將絕大多數(shù)設(shè)計(jì)修改僅限于增減元器件。通過(guò)調(diào)整PCB布局布線,能夠很好地防范ESD。以下是一些常見的防范措施。

2016-12-07 01:07:11 1734

1734 有人說(shuō)過(guò),世界上只有兩種電子工程師:經(jīng)歷過(guò)電磁干擾的和沒(méi)有經(jīng)歷過(guò)電磁干擾的。伴隨著PCB走線速遞的增加,電磁兼容設(shè)計(jì)是我們電子工程師不得不考慮的問(wèn)題。

2019-01-11 10:34:14 3574

3574 有人說(shuō)過(guò),世界上只有兩種電子工程師:經(jīng)歷過(guò)電磁干擾的和沒(méi)有經(jīng)歷過(guò)電磁干擾的。

2019-01-17 13:57:56 3422

3422 沉銀工藝印在制線路板制造中不可缺少,但是沉銀工藝也會(huì)造成缺陷或報(bào)廢。

預(yù)防措施的制訂需要考量實(shí)際生產(chǎn)中化學(xué)品和設(shè)備對(duì)各種缺陷的貢獻(xiàn)度,才能避免或消除缺陷并提升良品率。

2019-07-22 15:36:06 1639

1639

信號(hào)布線在以前通常被看作是一種簡(jiǎn)單的概念,從布線角度看,視頻信號(hào)、語(yǔ)音信號(hào)或數(shù)據(jù)信號(hào)之間沒(méi)有什么區(qū)別。因此過(guò)去很少有人關(guān)心信號(hào)布線問(wèn)題。然而,現(xiàn)在情況有了完全的改變。視頻信號(hào)傳輸速度目前已經(jīng)達(dá)到每個(gè)通道3.3Gbps,數(shù)據(jù)信號(hào)更是遠(yuǎn)超過(guò)每通道5Gbps。

2019-06-24 14:51:04 383

383 為了控制共模EMI,電源層要有助於去耦和具有足夠低的電感,這個(gè)電源層必須是一個(gè)設(shè)計(jì)相當(dāng)好的電源層的配對(duì)。有人可能會(huì)問(wèn),好到什麼程度才算好?問(wèn)題的答案取決於電源的分層、層間的材料以及工作頻率(即IC上升時(shí)間的函數(shù))。通常,電源分層的間距是6mil,夾層是FR4材料,則每平方英寸電源層的等效電容約為75pF。顯然,層間距越小電容越大。

2019-05-30 14:18:57 3029

3029 所謂的毛頭就是批鋒,產(chǎn)生的原因是因?yàn)殂~具有延展性,在鉆孔過(guò)程中刀具無(wú)法對(duì)齊進(jìn)行很好的切削或者其他物料沒(méi)有很好的進(jìn)行擬制所導(dǎo)致。解決方案有以下幾種:

2019-05-23 15:26:13 8383

8383 你可能不會(huì)有三只熊走進(jìn)來(lái)在您的PCB設(shè)計(jì)上,但您的電源傳輸網(wǎng)絡(luò)()設(shè)計(jì)的印刷電路板(PCB)仍然可以成就或休息,以便您晚安睡覺(jué)(或午睡)。如果沒(méi)有將電源正確地分配給需要它的設(shè)備,電路板可能會(huì)遇到與我家中不均勻的熱量分布相同的問(wèn)題。電路板的功率和過(guò)熱可能會(huì)太結(jié)塊,或者太稀疏,無(wú)法有效地散發(fā)能量和熱量。

2019-07-26 08:40:08 2235

2235 如圖所示,這種刷焊焊盤在調(diào)試或者后端維修時(shí)最左邊的地焊盤很容易脫落,后果是整個(gè)板子就報(bào)廢了,產(chǎn)生這種問(wèn)題的原因是:此處焊盤和地的連接面積過(guò)大,那么導(dǎo)熱就很快,焊接過(guò)程中很快就冷卻了,拉扯過(guò)程中自然就容易脫落了。

2019-10-14 14:25:51 13632

13632

很多時(shí)候,PCB走線中途會(huì)經(jīng)過(guò)過(guò)孔、測(cè)試點(diǎn)焊盤、短的stub線等,都存在寄生電容,必然對(duì)信號(hào)造成影響。走線中途的電容對(duì)信號(hào)的影響要從發(fā)射端和接受端兩個(gè)方面分析,對(duì)起點(diǎn)和終點(diǎn)都有影響。

2019-10-22 15:54:51 1287

1287 介于PCB的結(jié)構(gòu)特點(diǎn)與失效的主要模式,其中金相切片分析是屬于破壞性的分析技術(shù),一旦使用了這兩種技術(shù),樣品就破壞了,且無(wú)法恢復(fù);另外由于制樣的要求,可能掃描電鏡分析和X射線能譜分析有時(shí)也需要部分破壞樣品。

2019-11-01 15:01:35 1884

1884 EMI關(guān)注的是電磁能量的輻射,包括外部電磁環(huán)境對(duì)自身系統(tǒng)的干擾,以及自身輻射的電磁能量對(duì)外部系統(tǒng)的干擾。這些干擾都不能超過(guò)一個(gè)限度,超過(guò)了這個(gè)限度就會(huì)引起問(wèn)題,這些干擾歸根結(jié)底還是影響了系統(tǒng)的信號(hào)完整性。

2019-12-18 15:12:44 6007

6007 隨著電子產(chǎn)業(yè)的高速發(fā)展,PCB布線越來(lái)越精密,多數(shù)PCB廠家都采用干膜來(lái)完成圖形轉(zhuǎn)移,干膜的使用也越來(lái)越普及,但仍遇到很多客戶在使用干膜時(shí)產(chǎn)生很多誤區(qū),現(xiàn)總結(jié)出來(lái),以便借鑒。

一、干膜掩孔出現(xiàn)破孔

2019-12-19 15:10:21 3288

3288 隨著PCB行業(yè)迅速發(fā)展,PCB逐漸邁向高精密細(xì)線路、小孔徑、高縱橫比(6:1-10:1)方向發(fā)展,孔銅要求20-25Um,其中DF線距≤4mil之板,一般生產(chǎn)PCB公司都存在電鍍夾膜問(wèn)題。

2020-03-08 13:34:00 2960

2960 還是要說(shuō)鎳缸事。如果鎳缸藥水長(zhǎng)期得不到良好保養(yǎng),沒(méi)有及時(shí)進(jìn)行碳處理,那么電鍍出來(lái)鎳層就會(huì)容易產(chǎn)生片狀結(jié)晶,鍍層硬度增加、脆性增強(qiáng)。嚴(yán)重會(huì)產(chǎn)生發(fā)黑鍍層問(wèn)題。

2020-03-25 15:15:49 2682

2682 在PCB制造過(guò)程涉及到工序較多,每道工序都有可能發(fā)生質(zhì)量缺陷,這些質(zhì)量總是涉及到諸多方面,解決起來(lái)比較麻煩,由于產(chǎn)生問(wèn)題的原因是多方面的,有的是屬于化學(xué)、機(jī)械、板材、光學(xué)等等方面。

2020-04-13 15:06:02 828

828 對(duì)集成電路的影響:對(duì)于晶體管電路而言,溫度上升會(huì)導(dǎo)致PN結(jié)少子濃度急劇增高,導(dǎo)致電流放大系數(shù)增大,燒毀電路。對(duì)于MOS工藝的電路,同樣,溫度上升會(huì)導(dǎo)致電流加大,形成正反饋,致使溫度越來(lái)越高,直到燒毀。

2020-08-24 15:47:36 2502

2502

,但您可能會(huì)發(fā)現(xiàn)布局和布線會(huì)因攻擊者的蹤跡而產(chǎn)生強(qiáng)烈的串?dāng)_。 那么,在設(shè)計(jì)中哪里可以找到串?dāng)_,以及在PCB中識(shí)別出不良走線的最簡(jiǎn)單方法是什么?您可以使用全波場(chǎng)求解器,但是可以在PCB設(shè)計(jì)軟件中使用更簡(jiǎn)單的分析功能來(lái)識(shí)別和抑

2021-01-13 13:25:55 2123

2123 來(lái)源:羅姆半導(dǎo)體社區(qū)? PCB( Printed Circuit Board),中文名稱為印制電路板,又稱印刷線路板,是重要的電子部件,是電子元器件的支撐體,是電子元器件電氣連接的載體。由于它是采用

2022-12-13 11:25:21 955

955 印制電路板是電子設(shè)備中最重要的組成部分。隨著電子技術(shù)的普及和集成電路技術(shù)的發(fā)展,各種電磁干擾問(wèn)題紛紛出現(xiàn),由于電磁干擾造成的經(jīng)濟(jì)損失也在增加。因此,電磁兼容越來(lái)越重要。本文旨在分析 PCB 中出

2022-12-08 11:18:25 451

451 有用的注釋,例如“不要將組件x放置在組件y附近”。所構(gòu)建的電路存在電線布線和線束問(wèn)題,這些問(wèn)題是切實(shí)而直接的。 那些日子已經(jīng)一去不復(fù)返了,PCB現(xiàn)在統(tǒng)治著我們的世界。這些PCB從低端消費(fèi)產(chǎn)品的廉價(jià),單面,穿孔酚醛板到多層,

2021-03-24 15:15:18 3699

3699 PCB起泡是波峰焊接中常見的一種缺陷,主要現(xiàn)象是PCB焊錫面出現(xiàn)斑點(diǎn)或鼓起,造成PCB分層;那么在波峰焊工藝中造成PCB水泡的原因究竟有哪些呢?又該如何解決PCB起泡的問(wèn)題呢?

2021-04-06 10:10:41 1728

1728 隨著消費(fèi)者越來(lái)越關(guān)注產(chǎn)品的質(zhì)量及可靠性,電子產(chǎn)品的智能化、輕量化程度越來(lái)越高,對(duì)PCBA的加工工藝也提出了更高的要求,所以線路板三防漆的使用得以廣泛。但由于操作人員對(duì)三防漆產(chǎn)品特性及應(yīng)用工藝的專業(yè)性不夠,使用過(guò)程中現(xiàn)了各種問(wèn)題,今天我們一起來(lái)看看如何解決PCB板上三防漆相關(guān)異常現(xiàn)象及解決措施。

2022-06-23 09:22:39 4010

4010 通過(guò)PCB板本身散熱目前廣泛應(yīng)用的PCB板材是覆銅/環(huán)氧玻璃布基材或酚醛樹脂玻璃布基材,還有少量使用的紙基覆銅板材。

2022-09-30 14:40:22 736

736 近年來(lái)隨著自動(dòng)化進(jìn)程的推進(jìn),傳統(tǒng)的手工焊錫工藝被機(jī)器所取代,其中就包括手機(jī)內(nèi)部的精密電子零部件、天線等,通過(guò)錫膏激光焊錫機(jī)進(jìn)行焊接。

2022-04-29 16:48:08 425

425

使用PCB板三防漆時(shí),碰到最多的異常問(wèn)題有哪些呢?氣泡、針孔、發(fā)白、分層、橘皮、縮孔、裂紋……三分膠水、七分工藝,由于專業(yè)性不夠,使用前后就出現(xiàn)各種問(wèn)題,今天我們一起來(lái)看看如何解決PCB板上三防漆相關(guān)異常現(xiàn)象及解決方案措施。

2022-05-17 16:34:47 1911

1911

電鍍?nèi)兹?b class="flag-6" style="color: red">何解決PCB的信號(hào)、機(jī)械和環(huán)境問(wèn)題?

2024-02-27 14:15:44 82

82  電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論