在電子產(chǎn)品設(shè)計(jì)中,我們?cè)谧非?a target="_blank">產(chǎn)品功能以及成本的優(yōu)化時(shí),往往我們會(huì)忽略使用去耦的目的,僅僅知道在電路板上分散大小不同的許多電容,使較低阻抗電源連接到地。但問題依舊:需要多少電容?許多相關(guān)文獻(xiàn)表明,必須使用大小不同的許多電容來降低功率傳輸系統(tǒng)(PDS)的阻抗,但這并不完全正確。相反,僅需選擇正確大小和正確種類的電容就能降低PDS阻抗。

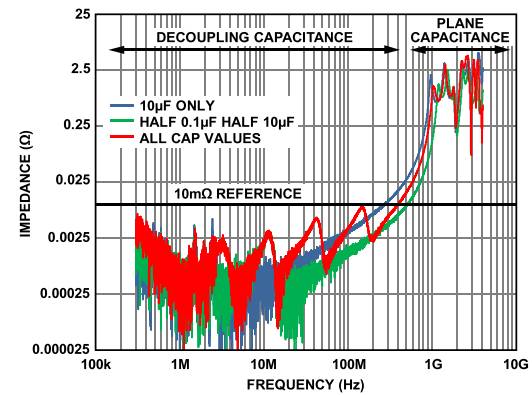

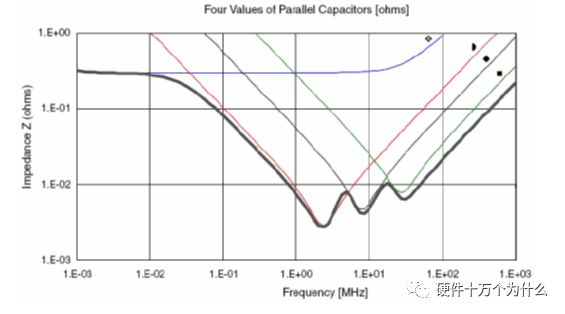

考慮設(shè)計(jì)一個(gè)10 mΩ參考層,如圖1所示。如紅色曲線所示,系統(tǒng)電路板上使用許多不同值的電容,0.001 μF、0.01 μF、0.1 μF等等。這當(dāng)然可以降低500 MHz頻率范圍內(nèi)的阻抗,但是,請(qǐng)看綠色曲線,同樣的設(shè)計(jì)僅使用0.1 μF和10 μF電容。這證明,如果使用正確的電容,則不需要如此多的電容。這也有助于節(jié)省空間和物料(BOM)成本。

圖1. 電容示例

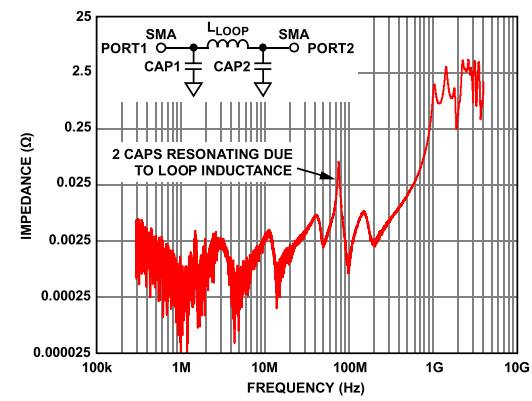

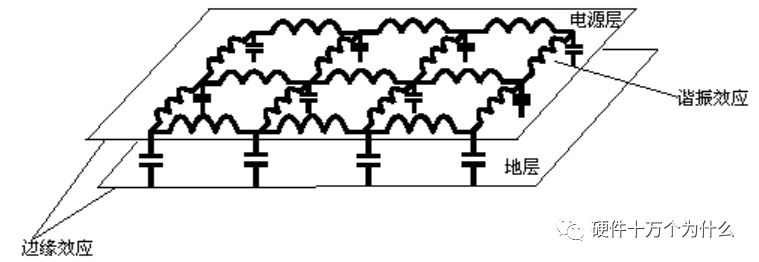

????注意,并非所有電容“生而平等”,即使同一供應(yīng)商,工藝、尺寸和樣式也有差別。如果未使用正確的電容,不論是多個(gè)電容還是幾個(gè)不同類型,都會(huì)給PDS帶來反作用。結(jié)果可能是形成電感環(huán)路。電容放置不當(dāng)或者使用不同工藝和型號(hào)的電容(因而對(duì)系統(tǒng)內(nèi)的頻率做出不同響應(yīng)),彼此之間可能會(huì)發(fā)生諧振,見圖2。

圖2. 諧振電容

所以,了解系統(tǒng)所用電容類型的頻率響應(yīng)很重要。隨便選用電容,會(huì)讓設(shè)計(jì)低阻抗PDS系統(tǒng)的努力付之東流。

如何設(shè)計(jì)出合格的PDS

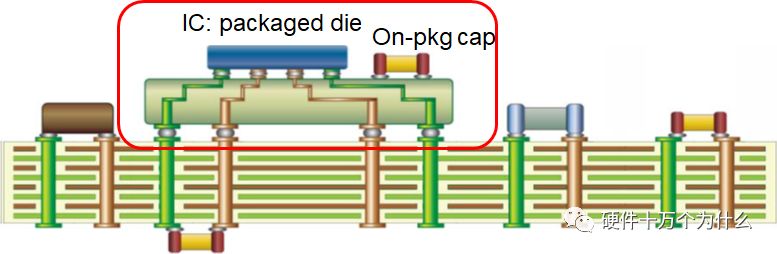

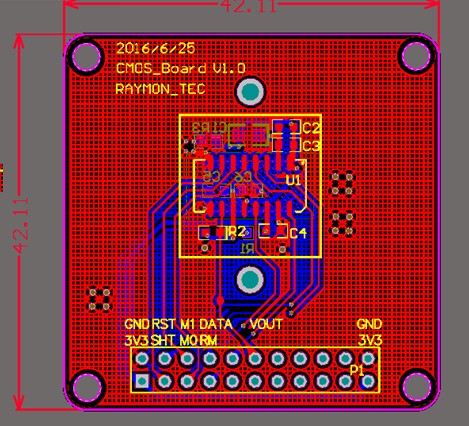

????要設(shè)計(jì)出合格的PDS,需要使用各種電容(見圖1)。PCB上使用的典型電容值只能將直流或接近直流頻率至約500 MHz范圍的阻抗降低。高于500 MHz頻率時(shí),電容取決于PCB形成的內(nèi)部電容。注意,電源層和接地層緊密疊置會(huì)有幫助。

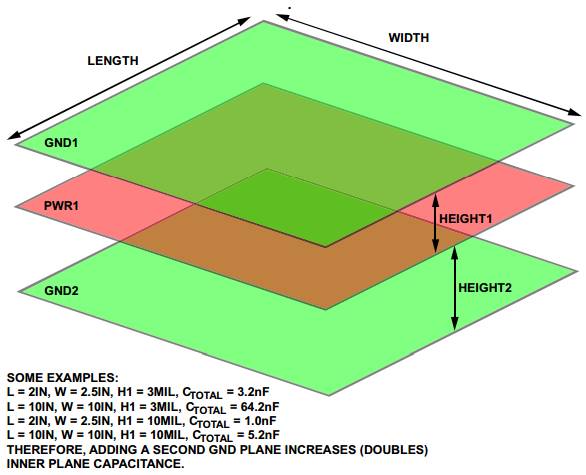

? ? 應(yīng)當(dāng)設(shè)計(jì)一個(gè)支持較大層電容的PCB層疊結(jié)構(gòu)。例如,六層堆疊可能包含頂部信號(hào)層、第一接地層、第一電源層、第二電源層、第二接地層和底部信號(hào)層。規(guī)定第一接地層和第一電源層在層疊結(jié)構(gòu)中彼此靠近,這兩層間距為2到4密爾,形成一個(gè)固有高頻層電容。此電容的最大優(yōu)點(diǎn)是它是免費(fèi)的,只需在PCB制造筆記中注明。如果必須分割電源層,同一層上有多個(gè)VDD電源軌,則應(yīng)使用盡可能大的電源層。不要留下空洞,同時(shí)應(yīng)注意敏感電路。這將使該VDD層的電容最大。

如果設(shè)計(jì)允許存在額外的層(上例中,從六層變?yōu)榘藢樱瑒t應(yīng)將兩個(gè)額外的接地層放在第一和第二電源層之間。在核心間距同樣為2到3密爾的情況下,此時(shí)層疊結(jié)構(gòu)的固有電容將加倍,示例見圖3。

圖3. 高頻層電容示例

與添加更多分立高頻電容以在高頻時(shí)保持低阻抗相比,此結(jié)構(gòu)更易于設(shè)計(jì)。

????PDS的任務(wù)是將響應(yīng)電源電流需求而產(chǎn)生的電壓紋波降至最低,這點(diǎn)很重要但常被忽略。所有電路都需要電流,有些電路需求量較大,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源層或接地層以及良好的PCB層疊,有助于將因電路的電流需求而產(chǎn)生的電壓紋波降至最低。例如,根據(jù)所用的去耦策略,如果系統(tǒng)設(shè)計(jì)的開關(guān)電流為1 A,PDS的阻抗為10 mΩ,則最大電壓紋波為10 mV。計(jì)算很簡單:V = IR。

憑借完美的PCB堆疊,可覆蓋高頻范圍,同時(shí)在電源層起始入口點(diǎn)和高功率或浪涌電流器件周圍使用傳統(tǒng)去耦,可覆蓋低頻范圍(<500 MHz)。這可確保PDS阻抗在整個(gè)頻率范圍內(nèi)均最低。沒有必要各處都配置電容;電容正對(duì)著每個(gè)IC放置會(huì)破壞許多制造規(guī)則。如果需要這種嚴(yán)厲的措施,則說明電路存在其它問題。Got it?

在高度集成的電子產(chǎn)品中,電源系統(tǒng)的設(shè)計(jì)占到了設(shè)計(jì)工作量的50%左右;對(duì)于復(fù)雜的FPGA類型的產(chǎn)品應(yīng)用,在電路中常常會(huì)達(dá)到15~30路不同的電源。

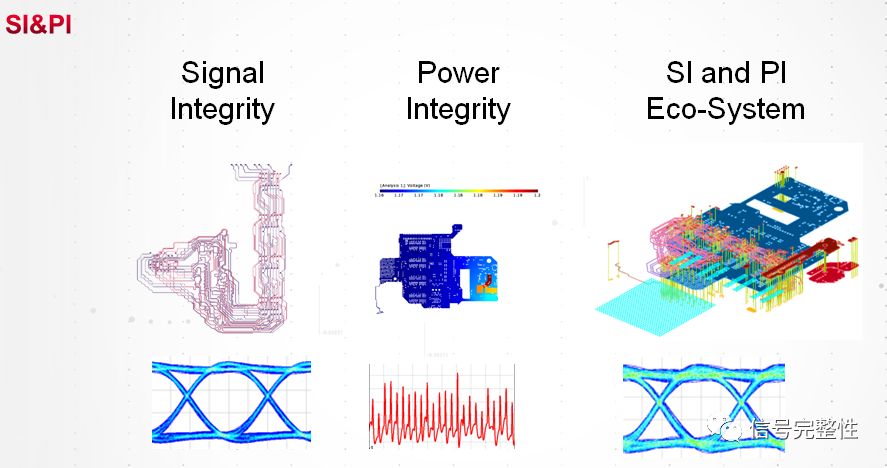

電源完整性的目的就是給系統(tǒng)提供持續(xù)、穩(wěn)定、干凈的電源,保證系統(tǒng)穩(wěn)定的工作。在數(shù)字系統(tǒng)中,使信號(hào)完整性滿足系統(tǒng)設(shè)計(jì)的要求也需要有一個(gè)非常穩(wěn)定的電源系統(tǒng),但是又不能使電源系統(tǒng)超標(biāo)。所以在設(shè)計(jì)電源完整性時(shí),不僅僅關(guān)注的是去耦電容,還需要關(guān)注電源完整性、信號(hào)完整性和電磁兼容性這個(gè)“生態(tài)系統(tǒng)”,尤其是要考慮高度集成化的數(shù)字電路對(duì)電源完整性的影響… …

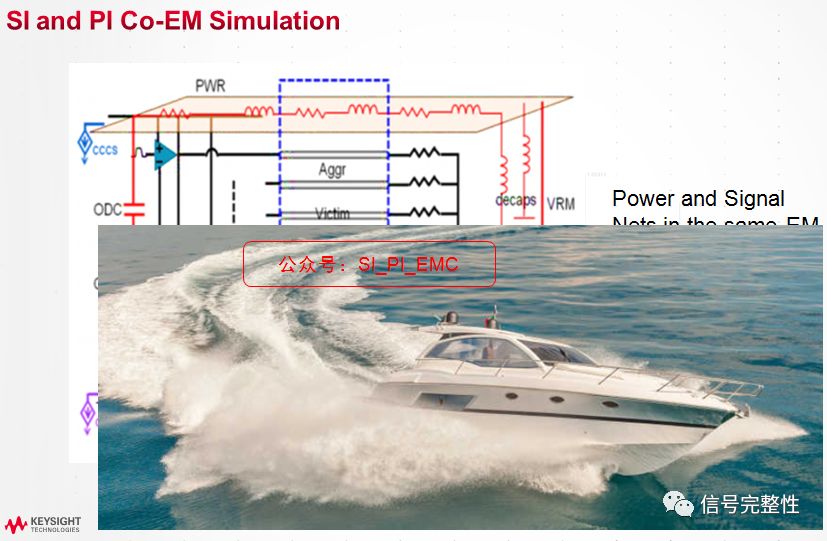

但是傳統(tǒng)分析信號(hào)完整性和電源完整性都是分開分析的,為了更好的分析SI和PI的相互影響,我們需要把SI和PI放在同一個(gè)EM仿真中來分析。

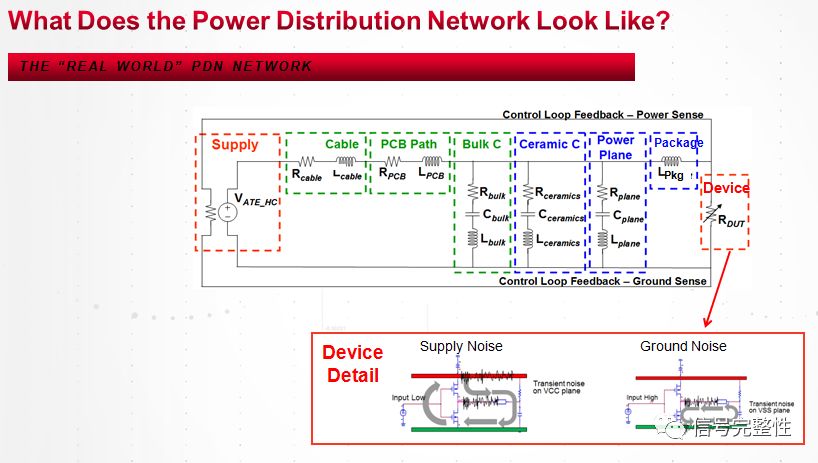

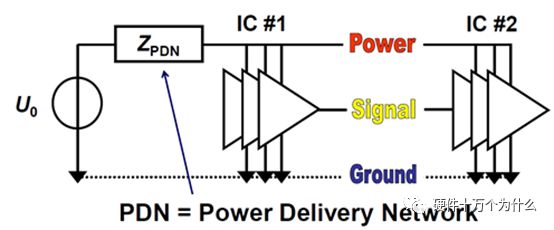

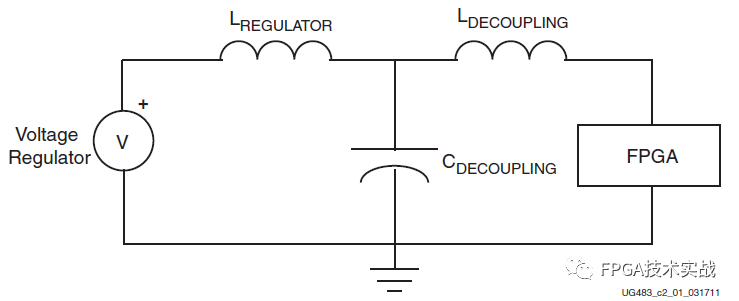

PDN

真實(shí)的PDN是什么樣子的呢?主要分為三個(gè)部分:供電端(VRM)、用電端(Sink)和傳輸通道(PCB、Cable、瓷片電容等等)。

電路板設(shè)計(jì)中,都有電源分配網(wǎng)絡(luò)系統(tǒng)。電源分配網(wǎng)絡(luò)系統(tǒng)的作用就是給系統(tǒng)內(nèi)所有器件或芯片提供足夠的電源,并滿足系統(tǒng)對(duì)電源穩(wěn)定性的要求。

我們看到電源、GND網(wǎng)絡(luò),其實(shí)分布著阻抗。

電源噪聲余量計(jì)算:

1、芯片的datasheet會(huì)給一個(gè)規(guī)范值,通常是5%;要考慮到穩(wěn)壓芯片直流輸出誤差,一般是+/_2.5%,因此電源噪聲峰值幅度不超過+/_2.5%。

2、如芯片的工作電壓范圍是3.13~3.47,穩(wěn)壓芯片標(biāo)出輸出電壓是3.3V,安裝在電路板后的輸出電壓是3.36V。容許的電壓的變化范圍是3.47-3.36=110mv。穩(wěn)壓芯片輸出精度是+/_1%,及3.36* +/_1%=+/_33.6mv。電源噪聲余量為110-33.6=76.4mv。

計(jì)算電源噪聲要注意五點(diǎn)

(1)穩(wěn)壓芯片的輸出的精確值是多少。

(2)工作環(huán)境的是否是穩(wěn)壓芯片所推薦的環(huán)境。

(3)負(fù)載情況是怎么樣,這對(duì)穩(wěn)壓芯片輸出也有影響。

(4)電源噪聲最終會(huì)影響到信號(hào)質(zhì)量。而信號(hào)上的噪聲來源不僅僅是電源噪聲,反射竄擾等信號(hào)完整性問題也會(huì)在信號(hào)上疊加,因此不能把所有噪聲余量留給電源系統(tǒng)。

(5)不同的電壓等級(jí)對(duì)電源噪聲要求也不樣,電壓越小噪聲余量越小。模擬電路對(duì)電源要求更高。

電源噪聲來源

(1)穩(wěn)壓芯片輸出的電壓不是恒定的,會(huì)有一定的紋波。

(2)穩(wěn)壓電源無法實(shí)時(shí)響應(yīng)負(fù)載對(duì)于電流需求的快速變化。穩(wěn)壓電源響應(yīng)的頻率一般在200Khz以內(nèi),能做正確的響應(yīng),超過了這個(gè)頻率則在電源的輸出短引腳處出現(xiàn)電壓跌落。

(3)負(fù)載瞬態(tài)電流在電源路徑阻抗和地路徑阻抗產(chǎn)生的壓降。

(4)外部的干擾。

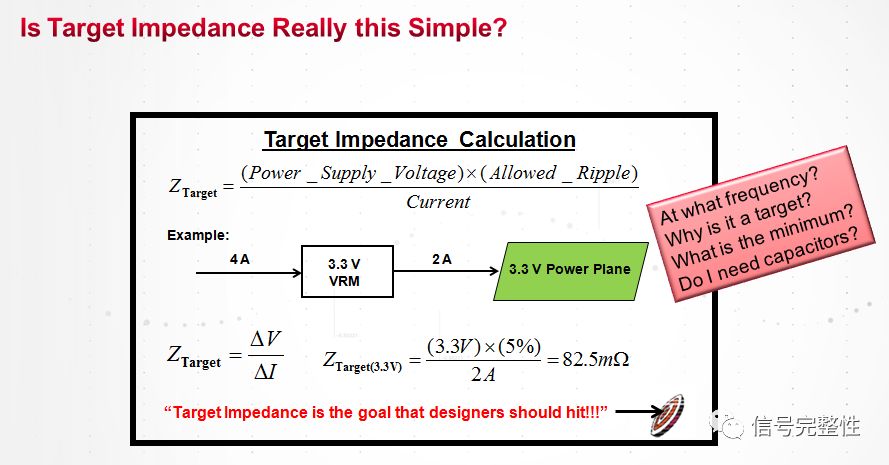

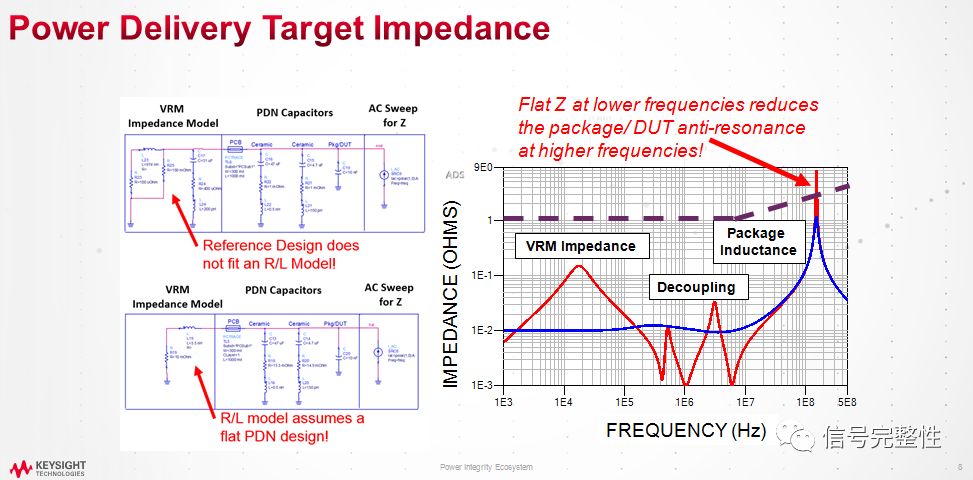

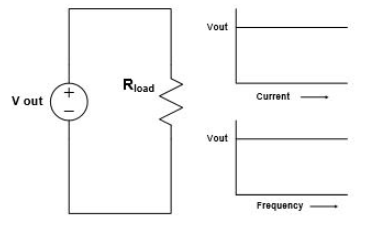

目標(biāo)阻抗

目標(biāo)阻抗是電源系統(tǒng)的瞬態(tài)阻抗,對(duì)快速變化的電流的表現(xiàn)出來的一種特性阻抗。目標(biāo)阻抗和一定寬度的頻率有關(guān),在感興趣的頻率范圍內(nèi),電源阻抗都不能超過這個(gè)值。

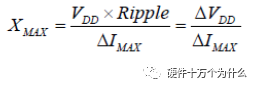

目標(biāo)阻抗公式

去耦的電源電壓,ripple為允許的電壓波動(dòng)范圍,典型值為2.5%,△Imax為負(fù)載芯片最大瞬態(tài)電流變化量。

在進(jìn)行電源完整性設(shè)計(jì)、分析和仿真的時(shí)候都會(huì)涉及到一個(gè)非常重要的概念,就是目標(biāo)阻抗?但是目標(biāo)阻抗真的是很多工程師認(rèn)為的那么簡單嗎?

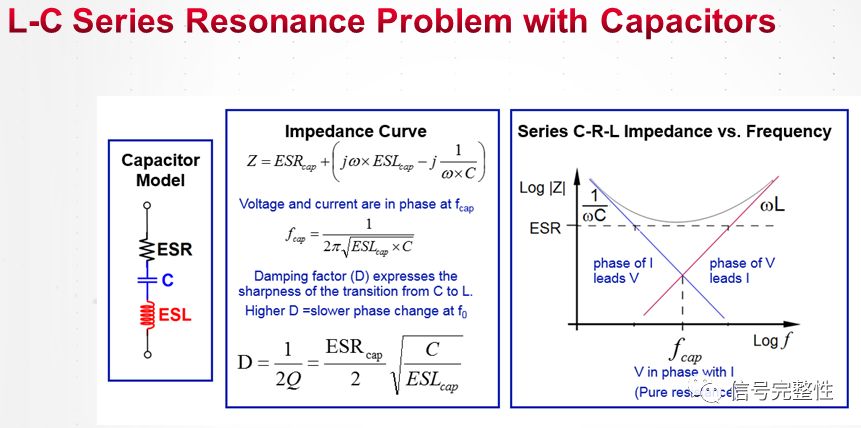

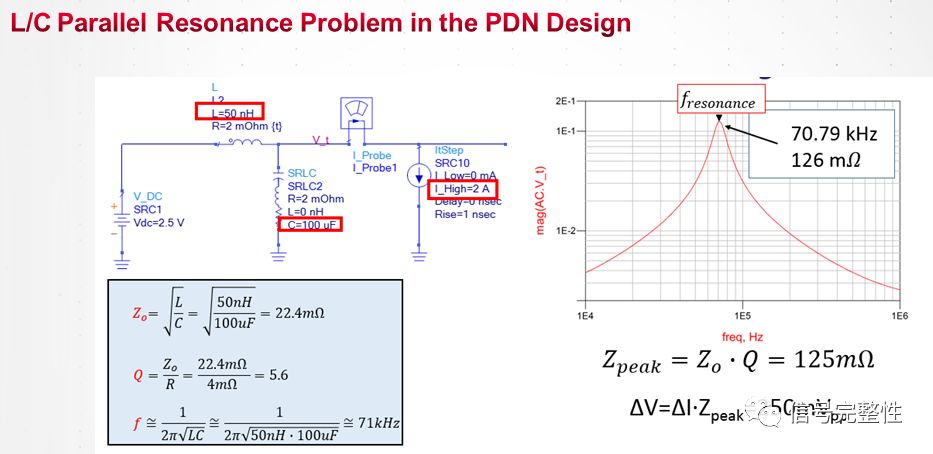

在真實(shí)的電源系統(tǒng)中,電容已經(jīng)不再是一個(gè)簡單的電容,而是包含了ESR、ESL的寄生參數(shù)。它們有串聯(lián)等效的作用,也有并聯(lián)等效的作用,呈現(xiàn)出來的結(jié)果都是不相同的。

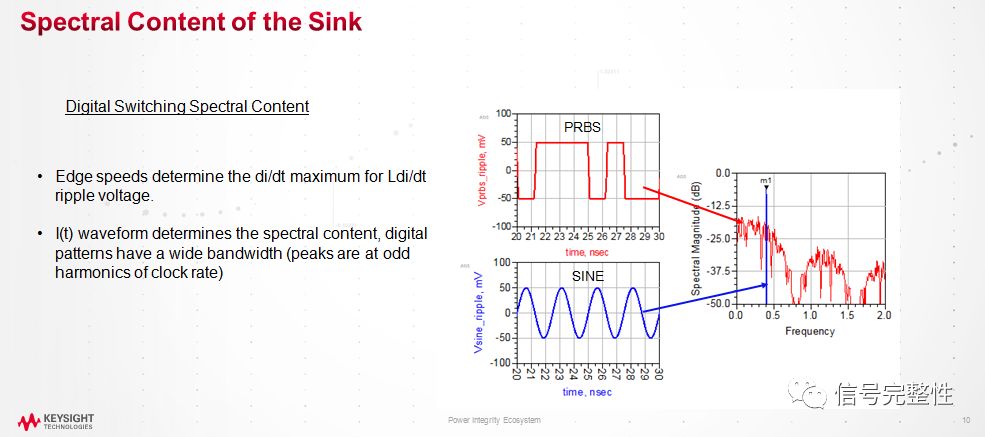

PDN阻抗隨著頻率而變化,不同的VRM也會(huì)導(dǎo)致阻抗曲線變化,好的VRM會(huì)使整條PDN阻抗曲線非常平滑。

信號(hào)的頻譜含量范圍很廣,并且隨著傳輸數(shù)據(jù)而不斷變化,在這種情況下,我們確實(shí)需要關(guān)注阻抗較高的頻率上的強(qiáng)制響應(yīng),確保這個(gè)響應(yīng)不要產(chǎn)生影響芯片與芯片之間通信的PDN噪聲。

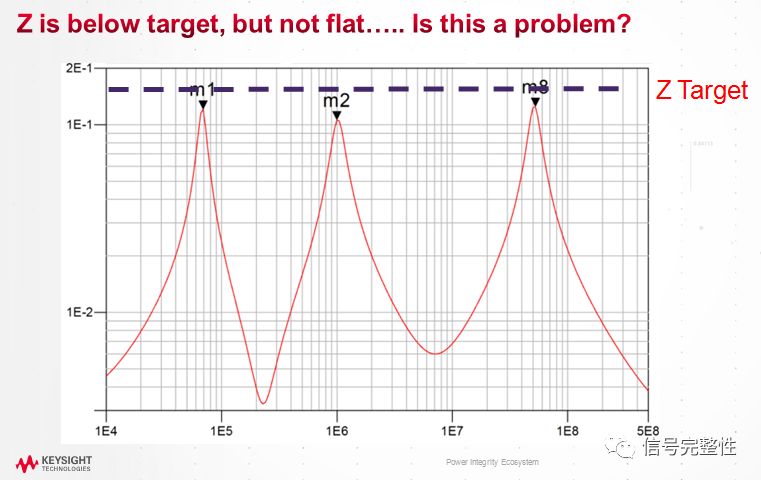

阻抗曲線都在目標(biāo)阻抗以下都沒問題了嗎?如果存在多個(gè)不超過目標(biāo)阻抗的巨大的反諧振點(diǎn)是否可以呢?

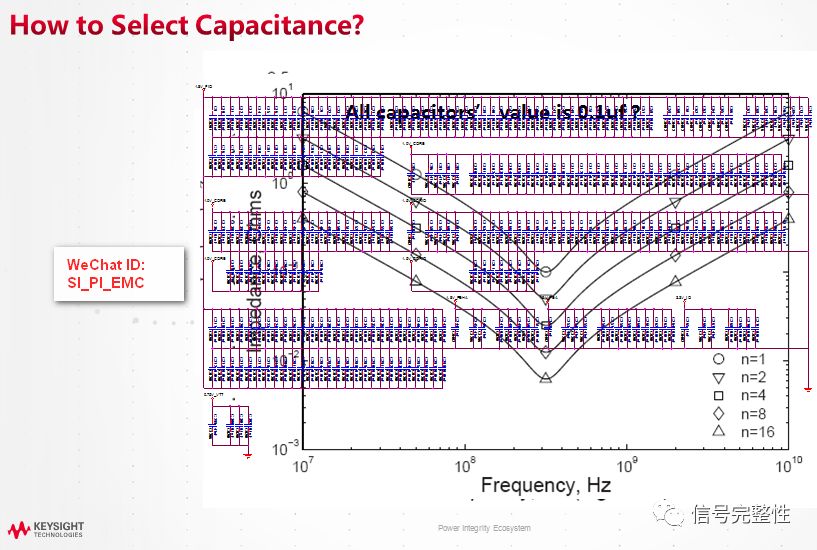

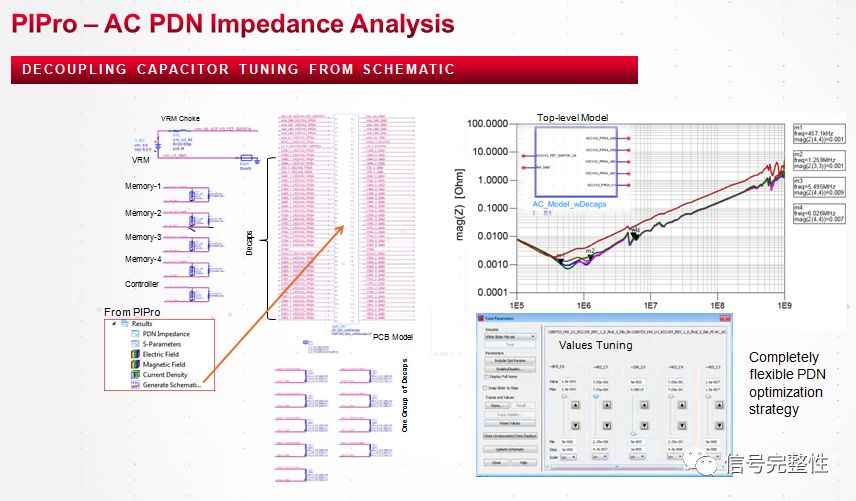

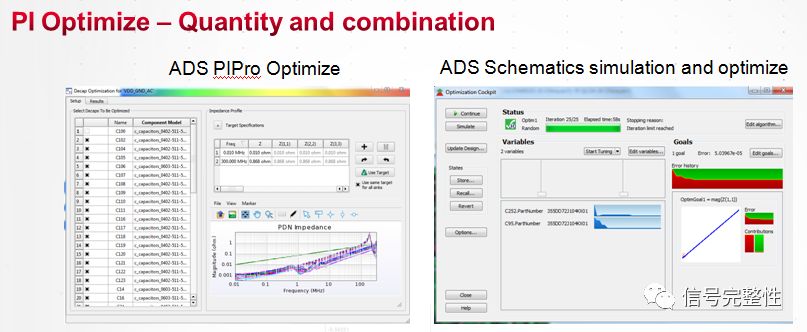

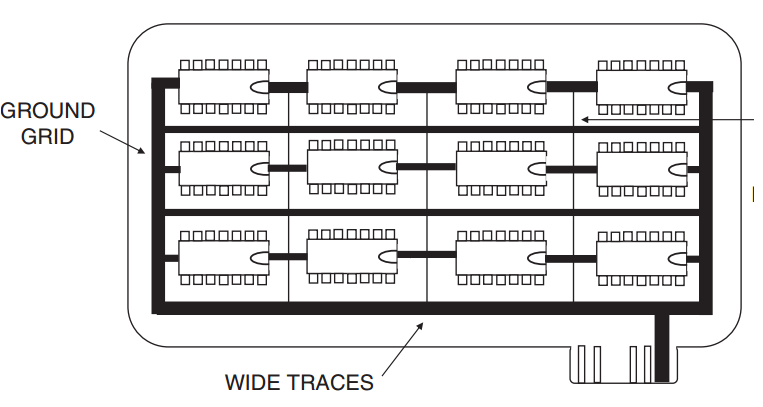

在電路設(shè)計(jì)時(shí),通常會(huì)在電路板上放置非常多的電容,那這些電容如何選型?如何搭配?如何放置?這是每一位工程師都會(huì)遇到的情況。

選擇電容

用一個(gè)電容組合的例子。這個(gè)組合使用的電容為:2個(gè)680uf鉭電容,7個(gè)2.2uf陶瓷電容(0805封裝),13個(gè)0.22uf陶瓷電容(0603封裝),26個(gè)0.022uf陶瓷電容(0402)。圖中上部平坦的曲線是680uf電容的阻抗曲線,其它三個(gè)容值的曲線為為圖中三個(gè)V字曲線,從左到右2.2uf →0.22uf → 0.022uf。總的阻抗曲線為底部粗包路線。

這個(gè)組合實(shí)現(xiàn)了在500K到150M范圍內(nèi)保持阻抗在33毫歐以下,到500M處,阻抗上升到110毫歐,從圖中看反諧振點(diǎn)控制的很低。

實(shí)際案例

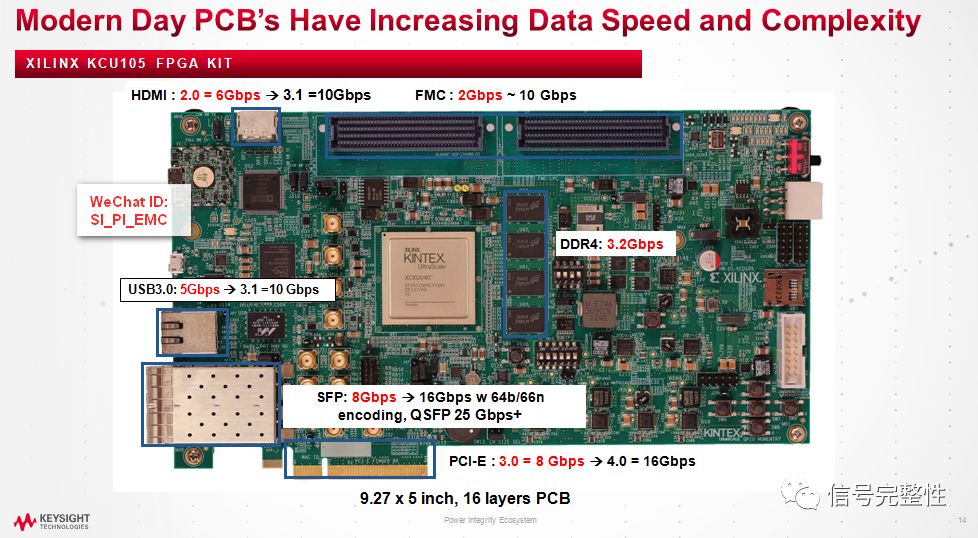

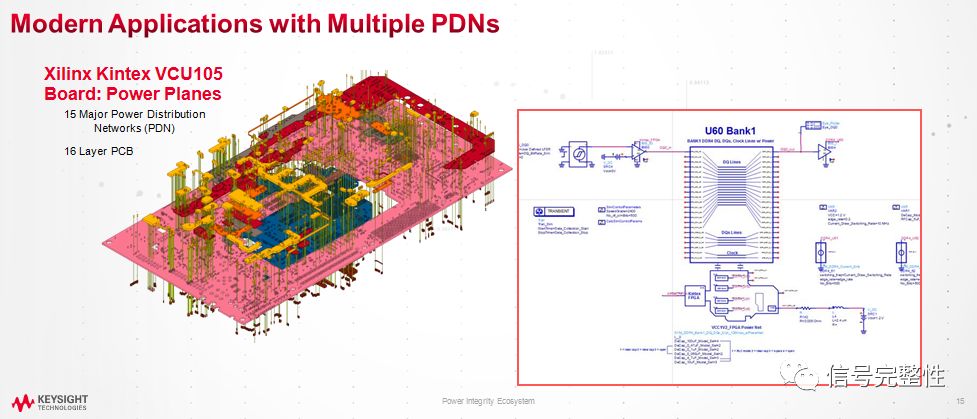

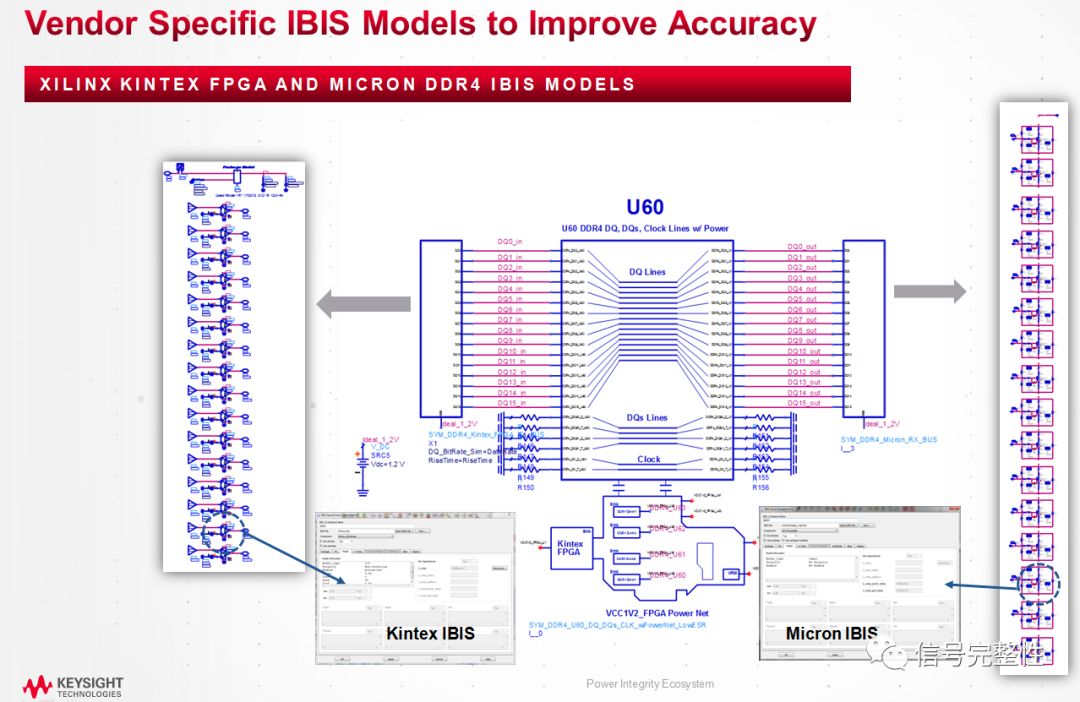

這是一個(gè)實(shí)際的案例,PCB是Xilinx的Demo板,包含了4pcs DDR4顆粒,速率達(dá)到3.2Gbps,同時(shí)還包含了很多SerDes總線,如USB,SFP+和PCIE等等。有15路主要的電源,與各類數(shù)字信號(hào)交織在一塊16層的PCB板上。

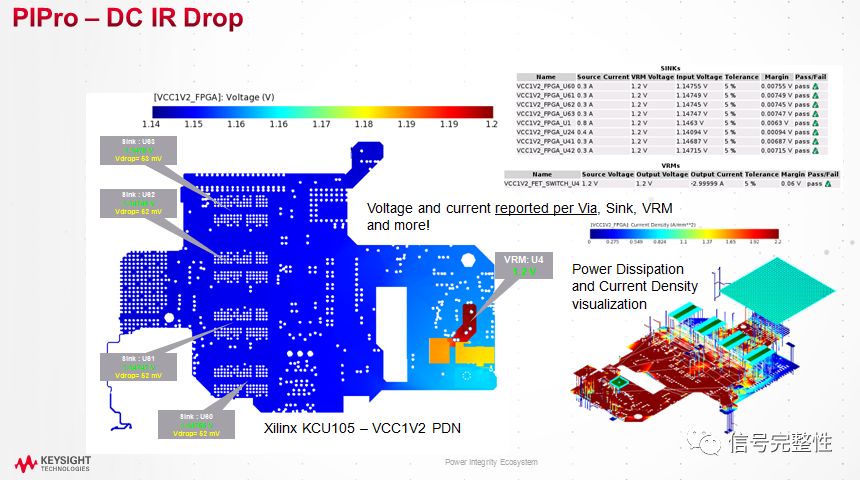

對(duì)于這么復(fù)雜的PCB設(shè)計(jì),如何開始EM仿真呢?最好的方式就是在直流狀態(tài)下進(jìn)行IR Drop的仿真,這個(gè)很容易理解。使用ADS PIPro就可以完成這個(gè)工作。

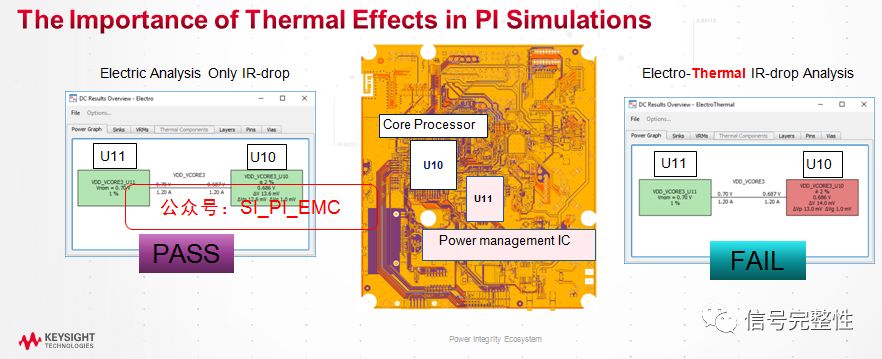

溫度也會(huì)造成電源系統(tǒng)的不確定性,使用PIPro可以進(jìn)行電源系統(tǒng)的電熱聯(lián)合仿真。下圖表示的就是電源系統(tǒng)是否考慮溫度的影響,這樣導(dǎo)致的結(jié)果是不相同的。

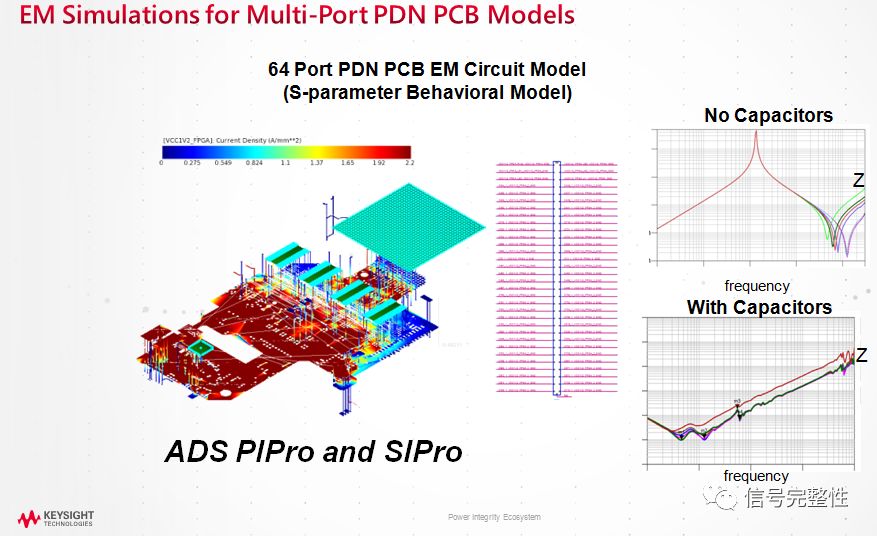

使用PIPro可以提取PDN的S參數(shù),同時(shí)仿真PDN的阻抗曲線。

其實(shí)信號(hào)與電源的關(guān)系就像一艘快艇行駛在海面上,相互之間都是有影響的。為了捕獲SI和PI的所有的影響,可以把SI和PI放在同一個(gè)EM仿真中同時(shí)來仿真以獲取一個(gè)完整的S參數(shù)。

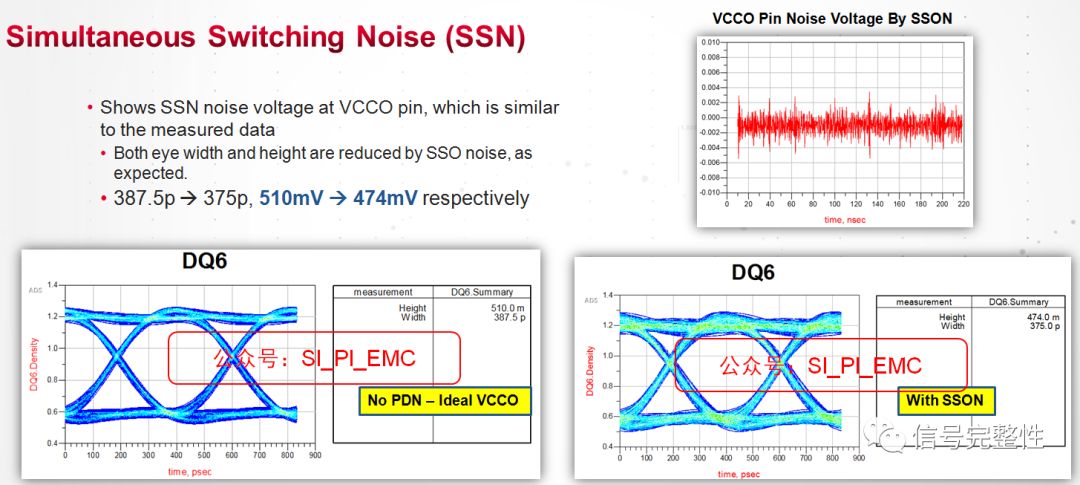

SSN仿真是一直以來SI/PI協(xié)同仿真的重點(diǎn),下面是一個(gè)SSN仿真的案例:

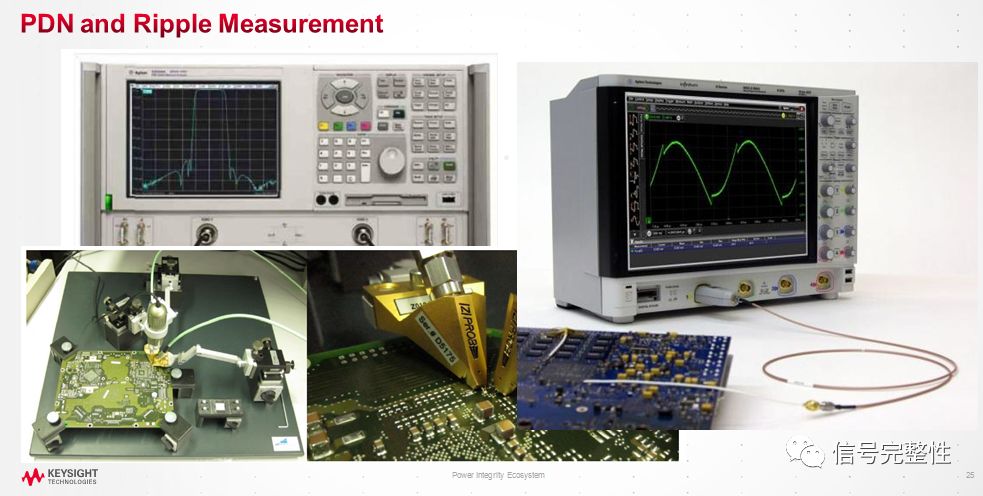

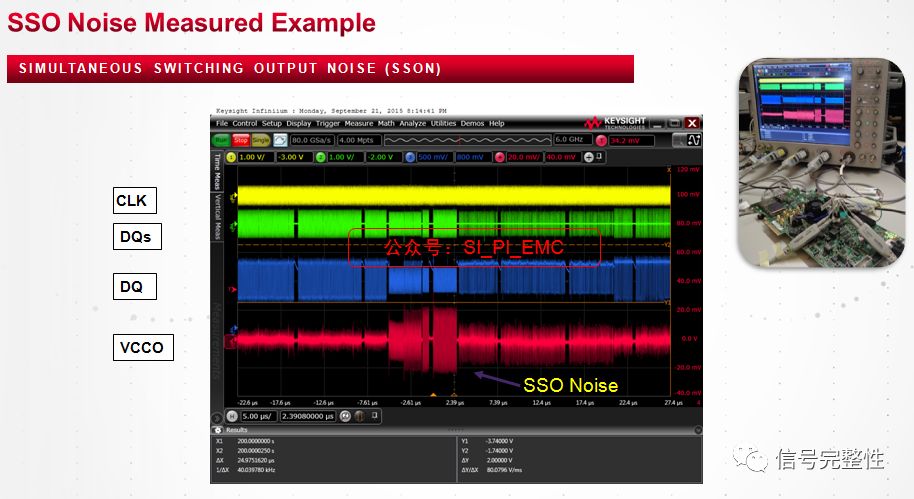

PDN的測(cè)量主要有時(shí)域測(cè)量和頻域測(cè)量之分,下面是關(guān)于SSN噪聲測(cè)量的案例:

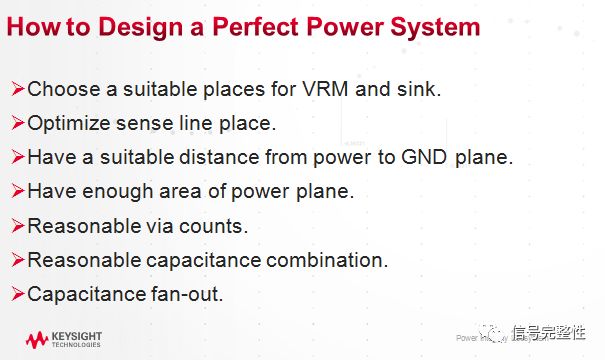

如何設(shè)計(jì)一個(gè)好的電源系統(tǒng),這是有一些可以遵循的方法的:

編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論