下面從直角走線、差分走線、蛇形線三個(gè)方面來闡述PCB LAYOUT的走線。

2021-03-17 07:25:46

本帖最后由 maskmyself 于 2017-7-10 10:08 編輯

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速

2017-07-07 11:45:56

PCB Layout中的走線策略

2012-08-04 16:32:25

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中

2014-08-13 15:44:05

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中

2019-08-05 06:40:24

新人,求PCB布局走線資料,謝謝!

2014-08-02 19:19:40

PCB中走線有幾種這幾種分別有什么作用?哪種對(duì)信號(hào)的影響最好?

2012-11-13 15:49:21

我們通常需要快速地估計(jì)出印刷電路板上一根走線或一個(gè)平面的電阻值,而不是進(jìn)行冗繁的計(jì)算。雖然現(xiàn)在已有可用的印刷電路板布局與信號(hào)完整性計(jì)算程序,可以精確地計(jì)算出走線的電阻,但在設(shè)計(jì)過程中,我們有時(shí)候還是希望采取快速粗略的估計(jì)方式。

2019-09-11 11:52:28

pcb走線時(shí),會(huì)影響到已經(jīng)布完的線。之前正在布的線不會(huì)對(duì)已經(jīng)布完的線產(chǎn)生影響,現(xiàn)在不知道怎么恢復(fù)。

2019-09-25 03:58:46

PCB走線寬度、電流關(guān)系計(jì)算工具:PCB走線寬度、電流關(guān)系計(jì)算工具.zip (850.77 KB )

2019-10-09 01:16:38

1. 一般規(guī)則 1.1 PCB板上預(yù)劃分?jǐn)?shù)字、模擬、DAA信號(hào)布線區(qū)域。 1.2 數(shù)字、模擬元器件及相應(yīng)走線盡量分開并放置於各自的布線區(qū)域內(nèi)。 1.3 高速數(shù)字信號(hào)走線盡量短。 1.4

2018-11-28 17:06:35

PCB走線電流計(jì)算工具

2021-03-12 13:36:29

好的圖像質(zhì)量的保證。 PCB走線如果可能的話,信號(hào)走線使用6mil, 走線間距使用6mil. 放置0.1uF的退耦電容在對(duì)應(yīng)的DSP電源腳上,并盡可能的靠近。它的走線盡可能的粗。電源正極的走線最少要

2023-04-13 16:09:54

求高手貢獻(xiàn)PCB設(shè)計(jì)走線經(jīng)驗(yàn)!及相關(guān)技術(shù)

2013-01-11 20:02:07

1.PCB走線線寬的重要性 PCB載流能力的計(jì)算一直缺乏權(quán)威的技術(shù)方法、公式,經(jīng)驗(yàn)豐富CAD工程師依靠個(gè)人經(jīng)驗(yàn)?zāi)茏鞒鲚^準(zhǔn)確的判斷。但是對(duì)于CAD新手,不可謂遇上一道難題。 對(duì)于大電流電源走線

2023-04-12 16:02:23

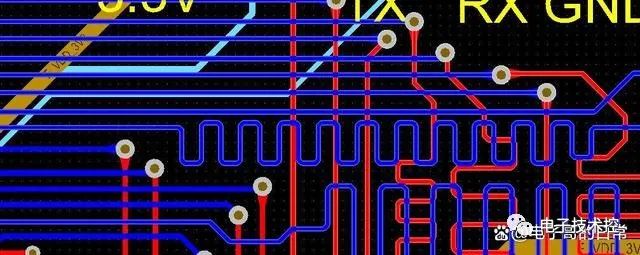

`為什么下圖中PCB走線正反面不同。孔與孔之間為直接通路。為什么背面的走線環(huán)繞迂回。小白菜提問,求高手詳解。謝謝`

2018-10-29 08:46:46

經(jīng)驗(yàn)公式來計(jì)算: C=61W(Er)1/2/Z0 在上式中,C就是指拐角的等效電容(單位:pF),W指走線的寬度(單位:inch),εr指介質(zhì)的介電常數(shù),Z0就是傳輸線的特征阻抗。舉個(gè)例子,對(duì)于一個(gè)

2014-11-18 17:29:31

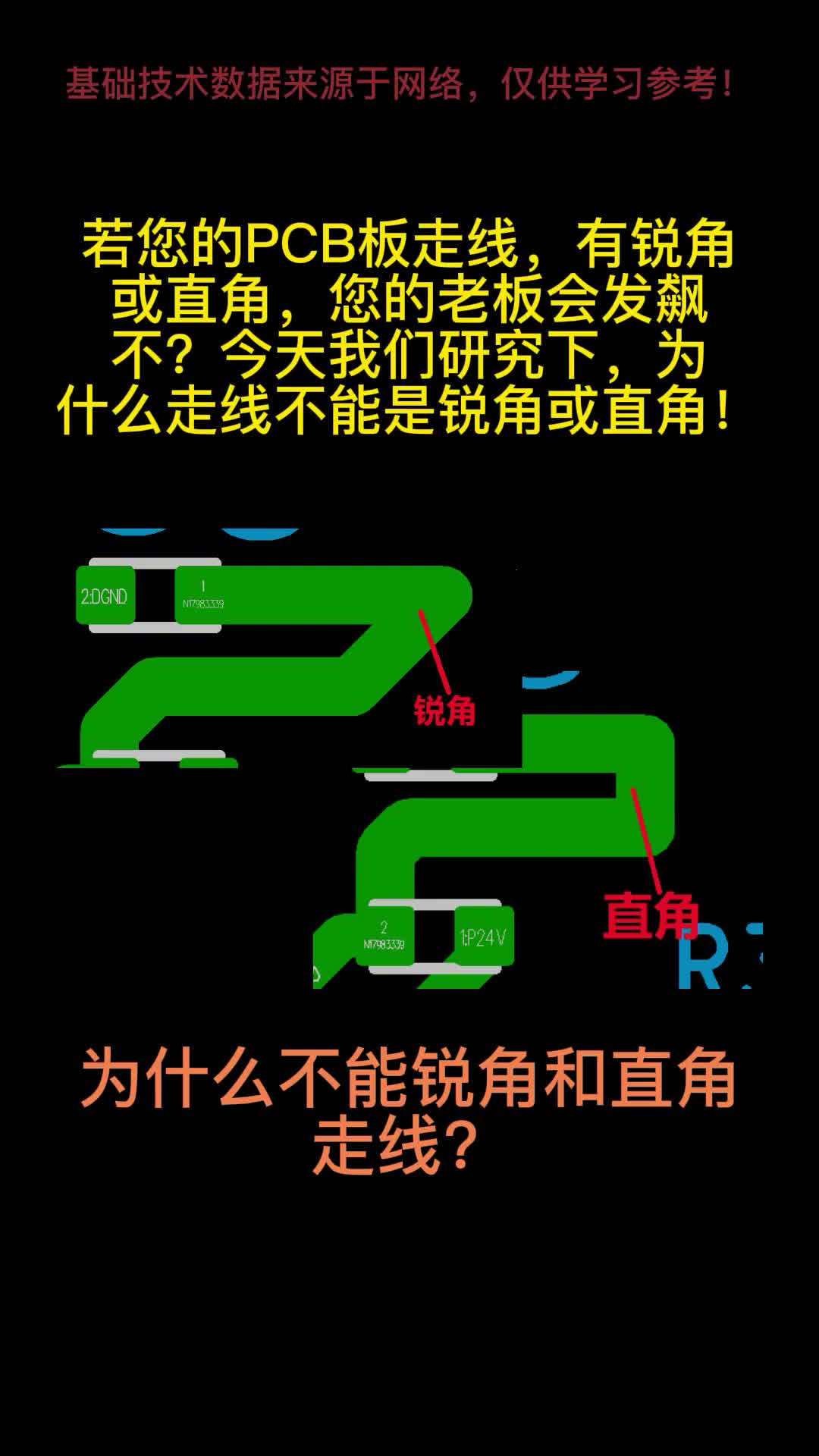

采訪過蘋果公司CEO的B站up主-何同學(xué),近期更新一條視頻中,有出現(xiàn)過他自己設(shè)計(jì)的PCB圖。很多人說他不應(yīng)該直角走線。PCB為什么不能直角走線呢?一般在高速信號(hào)線中,直角線會(huì)帶來阻抗的不均勻

2022-09-08 16:54:17

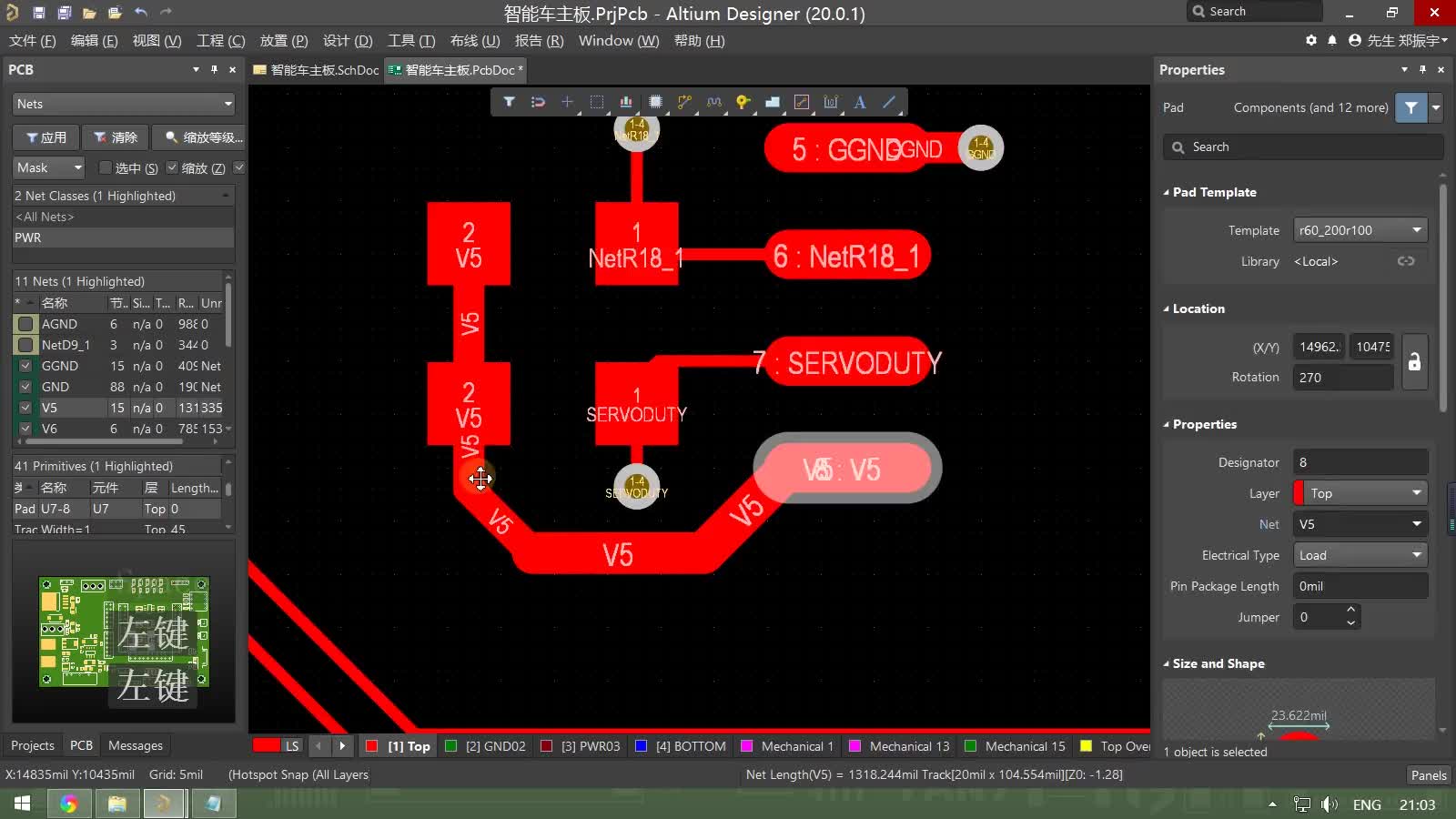

`用altium 畫PCB 對(duì)稱電路時(shí)走線沒有走對(duì)稱,看起來有點(diǎn)別扭。像這種對(duì)稱電路走線一般要怎么處理比較好呢?像我這樣畫對(duì)電器想能有沒有什么影響?要怎么畫才比較合理?希望大家指點(diǎn)指點(diǎn)`

2017-01-07 11:20:13

對(duì)角線之間的距離為78.74mil(4)計(jì)算線寬、間隙及過孔。若兩個(gè)焊盤之間走一條線,兩個(gè)焊盤之間平行布線區(qū)域?yàn)?9.2910mil,考慮到余量計(jì)算采用17.2910mil進(jìn)行。若線寬5mil,間隙

2020-07-06 15:58:12

經(jīng)常聽說“PCB走線間距大于等于3倍線寬時(shí)可以抑制70%的信號(hào)間干擾”,這就是3W原則,信號(hào)線之間的干擾被稱為串?dāng)_。那么,你知道串?dāng)_是怎么形成的嗎?當(dāng)兩條走線很近時(shí),一條信號(hào)線上的信號(hào)可能會(huì)在另一

2022-12-27 20:33:40

在pcb的設(shè)計(jì)過程中,元器件的布局和走線的調(diào)整是非常重要的一個(gè)步驟。恰當(dāng)?shù)牟季挚梢院?jiǎn)化布線的難度,更重要的是可以提高PCB的電氣性能,減少EMC,EMI。 下面是同一個(gè)原理圖對(duì)應(yīng)的兩種不同的布局和走

2019-10-17 04:37:54

PCB上的任何一條走線在通過高頻信號(hào)的情況下都會(huì)對(duì)該信號(hào)造成時(shí)延時(shí),蛇形走線的主要作用是補(bǔ)償“同一組相關(guān)"信號(hào)線中延時(shí)較小的部分,這些部分通常是沒有或比其它信號(hào)少通過另外的邏輯處理;最典型的就是時(shí)鐘

2017-11-22 20:04:14

PCB上的任何一條走線在通過高頻信號(hào)的情況下都會(huì)對(duì)該信號(hào)造成時(shí)延時(shí),蛇形走線的主要作用是補(bǔ)償“同一組相關(guān)”信號(hào)線中延時(shí)較小的部分,這些部分通常是沒有或比其它信號(hào)少通過另外的邏輯處理;最典型的就是

2018-08-30 10:14:44

PCB上的任何一條走線在通過高頻信號(hào)的情況下都會(huì)對(duì)該信號(hào)造成時(shí)延時(shí),蛇形走線的主要作用是補(bǔ)償“同一組相關(guān)”信號(hào)線中延時(shí)較小的部分,這些部分通常是沒有或比其它信號(hào)少通過另外的邏輯處理;最典型的就是

2020-07-14 18:02:17

PCB上的任何一條走線在通過高頻信號(hào)的情況下都會(huì)對(duì)該信號(hào)造成時(shí)延時(shí),蛇形走線的主要作用是補(bǔ)償“同一組相關(guān)"信號(hào)線中延時(shí)較小的部分,這些部分通常是沒有或比其它信號(hào)少通過另外的邏輯處?;最典型的就是

2018-09-20 11:05:23

PCB電容引腳之間可以走線嗎?

2023-04-13 16:25:48

直角走線一般是pcb布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標(biāo)準(zhǔn)之一,那么直角走線究竟會(huì)對(duì)信號(hào)傳輸產(chǎn)生多大的影響呢?從原理上說,直角走線會(huì)使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)。其實(shí)

2014-10-28 15:08:55

1.1 PCB板上預(yù)劃分?jǐn)?shù)字、模擬、DAA信號(hào)布線區(qū)域。1.2 數(shù)字、模擬元器件及相應(yīng)走線盡量分開并放置於各自的布線區(qū)域內(nèi)。1.3 高速數(shù)字信號(hào)走線盡量短。1.4 敏感模擬信號(hào)走線盡量短。1.5

2019-05-30 06:58:19

PCB設(shè)計(jì)走線的寬度與最大允許電流有何關(guān)系?PCB設(shè)計(jì)走線的寬度與銅厚有何關(guān)系?

2021-10-11 09:49:14

PCB設(shè)計(jì)走線的規(guī)則是什么

2021-03-17 06:36:28

在高頻電路中的數(shù)據(jù)線。沒有計(jì)算蛇形線電感量的公式或經(jīng)驗(yàn)值? 、specctra可以編程設(shè)定網(wǎng)絡(luò)走線的阻抗匹配規(guī)則和差分線走線規(guī)則, 幫助里面講了一些一般的設(shè)計(jì)原則,有時(shí)也兼作電阻作用。 實(shí)際是一個(gè)分布

2014-11-19 11:54:01

PCB能不能以銳角走線pcb layout能不能以90°走線

2021-02-26 08:14:21

1. 一般規(guī)則1.1 PCB板上預(yù)劃分?jǐn)?shù)字、模擬、DAA信號(hào)布線區(qū)域。1.2 數(shù)字、模擬元器件及相應(yīng)走線盡量分開并放置於各自的布線區(qū)域內(nèi)。1.3 高速數(shù)字信號(hào)走線盡量短。1.4 敏感模擬信號(hào)走線盡量

2014-03-14 17:44:44

pcb走線為什么直接連不到芯片引腳上呢?

2023-04-10 16:29:30

pcb走線線寬和電流的關(guān)系

2012-07-16 16:48:57

pcb布局,走線方面,有什么建議嗎,該怎么怎么走,怎么提高效率

2016-10-15 14:51:34

;=2倍的線寬。PCI板上的蛇行線就是為了適應(yīng)PCI 33MHzClock的線長(zhǎng)要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等

2019-05-22 02:48:05

`請(qǐng)問各路大神,從電阻內(nèi)部走線會(huì)有什么影響?高頻情況下有壞的影響?如果有影響的話,請(qǐng)?jiān)敿?xì)、具體解釋下。`

2015-11-06 15:38:25

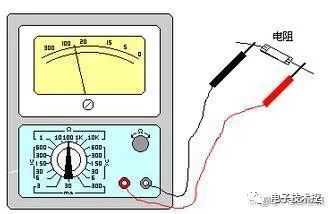

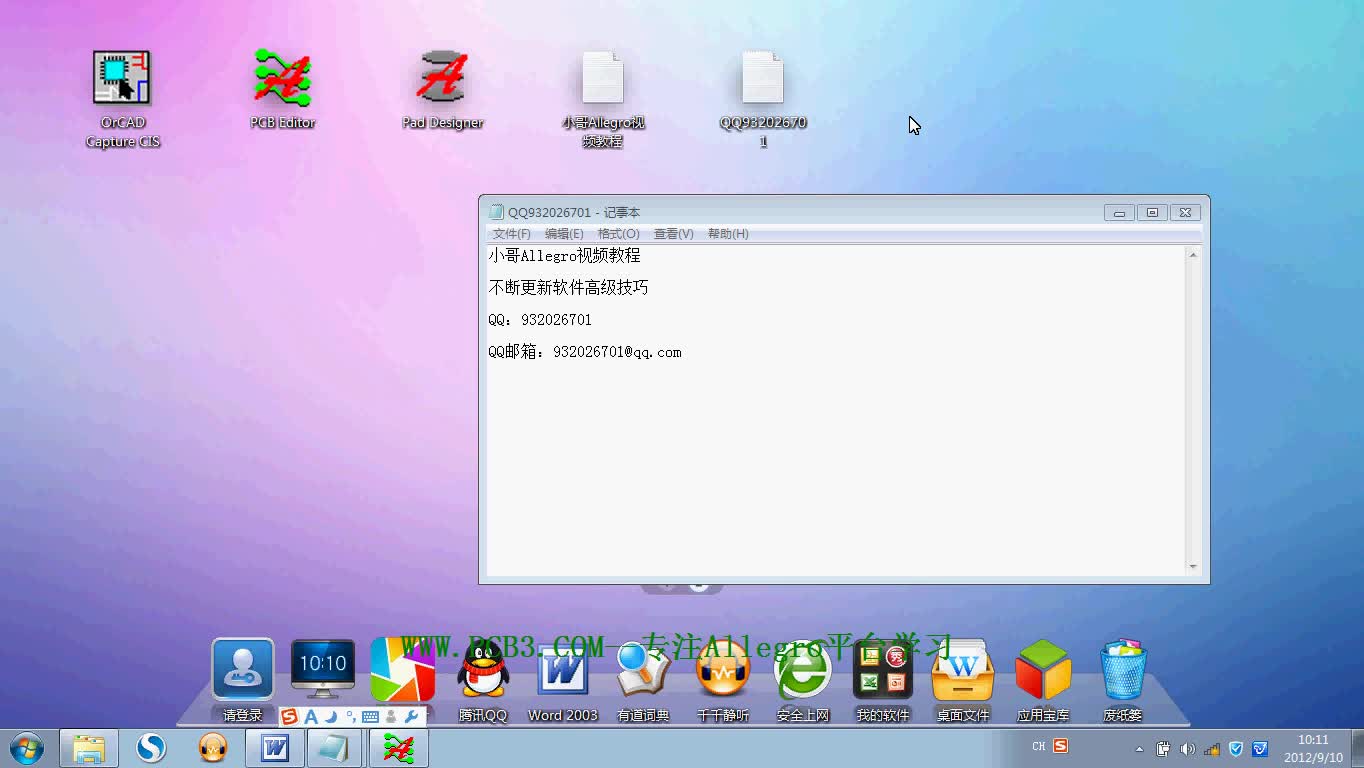

請(qǐng)問大神,用這個(gè)打開PCB工程文件的時(shí)候鼠標(biāo)所指的同一網(wǎng)絡(luò)的走線不會(huì)高亮顯示,這要怎么解決?

2017-08-27 10:42:29

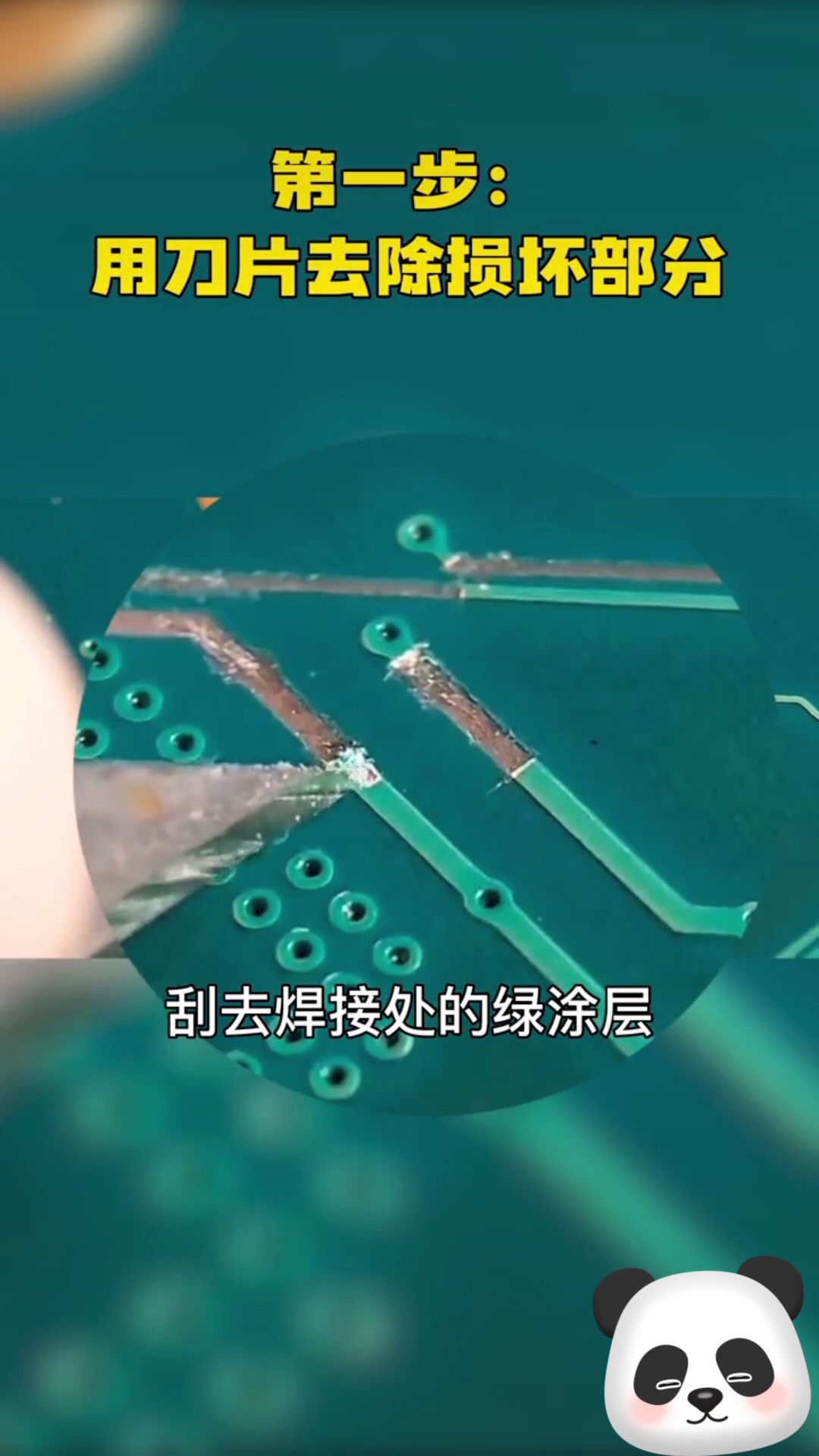

PCB設(shè)計(jì)時(shí),有時(shí)候需要在不增加PCB走線寬度的情況下提高該走線通過大電流的能力(載流能力),通常的方法是給該導(dǎo)線鍍錫(或者上錫);下面以在PCB頂層走線鍍錫為例,使用AD09軟件,簡(jiǎn)單介紹如何走線上錫處理:1、?選擇TopLayer層,確定需要走線的地方,畫一條導(dǎo)線;(圖文詳解見附件)

2019-09-06 15:57:30

PCB設(shè)計(jì):通常的BGA器件如何走線?

2021-02-26 06:13:16

PCB Layout中的走線策略布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見

2009-08-20 20:58:49

是至關(guān)重要的。下面將針對(duì)實(shí)際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。主要從直角走線,差分走線,蛇形線等三個(gè)方面來闡述。01直角走線直角走線一般是PCB布線中要求盡量避免

2018-07-08 13:28:36

cadence PCB 怎么取消走線?***用過,取消很容易,cadence沒發(fā)現(xiàn)這個(gè)功能!

2016-01-25 22:57:46

很多人對(duì)于PCB走線的參考平面感到迷惑,經(jīng)常有人問:對(duì)于內(nèi)層走線,如果走線一側(cè)是VCC,另一側(cè)是GND,那么哪個(gè)是參考平面?要弄清楚這個(gè)問題,必須對(duì)了解傳輸線的概念。我們知道,必須使用傳輸線來分析

2014-11-17 10:07:29

會(huì)說:PCB走線怎么會(huì)那么奇形怪狀?但是往往需要計(jì)算走線電阻的是電源信號(hào),電源信號(hào)有時(shí)通過覆銅實(shí)現(xiàn),形成一些不規(guī)則形狀。總結(jié)如下:●六個(gè)為1的全正方形=6個(gè)等效方塊;兩個(gè)為0.14的連接器方塊

2019-09-14 07:00:00

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中

2019-03-18 21:38:12

為什么PCB走線中不能出現(xiàn)銳角和直角?而且走線也不能和IC的PIN腳垂直?會(huì)影響到什么?

2023-04-11 16:31:28

是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標(biāo)準(zhǔn)之一,那么直角走線究竟會(huì)對(duì)信號(hào)傳輸產(chǎn)生多大的影響呢?從原理上說,銳角、直角走線會(huì)使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)。線寬變化導(dǎo)致阻抗

2017-08-12 15:09:54

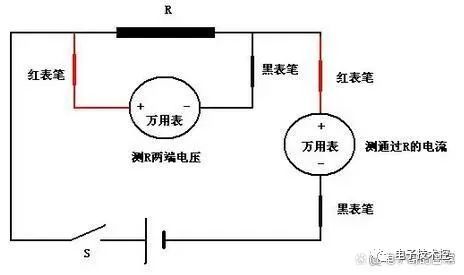

如何計(jì)算pcb走線上的電流大小?我電路板上的走線的特性阻抗為50,加了個(gè)33的限流電阻,芯片采用的3.3V電壓,則走線的電路為3.3/(50+33) A嗎?

2014-11-07 09:50:36

如何利用PCB走線設(shè)計(jì)一個(gè)0.05歐姆的采樣電阻?

2021-02-03 07:10:52

AD里PCB多根走線時(shí)怎么改變線寬

2019-09-12 04:20:46

如何在altium designer 的PCB圖里畫出 粗細(xì)漸變的走線

2019-09-04 04:21:32

我們通常需要快速地估計(jì)出印刷電路板上一根走線或一個(gè)平面的電阻值,而不是進(jìn)行冗繁的計(jì)算。雖然現(xiàn)在已有可用的印刷電路板布局與信號(hào)完整性計(jì)算程序,可以精確地計(jì)算出走線的電阻,但在設(shè)計(jì)過程中,我們有時(shí)候還是

2015-03-10 10:12:14

射頻線PCB走線屏蔽孔,都有什么要求???求解

2016-01-13 14:40:40

做設(shè)計(jì)的都明白一個(gè)事情,很多時(shí)候需要的是一個(gè)估算值,印刷電路板也一樣,通常需要很快的估算出PCB走線電阻的阻值,繞過那些繁雜的計(jì)算。本文就借著一個(gè)復(fù)雜的例子介紹一種快速估算出PCB走線電阻的方法

2019-05-26 08:30:00

PCB上面用更細(xì)的走線做保險(xiǎn)有什么具體的公式算法,我有兩種電流規(guī)格,一種是2A的持續(xù)電流,一種是0.1A的持續(xù)電流,如果用表層走線做保險(xiǎn)絲,要用多寬的走線,銅厚1OZ

2019-08-21 21:45:15

怎樣計(jì)算PCB布線中走線允許的最大長(zhǎng)度?走線太長(zhǎng)了都有哪些影響呢?

2023-04-10 17:10:25

寬,距電源/地越近,或隔離層的介電常數(shù)越高,特征阻抗就越小。 11、PCB板上的走線可等效為串聯(lián)和并聯(lián)的電容、電阻和電感結(jié)構(gòu)。串聯(lián)電阻的典型值0.25-0.55 ohms/英尺。并聯(lián)電阻阻值通常很高

2014-12-16 09:47:09

如何控制PCB走線的直流電阻?

2019-07-19 14:32:04

電源布局、網(wǎng)口電路、音頻走線的PCB設(shè)計(jì)

2021-03-04 06:10:24

Ω。 因此,從A到B的總電阻為3.98mΩ(3mΩ+0.14mΩ+0.84mΩ)。 有的朋友會(huì)說:PCB走線怎么會(huì)那么奇形怪狀?但是往往需要計(jì)算走線電阻的是電源信號(hào),電源信號(hào)有時(shí)通過覆銅實(shí)現(xiàn),形成一些不規(guī)則

2019-10-02 08:00:00

A 到 B 的總電阻為 3.98mΩ(3mΩ+0.14mΩ+0.84mΩ)。 有的朋友會(huì)說:PCB 走線怎么會(huì)那么奇形怪狀?但是往往需要計(jì)算走線電阻的是電源信號(hào),電源信號(hào)有時(shí)通過覆銅實(shí)現(xiàn),形成一些

2019-10-26 07:30:00

直角走線一般是pcb布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標(biāo)準(zhǔn)之一,那么直角走線究竟會(huì)對(duì)信號(hào)傳輸產(chǎn)生多大的影響呢?從原理上說,直角走線會(huì)使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)。其實(shí)

2014-11-07 09:40:54

PCB走線線間距能不能走5mil?

2019-09-26 05:35:53

PCB長(zhǎng)距離走線和短距離加個(gè)過孔走線哪種走線更合理?

2019-09-25 22:11:32

AD18 ,PCB,走線,任意走線,在哪里設(shè)置?

2019-03-07 01:36:59

HDMI差分對(duì)PCB怎么走線?要計(jì)算匹配阻抗嗎?差分對(duì)走多長(zhǎng)有要求嗎?四對(duì)差分對(duì)要走一樣長(zhǎng)嗎?

2019-05-31 05:35:21

TI人員你好:運(yùn)放避免不了加反饋,在PCB Layout的時(shí)候,這個(gè)反饋回路的走線,最好的走線是怎樣的?具體一點(diǎn)就是: 這條走線 是直接連接在芯片的輸出端管腳的焊盤上? 還是 要與輸出管腳有一定的距離,畫在輸出端的線上或者是輸出端那個(gè)補(bǔ)償電阻靠近輸出口的那一端?

2019-05-07 13:51:27

PCB走線之問會(huì)產(chǎn)生串?dāng)_現(xiàn)象,這種串?dāng)_不僅僅會(huì)在時(shí)鐘和其周圍信號(hào)之間產(chǎn)生,也會(huì)發(fā)生在其他關(guān)鍵信號(hào)上,如數(shù)據(jù)、地址、控制和輸入/輸出信號(hào)線等,都會(huì)受到串?dāng)_和耦合影響。為了解決這些信號(hào)的串?dāng)_

2018-11-27 15:26:40

的EMI,如果不對(duì)差分信號(hào)進(jìn)行恰當(dāng)?shù)钠胶饣驗(yàn)V波,或者存在任何共模信號(hào),就可能會(huì)產(chǎn)生EMI問題;其次是和單端信號(hào)相比,傳輸差分信號(hào)需要雙倍的信號(hào)線。 如圖2所示為差分對(duì)走線在PCB上的橫截面。D為兩個(gè)差

2018-11-27 10:56:15

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論