之前,首先加粗相應(yīng)的電源連線:5.0V、3.3V等等,這樣一來(lái),就形成了多個(gè)不同形狀的多變形結(jié)構(gòu)。2、對(duì)不同地的單點(diǎn)連接,做法是通過(guò)0歐電阻或者磁珠或者電感連接;3、晶振附近的覆銅,電路中的晶振為一高

2019-09-13 07:30:00

一影響的只不過(guò)是大還是小而已,我建議使用圓弧的邊沿線。7、多層板中間層的布線空曠區(qū)域,不要敷銅。因?yàn)槟愫茈y做到讓這個(gè)敷銅“良好接地”8、設(shè)備內(nèi)部的金屬,例如金屬散熱器、金屬加固條等,一定要實(shí)現(xiàn)“良好

2019-09-17 10:39:56

本帖最后由 WAITXHURT 于 2012-12-27 13:23 編輯

我如果把覆銅和地網(wǎng)絡(luò)相連,電路中的各個(gè)地是不是就不需要連在一起了???望指教

2012-11-14 23:17:26

我們?cè)诋婸CB的時(shí)候通常是通過(guò)覆銅來(lái)進(jìn)行隔離,電器連接,散熱,但是選擇什么樣的覆銅方式好呢?請(qǐng)大家給點(diǎn)意見(jiàn)

2012-12-04 08:29:14

在覆銅時(shí)有那些注意事項(xiàng), 怎樣才能把覆銅覆的好看。求解答謝謝各位老師

2013-03-16 17:32:56

為什么覆銅完會(huì)有這樣的區(qū)別,是一樣的電路圖

2014-11-28 10:28:39

PCB中,地大多數(shù)是通過(guò)覆銅來(lái)解決的,那面覆銅間距有什么要求么?我經(jīng)常用0。2mm的間距,不知道個(gè)有什么影響?求拍磚!!!!!!!!

2012-12-13 13:30:05

覆銅后,如果重新修改覆銅后,會(huì)出現(xiàn)下面的違規(guī)提示:modified polygon(allow modified:no)。請(qǐng)問(wèn)是什么原因?為什么不能修改覆銅?謝謝

2017-03-30 11:26:09

我看技術(shù)文檔上說(shuō)要將信號(hào)的地直接接到AD650芯片的模擬地管腳上,尤其是Cos電容。

請(qǐng)問(wèn)如果設(shè)計(jì)PCB時(shí)直接將一整塊電路板覆銅,并且將模擬地接在覆銅上會(huì)對(duì)芯片性能產(chǎn)生影響嗎?

另外我是把模擬部分和數(shù)字部分分開(kāi),分別由模擬電源和數(shù)字電源,模擬地和數(shù)字地也分開(kāi)。

2023-12-18 08:26:23

覆銅后發(fā)現(xiàn)底層好像這塊區(qū)域覆不上銅,很少畫板不知道什么情況,板子上有其他同樣的封裝,確定了不是封裝的問(wèn)題

2019-06-18 04:38:57

平常用的是全覆銅,直接批量導(dǎo)入過(guò)孔就可以實(shí)現(xiàn)上下層連接;但是網(wǎng)格覆銅的話,似乎不能直接批量過(guò)孔,只能手動(dòng)一個(gè)個(gè)添加過(guò)孔嗎

2020-04-29 12:33:23

能不能像PADS一樣,不用變動(dòng)覆銅外框線,直接再次點(diǎn)擊覆銅命令即可。

2017-05-15 14:01:13

今天安裝了個(gè)Altium Designer 16 ,發(fā)現(xiàn)原來(lái)AD9.4 中的快捷編輯覆銅工具沒(méi)有了,求怎么編輯之前做好PCB文檔中的覆銅?

2017-04-24 15:00:26

他間距 為 8mil, 覆銅后進(jìn)行安全間距檢查報(bào)錯(cuò), 發(fā)現(xiàn)覆銅到 PAD 間距為 4 mil,整板最小間距也都為 6 mil, 怎么覆銅后會(huì)有 4 mil 間距出來(lái)呢? 實(shí)在不解啊... 有圖有真相

2013-03-14 22:24:31

`請(qǐng)教下各位大神 PADS覆銅邊框怎么刪除 如圖 藍(lán)色和粉紅色邊框.`

2017-04-27 09:24:30

`求解各位大神: PADS四層板(頂層,地層,電源層,底層)COPPER POUR畫好覆銅邊框后進(jìn)行Flood,但是看不到覆銅效果,能不能告訴我怎么解決,在這里一直沒(méi)找到原因,萬(wàn)分感謝!!!`

2015-10-27 16:18:20

PCB覆銅都有哪些地方可以覆銅,哪些地方不能覆銅,有沒(méi)有人又相關(guān)的教程,或指點(diǎn)一下,謝謝。

2012-09-12 18:46:31

畫了一塊PCB,覆銅后想返回到未覆銅的狀態(tài),已經(jīng)操作了很多步,返回也沒(méi)用,該怎么操作呢

2019-03-14 06:35:57

;與地線相連,還可以減小環(huán)路面積等。覆銅的方式覆銅一般有兩種基本的方式,就是大面積的覆銅(實(shí)心覆銅)和網(wǎng)格銅,那是大面積覆銅好還是網(wǎng)格覆銅好呢?不好一概而論,它們各有優(yōu)缺點(diǎn)。1、實(shí)心覆銅優(yōu)點(diǎn):具備了加大

2020-03-16 17:20:18

覆銅在PCB生產(chǎn)工藝中,具有非常重要的地位,有時(shí)候覆銅的成敗,關(guān)系到整塊板的質(zhì)量。所謂覆銅,就是把固體銅填充到PCB基板的閑置空間上。覆銅有大面積覆銅和網(wǎng)格覆銅兩種方法,大面積覆銅加大了電流和屏蔽

2017-02-17 11:17:59

,還有一個(gè)就是看起來(lái)很美! 大面積覆銅還是網(wǎng)格覆銅好? 不一概而論。為什么呢?大面積覆銅,如果過(guò)波峰焊時(shí),板子就可能會(huì)翹起來(lái),甚至?xí)鹋荨倪@點(diǎn)來(lái)說(shuō),網(wǎng)格的散熱性要好些。通常是高頻電路對(duì)抗干擾要求

2018-04-25 11:09:05

。所以覆銅主要是地平面的覆銅,不用于電源或其他net的覆銅。2、采用什么方式覆銅敷銅一般有兩種基本的方式,就是大面積的敷銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論

2019-05-29 06:33:50

進(jìn)行印刷線路板的線路設(shè)計(jì)時(shí),設(shè)計(jì)師基本上都會(huì)遇到大面積鋪通的問(wèn)題。印刷線路板上的大面積敷銅常用的有兩種。PCBA樣板 一種是大銅皮,一種是網(wǎng)格銅。其作用也各不相同:一種用于散熱,一種用于屏蔽減少干擾

2012-11-13 12:07:22

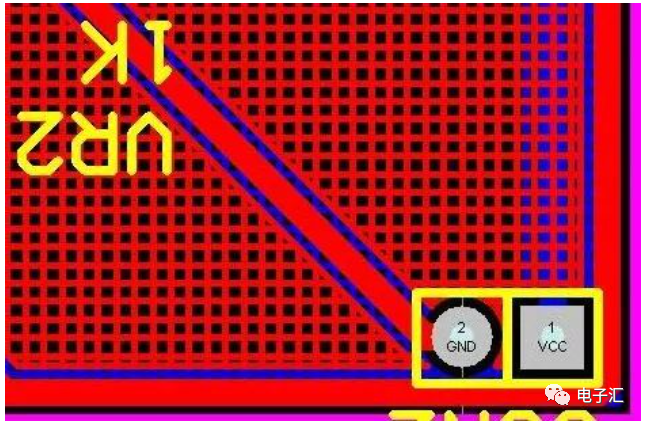

最近在做PCB,以前沒(méi)有留意這個(gè)覆銅問(wèn)題,我一般的STM32的板子覆銅的時(shí)候大家正反兩面肯定是都是對(duì)GND進(jìn)行覆銅,有沒(méi)有誰(shuí)嘗試正面對(duì)VDD3.3覆銅,反面對(duì)GND覆銅呢???這兩者誰(shuí)更好???求

2019-02-14 06:36:20

一般覆銅之后會(huì)出現(xiàn)毛刺、或者有需要調(diào)整的地方,這時(shí)選中覆銅快捷鍵E M G或者在選中之后選擇polygon action-----movevertices選項(xiàng),此時(shí)出現(xiàn)覆銅的各個(gè)定點(diǎn),點(diǎn)擊移動(dòng)修改即可。

2016-06-16 16:05:37

的晶振為一高頻發(fā)射源,做法是在環(huán)繞晶振敷銅,然后將晶振的外殼另行接地。三是孤島(死區(qū))問(wèn)題,如果覺(jué)得很大,那就定義個(gè)地過(guò)孔添加進(jìn)去也費(fèi)不了多大的事。 大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢

2012-09-17 15:09:05

銅,電路中的晶振為一高頻發(fā)射源,做法是在環(huán)繞晶振敷銅,然后將晶振的外殼另行接地。三是孤島(死區(qū))問(wèn)題,如果覺(jué)得很大,那就定義個(gè)地過(guò)孔添加進(jìn)去也費(fèi)不了多大的事。? 另外,大面積覆銅好還是網(wǎng)格覆銅好

2017-04-14 10:48:19

,電路中的晶振為一高頻發(fā)射源,做法是在環(huán)繞晶振敷銅,然后將晶振的外殼另行接地。三是孤島(死區(qū))問(wèn)題,如果覺(jué)得很大,那就定義個(gè)地過(guò)孔添加進(jìn)去也費(fèi)不了多大的事。 另外,大面積覆銅好還是網(wǎng)格覆銅好,不好

2016-11-17 16:03:04

附近的覆銅,電路中的晶振為一高頻發(fā)射源,做法是在環(huán)繞晶振敷銅,然后將晶振的外殼另行接地。三是孤島(死區(qū))問(wèn)題,如果覺(jué)得很大,那就定義個(gè)地過(guò)孔添加進(jìn)去也費(fèi)不了多大的事。另外,大面積覆銅好還是網(wǎng)格覆銅好

2019-06-14 00:42:35

PCB線路板在各類應(yīng)用電器以及儀器儀表到處可見(jiàn),電路板的可靠性是保證各項(xiàng)功能正常運(yùn)行的重要保障,但是在很多線路板我們經(jīng)常看見(jiàn)很多都是大面積的覆銅,設(shè)計(jì)電路板用到大面積覆銅。 一般來(lái)說(shuō)大面積覆銅

2020-09-03 18:03:27

PCB線路板在各類應(yīng)用電器以及儀器儀表到處可見(jiàn),電路板的可靠性是保證各項(xiàng)功能正常運(yùn)行的重要保障,但是在很多線路板我們經(jīng)常看見(jiàn)很多都是大面積的覆銅,設(shè)計(jì)電路板用到大面積覆銅。 一般來(lái)說(shuō)大面積覆銅

2020-06-28 14:25:44

的雙重作用。覆銅一般有兩種基本的方式,就是大面積的覆銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積覆銅,具備了加大電流和屏蔽雙重作用,但是大面積覆銅,如果過(guò)波峰焊

2016-09-06 13:03:13

,還起了屏蔽干擾的雙重作用。覆銅一般有兩種基本的方式,就是大面積的覆銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積覆銅,具備了加大電流和屏蔽雙重作用,但是大面積覆

2019-05-02 10:00:00

,還起了屏蔽干擾的雙重作用。覆銅一般有兩種基本的方式,就是大面積的覆銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積覆銅,具備了加大電流和屏蔽雙重作用,但是大面積覆

2018-08-12 18:27:46

請(qǐng)問(wèn),在PROTEL 99 SE畫PCB板時(shí)怎樣設(shè)置是覆銅和走線之間距離與邊框和覆銅之間距離不相同?

2011-12-22 20:05:11

接地”。如果把敷銅處理恰當(dāng)了,敷銅不僅具有加大電流,還起了屏蔽干擾的雙重作用。 敷銅一般有兩種基本的方式,就是大面積的敷銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好

2009-04-30 10:58:16

如圖,在畫PCB給電源層覆銅時(shí)想要擴(kuò)大覆銅面積卻加不上了,點(diǎn)擊進(jìn)去以后出現(xiàn)了圖片中的英文,我的是AD17,是版本問(wèn)題么?

2018-01-11 11:36:04

` 誰(shuí)來(lái)闡述一下pcb板大面積覆銅的原因是什么?`

2020-03-20 16:54:40

的間距,不影響各層布線的間距了。pcb覆銅技巧之大面積敷銅、網(wǎng)格銅哪一種好? 1、經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積敷銅,具備了加大電流和屏蔽雙重作用,但是大面積

2016-03-01 23:23:39

進(jìn)去也費(fèi)不了多大的事。 另外,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積覆銅,如果過(guò)波峰焊時(shí),板子就可能會(huì)翹起來(lái),甚至?xí)鹋荨倪@點(diǎn)來(lái)說(shuō),網(wǎng)格的散熱性要好些。通常是高頻電路對(duì)抗

2013-01-29 15:43:38

`請(qǐng)問(wèn)pcb為什么要覆銅?`

2019-09-24 17:27:14

`請(qǐng)問(wèn)pcb可以不覆銅嗎?`

2019-09-25 17:26:54

protel pcb 板上為什么某些地方要局部覆銅在整個(gè)板子在覆銅如果直接整個(gè)板子一起覆銅會(huì)怎么樣

2014-11-28 09:00:17

本人proteus小白畫了一塊板子想做實(shí)物,但是在覆銅的時(shí)候出問(wèn)題了,底層覆銅覆不上去,再覆一次就有一個(gè)藍(lán)色的框,有沒(méi)有大神指導(dǎo)下問(wèn)題在哪?

2016-04-23 10:24:54

頻發(fā)射源,做法是在環(huán)繞晶振敷銅,然后將晶振的外殼另行接地。三是孤島(死區(qū))問(wèn)題,如果覺(jué)得很大,那就定義個(gè)地過(guò)孔添加進(jìn)去也費(fèi)不了多大的事。 另外,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積

2014-12-09 15:08:36

覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積敷銅,具備了加大電流和屏蔽雙重作用,但是大面積覆銅,如果過(guò)波峰焊時(shí),板子就可能會(huì)翹起來(lái),甚至?xí)鹋荨R虼?b class="flag-6" style="color: red">大面積敷銅,一般也會(huì)開(kāi)幾個(gè)槽,緩解銅箔起泡

2015-12-29 20:25:01

,還起了屏蔽干擾的雙重作用。覆銅一般有兩種基本的方式,就是大面積的覆銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積覆銅,具備了加大電流和屏蔽雙重作用,但是大面積覆

2018-08-11 21:44:38

為什么覆銅會(huì)這樣子

2019-07-02 04:41:07

請(qǐng)問(wèn)隱藏了覆銅怎么出不來(lái)了 怎么辦

2019-09-23 00:12:36

本帖最后由 stypaonil 于 2013-9-11 15:50 編輯

為什么打印PCB電路圖大面積敷銅都不夠黑?熱轉(zhuǎn)印做電路板,先打印普通A4紙上看看效果,大面積敷銅都不夠黑。打印機(jī)是HP1020.

2013-09-11 15:48:00

為什么我看到很多人的電路都不覆銅?為什么都不覆銅呢?覆銅不是更好么?而且價(jià)格一樣。。。。

2015-06-04 15:53:46

請(qǐng)問(wèn)為什么這個(gè)覆銅點(diǎn)不了啊我想刪除它,當(dāng)選不了

2019-07-03 05:27:45

一、什么是覆銅 所謂覆銅,就是將電路板上閑置的空間作為基準(zhǔn)面,然后用固體銅填充,這些銅區(qū)又稱為灌銅。 覆銅的意義在于:減小地線阻抗,提高抗干擾能力;降低壓降,提高電源效率;與地線相連,還可以減小環(huán)路面積

2023-02-24 17:32:54

,電路中的晶振為一高頻發(fā)射源,做法是在環(huán)繞晶振敷銅,然后將晶振的外殼另行接地。三是孤島(死區(qū))問(wèn)題,如果覺(jué)得很大,那就定義個(gè)地過(guò)孔添加進(jìn)去也費(fèi)不了多大的事。另外,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論

2019-05-22 07:27:39

什么是覆銅?覆銅需要處理好哪幾個(gè)問(wèn)題?到底是大面積覆銅好還是網(wǎng)格覆銅好?

2021-04-25 08:08:04

請(qǐng)問(wèn)如何設(shè)置,覆銅與導(dǎo)線間的寬度,謝謝。

2012-10-04 21:41:59

上打過(guò)孔,與多層板的地平面“良好接地”。如果把覆銅處理恰當(dāng)了,覆銅不僅具有加大電流,還起了屏蔽干擾的雙重作用。 覆銅一般有兩種基本的方式,就是大面積的覆銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格

2019-11-21 14:38:57

加大電流,還起了屏蔽干擾的雙重作用。敷銅一般有兩種基本的方式,就是大面積的敷銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積敷銅,具備了加大電流和屏蔽雙重作用,但是

2015-03-05 15:36:18

單點(diǎn)接地,用來(lái)防止串?dāng)_和一些干擾,或者是作為電源層和地層用來(lái)走線。一般低頻電路,我們是覆實(shí)心銅;高頻電路覆網(wǎng)格銅。這是因?yàn)榫饶汶姎馓匦远裕瑢?shí)心銅的較好,而網(wǎng)格銅次之;但是網(wǎng)格銅能夠隔離高頻干擾信號(hào)。但是對(duì)于大面積鋪銅和溫度較高的板而言,建議采取鋪網(wǎng)格銅的方式。大概就是這些,希望大家集思廣益。

2015-10-14 09:40:30

請(qǐng)問(wèn)layout覆銅時(shí)常規(guī)設(shè)置是什么?我現(xiàn)在想讓同包圍整個(gè)焊盤,要怎么設(shè)置?

2011-12-30 10:10:18

有一個(gè)pcb的圖,已經(jīng)覆銅了,據(jù)說(shuō)是要把銅層移除,然后再修改,修改完了再加上銅層,可是具體怎么操作呢?求高人指點(diǎn)qq:987118969

2013-05-19 20:12:21

:感覺(jué)覆銅的形狀很難控制,矩形都畫不規(guī)則;覆銅的時(shí)候可以有哪些操作?

2019-09-19 00:54:49

AD18中如何大面積鋪銅?

2019-09-26 01:06:05

跟著視頻做發(fā)現(xiàn)老師覆銅的時(shí)候,fill和覆銅是連在一塊的,其目的就是過(guò)電流的主干道,我跟著做發(fā)現(xiàn)fill和覆銅有間隙,該如何解決

2019-07-23 05:35:02

用 Altium 畫板,覆銅之后才發(fā)現(xiàn)要在機(jī)械層開(kāi)孔,而且孔在覆銅上。請(qǐng)問(wèn)怎樣能重新生成覆銅呢?不想刪除重畫。謝謝!

2022-04-09 21:56:06

`我弄的電路PCB圖(沒(méi)覆銅前)`

2013-12-23 15:46:33

1.初次布局,請(qǐng)指教。2.想問(wèn)下我的電路中有數(shù)電 模電 信號(hào)線等,覆銅的時(shí)候,三塊部分需要分開(kāi)覆銅。都是覆銅GND,這分開(kāi)覆銅難道有效果?

2018-01-21 11:43:44

我在進(jìn)行PCB覆銅時(shí),發(fā)現(xiàn)有不需要覆銅的地方被覆了銅,求大神指教如何把銅去掉

2018-03-28 11:21:45

覆銅后出現(xiàn)了這樣的情況,是什么原因。。。。

2014-11-27 17:15:08

1.覆銅的意義 覆銅,就是將PCB上閑置的空間作為基準(zhǔn)面,然后用固體銅填充,這些銅區(qū)又稱為灌銅。敷銅的意義在于,減小地線阻抗,提高抗干擾能力;降低壓降,提高電源效率;還有,與地線相連,減小環(huán)路面積。

2019-07-23 06:29:04

基本的方式,就是大面積的敷銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積敷銅,具備了加大電流和屏蔽雙重作用,但是大面積覆銅,如果過(guò)波峰焊時(shí),板子就可能會(huì)翹起來(lái)

2015-12-28 17:32:28

本帖最后由 wj1478 于 2015-11-23 11:21 編輯

繪制4層板時(shí),有3組地:電源地、數(shù)字地,模擬地; 3組電源:供電電源,數(shù)字電源,模擬電源請(qǐng)問(wèn)以下問(wèn)題1.覆銅時(shí)全覆電源地還是分別覆數(shù)字地,模擬地,在同一層分隔覆銅數(shù)字地,模擬地,還是頂層覆數(shù)字地,底層覆模擬地?

2015-11-23 11:15:21

從剛開(kāi)始畫PCB板時(shí)就對(duì)覆銅的定義不理解而且現(xiàn)在手上有個(gè)4層板看到它的覆銅是底層全部都是地,中間走信號(hào),頂層有畫一塊區(qū)域是電源覆銅那我就不明白了,如果底層全部都是被GND覆銅了,但是底層有時(shí)也會(huì)有

2017-09-06 20:06:11

。 另外,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積覆銅,如果過(guò)波峰焊時(shí),板子就可能會(huì)翹起來(lái),甚至?xí)鹋荨倪@點(diǎn)來(lái)說(shuō),網(wǎng)格的散 熱性要好些。通常是高頻電路對(duì)抗干擾要求高的多用網(wǎng)格,低頻

2017-07-01 16:53:00

加大電流,還起了屏蔽干擾的雙重作用。 敷銅一般有兩種基本的方式,就是大面積的敷銅和網(wǎng)格銅,經(jīng)常也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積敷銅,具備了加大電流和屏蔽雙重

2015-10-12 15:24:32

也有人問(wèn)到,大面積覆銅好還是網(wǎng)格覆銅好,不好一概而論。為什么呢?大面積敷銅,具備了加大電 流和屏蔽雙重作用,但是大面積覆銅,如果過(guò)波峰焊時(shí),板子就可能會(huì)翹起來(lái),甚至?xí)鹋荨R虼?b class="flag-6" style="color: red">大面積敷銅,一般也會(huì)開(kāi)幾個(gè)

2011-11-30 15:14:18

`畫完板子后連線,覆銅,然后有的部分可以覆銅成功,有的則不行顯示空白(如圖所示),請(qǐng)問(wèn)這是怎么回事。這樣對(duì)班子的加工制作有影響嗎。`

2018-12-05 18:45:35

覆銅不可以拖大拖小的嗎

2019-04-22 04:08:13

這是覆銅好還是走線好呢?

2019-09-06 05:35:24

覆銅怎么出現(xiàn)線框

2019-08-06 05:35:17

我覺(jué)得電流流向是正->地->負(fù);所以應(yīng)該是負(fù)電源大面積覆銅好,讓其回流阻抗最小。請(qǐng)問(wèn)是不是這樣?

2019-08-12 01:22:05

什么情況需要給PCB覆銅,什么時(shí)候沒(méi)必要呢,而且覆銅時(shí),線寬有什么要求嗎,有什么需要注意的地方

2012-08-02 23:25:04

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論