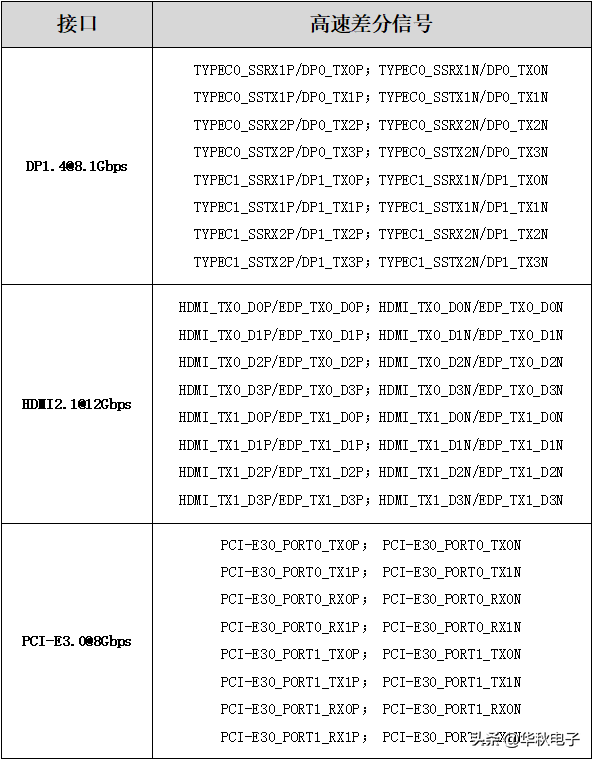

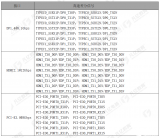

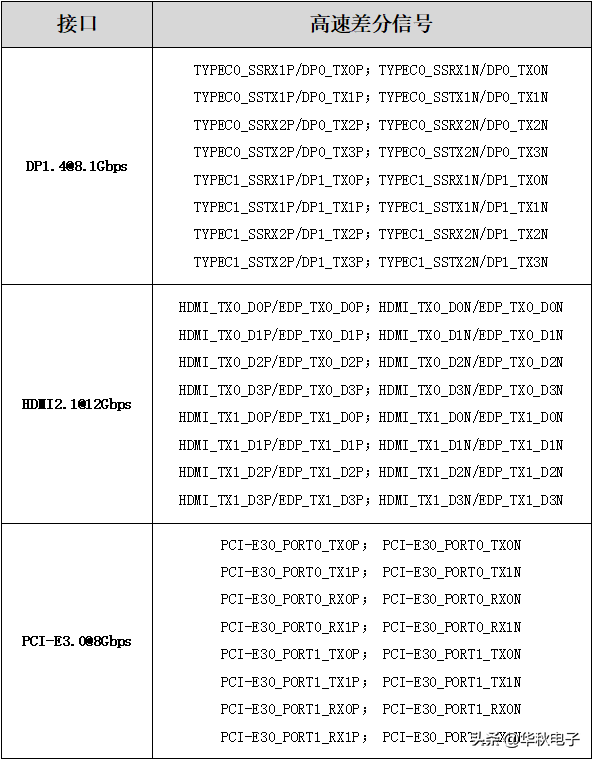

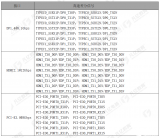

接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量少打孔

2023-08-02 08:41:11 1432

1432

高速電路PCB電源布線技巧

PCB設計來說電源處理好壞直接關系到整個電路板的性能。下面我們分析一下高速電路PCB板的電源布線需要注意的地方和技

2010-03-21 18:29:39 2743

2743

探討使用PROTEL設計軟件實現高速PCB設計的過程中,需要注意的一些布局與布線方面的相關原則問題.

2011-12-10 00:03:00 1146

1146 本文主要詳解PCB設計高速模擬輸入信號走線,首先介紹了PCB設計高速模擬輸入信號走線方法,其次闡述了九大關于PCB設計高速模擬輸入信號走線規則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 8394

8394

在PCB設計過程中,有一項重要的任務是從發射和抗擾度這兩個角度去分辨哪些是關鍵信號。對于發射類,需要重點關注的信號有,時鐘信號,高 dv/dt 或 高di/dt 信號,以及射頻RF信號等。對于抗擾類,需關注的重點信號有,復位、中斷和低電平模擬信號等。識別出這些信號后,請避免將它們靠近電路板邊緣進行布線。

2022-10-11 17:44:12 1102

1102 如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量

2023-08-01 18:10:06 1263

1263

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量

2023-08-03 17:13:35 644

644

一站式PCBA智造廠家今天為大家講講高速PCB設計中的屏蔽方法有哪些?高速PCB設計中的屏蔽方法高速PCB設計布線系統的傳輸速率隨著時代的更迭也在不斷加快,但這也給其帶來了一個新的挑戰——抗干擾能力

2023-08-08 10:19:06 789

789

PCB設計布線(Layout)的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB 設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。

2016-07-18 14:07:10 46477

46477 PCB布線在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做的, 在整個PCB中,以布線的設計過程限定最高,技巧最細、工作量最大。PCB布線有單面布線、 雙面布線及多層

2018-12-07 09:44:39

(7)3.125Gbps以上高速信號布線規劃時優先考慮布線長度,做到最短。(8)高速信號布線需要規則至具有完整參考平面層的布線層(9)模擬信號禁止在數字信號區域布線(10)不同電平信號禁止混合布線說明:如LVTTL與CML電平信號以上便是PCB設計中布線通道計算和設計規劃,下期預告:特殊信號線處理。

2017-09-07 14:36:02

在pcb上靠近平行走高速差分信號線對的時候,在阻抗匹配的情況下,由于兩線的相互耦合,會帶來很多好處。但是有觀點認為這樣會增大信號的衰減,影響傳輸距離,為什么?我在一些大公司的評估板上看到高速布線有的

2012-03-03 12:37:52

請問PCB設計中如何避免平行布線?

2020-01-07 15:07:03

請問PCB設計中如何避免平行布線?

2020-02-26 16:39:38

PCB設計工程師在設計PCB時,往往很想使用自動布線。通常,純數字的電路板(尤其信號電平比較低,電路密度比較小時)采用自動布線是沒有問題的。但是,在設計模擬、混合信號或高速電路板時,如果采用PCB設計軟件的自動布線工具,可能會出現一些問題,甚至很可能帶來嚴重的電路性能問題。

2019-07-10 06:11:44

PCB設計中跨分割的處理高速信號布線技巧

2021-02-19 06:27:15

確保信號完整性的一個重要部分是信號走線的物理布線。PCB設計人員經常承受壓力,不僅要縮小設計,還要保持信號完整性。找到平衡點就是要知道問題可能發生的位置以及在系統出現故障之前可以推送信封的距離

2023-04-12 15:20:37

信號的特性阻抗連續規則高速信號,在層與層之間切換的時候必須保證特性阻抗的連續,否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續,不同層的走線阻抗必須連續。規則五、高速PCB設計的布線方向規則

2021-03-31 06:00:00

的情況下為益。高速PCB設計中建議使用后端的星形對稱結構。規則七、走線長度的諧振規則 檢查信號線的長度和信號的頻率是否構成諧振,即當布線長度為信號波長1/4的時候的整數倍時,此布線將產生諧振,而諧振

2022-04-18 15:22:08

15條高速PCB布線經驗分享

2021-01-29 06:10:51

`高速PCB板的電源布線設計隨著集成電路工藝和集成度的不斷提高,集成電路的工作電壓越來越低,速度越來越快。進入新世紀后,CPU和網絡都邁入了GHZ的時代,這對于PCB板的設計提出了更高的要求。本文正是基于這種背景下,對高速PCB設計中最重要的環節之一——電源的合理布局布線進行分析和探討。`

2009-12-09 13:58:28

本帖最后由 eehome 于 2013-1-5 10:01 編輯

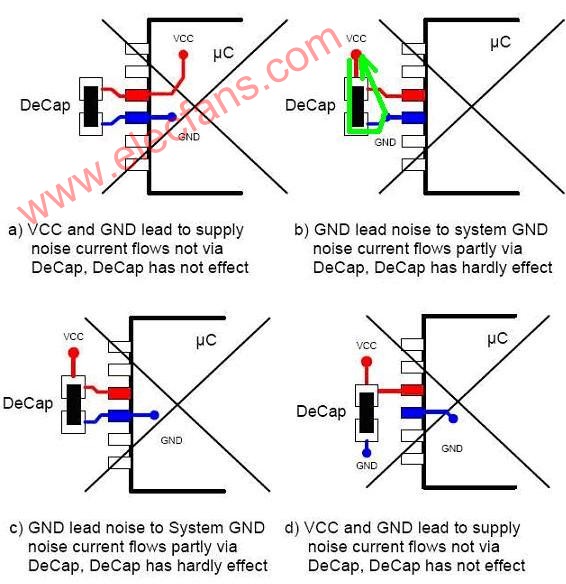

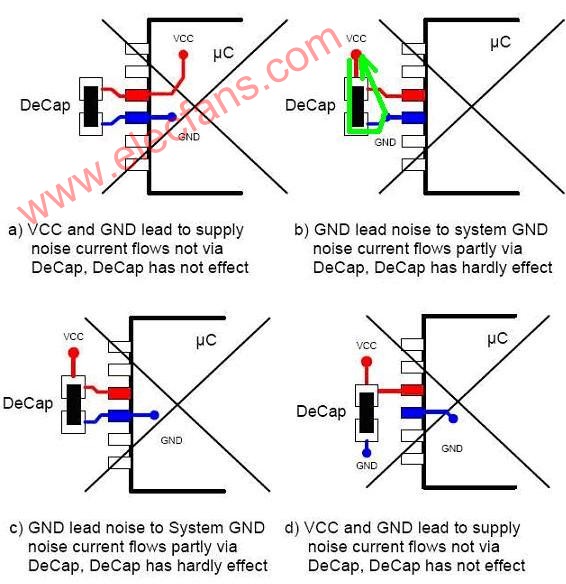

高速PCB板信號接地設計中存在接地噪聲及電磁輻射等問題,提出了高速PCB接地模型,并從PCB設計中布線策略的分析和去耦電容的使用等幾個方面討論了解決高速PCB板的接地噪聲和電磁輻射問題的方法。

2012-03-31 14:31:52

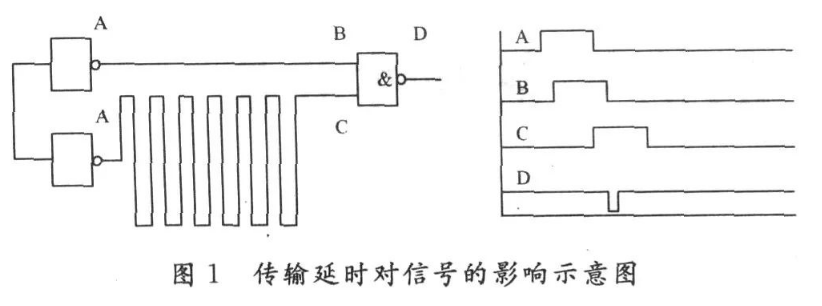

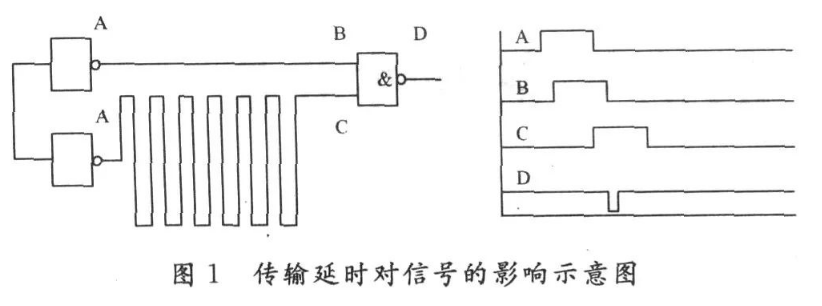

我們定義了傳輸線效應發生的前提條件,但是如何得知線延時是否大于1/2驅動端的信號上升時間? 一般地,信號上升時間的典型值可通過器件手冊給出,而信號的傳播時間在PCB設計中由實際布線長度決定。下圖為信號

2015-05-05 09:30:27

的“啟動自動布線”圖標,或者按下【F9】鍵,進行自動布線。 本文參閱文獻:《PADS9.5實戰攻略與高速PCB設計》 完整PDF版下載:`

2015-09-24 14:39:21

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-02-16 15:06:01

` 本帖最后由 飛翔的烏龜005 于 2017-2-10 10:43 編輯

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用

2017-02-10 10:42:11

高速PCB設計之一 何為高速PCB設計電子產品的高速化、高密化,給PCB設計工程師帶來新的挑戰。PCB設計不再是產品硬件開發的附屬,而成為產品硬件開發中“前端IC,后端PCB,SE集成”3個環節中

2014-10-21 09:41:25

九大PCB設計布線原則:1、一般情況下,首先應對電源線和地線進行布線,以保證電路板的電氣性能。在條件允許的范圍內,盡量加寬電源、地線寬度,最好是地線比電源線寬,它們的關系是:地線>電源線>信號

2016-12-21 10:12:15

電路應具備信號分析、傳輸線、模擬電路的知識。錯誤的概念:8kHz幀信號為低速信號。 問:在高速PCB設計中,經常需要用到自動布線功能,請問如何能卓有成效地實現自動布線? 答:在高速電路板中,不能只是看

2019-01-11 10:55:05

在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做的, 在整個PCB中,以布線的設計過程限定最高,技巧最細、工作量最大。PCB布線有單面布線、 雙面布線及多層布線。布線

2012-08-13 16:30:47

高速PCB設計的信號完整性問題 隨著器件工作頻率越來越高,高速PCB設計所面臨的信號完整性等問題成爲傳統設計的一個瓶頸,工程師在設計出完整的解決方案上面臨越來越大的挑戰。盡管有關的高速仿真工具

2012-10-17 15:59:48

本期講解PCB設計中高速信號關鍵信號的布線要求。一、時鐘信號布線要求在數字電路設計中,時鐘信號是一種在高態與低態之間振蕩的信號,決定著電路的性能。時鐘電路在數字電路中點有重要地位,同時又是產生

2017-10-19 14:25:36

的設計要求,結合筆者設計經驗,按照PCB設計流程,對PCB設計中需要重點關注的設計原則進行了歸類。詳細闡述了PCB的疊層設計、元器件布局、接地、PCB布線等高速PCB設計中需要遵循的設計原則和設計方法以及需要注意的問題等。按照筆者所述方法設計的高速復雜數模混合電路,其地噪很低,電磁兼容性很好。

2012-03-31 14:29:39

`請問高速PCB設計規則有哪些?`

2020-02-25 16:07:38

隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規則: 高速PCB設計解決EMI問題的九大規則

2016-01-19 22:50:31

高速PCB設計指南之(一~八 )目錄2001/11/21CHENZHI/LEGENDSILICON一、1、PCB布線2、PCB布局3、高速PCB設計二、1、高密度(HD)電路設計2、抗干擾技術3

2012-07-13 16:18:40

高速信號PCB布線中降低寄生電感的具體措施

2021-03-08 08:49:46

影響高速信號鏈設計性能的機制是什么?高速ADC設計中的PCB布局布線技巧有哪些?

2021-04-21 06:29:52

高速電路信號完整性分析與設計—PCB設計多層印制板分層及堆疊中應遵徇的基本原則;電源平面應盡量靠近接地平面。布線層應安排與映象平面層相鄰。重要信號線應緊臨地層。[hide] [/hide][此貼子已經被作者于2009-9-12 10:38:14編輯過]

2009-09-12 10:37:02

高速高密度多層PCB設計和布局布線技術

2012-08-12 10:47:09

RT,今天上關于AD敷銅+布局布線+高速PCB設計技巧的資料!期望能夠對眾屌有用!!謝謝!!

2012-08-10 08:51:56

高速PCB設計是一個相對復雜的過程,由于高速PCB設計中需要充分考慮信號、阻抗、傳輸線等眾多技術要素,常常成為PCB設計初學者的一大難點,本文提供的幾個關于高速PCB設計的基本概念及技術要點

2023-04-19 16:05:28

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-01-23 16:04:35

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-01-23 09:36:13

板的布線層層數;(3)信號質量控制:對于高速信號比較集中的PCB設計,如果重點關注信號質量,那么就要求減少相鄰層布線以降低信號間串擾,這時布線層層數與參考層層數(Ground層或Power層)的比例

2017-03-01 15:29:58

在pcb設計中FPGA與高速并行DAC的布線應該注意什么?

2023-04-11 17:30:54

解決高速PCB設計信號問題的全新方法

2021-04-25 07:56:35

高速數字PCB設計信號完整性解決方法

2021-03-29 08:12:25

對于高速信號,pcb的設計要求會更多,因為高速信號很容易收到其他外在因素的干擾,導致實際設計出來的東西和原本預期的效果相差很多。 所以在高速信號pcb設計中,需要提前考慮好整體的布局布線,良好

2023-04-12 14:22:25

求大神分享PCB設計中的布線經驗

2021-04-23 06:42:17

。規則四:高速信號的特性阻抗連續規則高速信號,在層與層之間切換的時候必須保證特性阻抗的連續,否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續,不同層的走線阻抗必須連續。規則五:高速PCB設計

2017-11-02 12:11:12

什么是高速pcb設計高速線總體規則是什么?

2019-06-13 02:32:06

高速PCB設計指南之(一~八 )目錄 2001/11/21 一、1、PCB布線2、PCB布局3、高速PCB設計

二、1、高密度(HD)電路設計2、抗干擾技術

2008-08-04 14:14:42 0

0 高速PCB板的電源布線設計:本文分析討論了高速PCB板上由于高頻信號干擾和走線寬度的減小而產生的電源噪聲和壓降,并提出了高速PCB的電源模型,采用電源總線網絡布線,選取合適

2009-03-24 14:08:40 0

0 本文針對高速PCB板信號接地設計中存在接地噪聲及電磁輻射等問題,提出了高速PCB接地模型,并從PCB設計中布線策略的分析和去耦電容的使用等幾個方面討論了解決高速PCB板的接地噪聲

2009-12-08 14:53:23 63

63 隨著半導體工藝的發展,器件的工作頻率越來越高,使得高速PCB的設計成為產品設計中的一個重要環節,而高速PCB設計所面臨的過沖、下沖、振鈴、延遲和單調性等信號完整性問題

2010-06-07 08:24:08 0

0 PCB設計布線工程師談 一般PCB基本設計流程如下:前期準備->PCB結構設計->PCB布局->布線->布線優化和絲印->網絡和DRC檢查和結構檢查->制版。

&nb

2006-09-25 14:22:31 506

506 PCB布線技術:一個布線工程師談PCB設計的經驗

一般PCB基本設計流程如下:前期準備->PCB結構設計->PCB布局->布線-

2009-09-02 17:15:56 1128

1128 高速PCB設計指南之一

第一篇 PCB布線在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做

2009-11-11 14:57:48 600

600 基于Cadence的高速PCB設計

隨著人們對通信需求的不斷提高,要求信號的傳輸和處理的速度越來越快.相應的高速PCB的應用也越來越廣,設計也越來越

2009-12-12 17:50:27 954

954 高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就

2010-10-30 11:54:01 610

610 本內容詳細介紹了高速PCB設計的布局布線優化方法,歡迎大家下載學習

2011-09-27 16:22:33 0

0 信號完整性分析及其在高速PCB設計中的應用,教你如何設計高速電路。

2016-04-06 17:29:45 15

15 PCB自動布線與流水燈PCB設計,很實用的實例。

2016-06-17 14:59:53 0

0 PCB設計布線中的3種特殊走線技巧,學習資料,感興趣的可以看看。

2022-05-12 10:34:20 0

0 PCB設計,布線設計非常詳細,轉需

2017-02-28 15:09:14 0

0 PADS可提供強大且易于使用的多走線高速布線功能,幫助您應對這些挑戰。讓您可以根據PCB設計定義的規則選擇并完成多走線布線。以及根據需要選擇要完成的走線數量。如果采用PADS多走線HSDRouter,一切盡在您的掌握之中。

2017-09-19 11:41:38 29

29 規則一:高速信號走線屏蔽規則 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有

2017-11-25 07:43:00 7508

7508

高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。

2019-01-24 15:44:43 3352

3352 PCB設計工程師在設計PCB時,往往很想使用自動布線。通常,純數字的電路板(尤其信號電平比較低,電路密度比較小時)采用自動布線是沒有問題的。但是,在設計模擬、混合信號或高速電路板時,如果采用PCB設計軟件的自動布線工具,可能會出現一些問題,甚至很可能帶來嚴重的電路性能問題。

2019-05-07 15:07:18 27784

27784 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計

2019-07-01 15:24:50 5303

5303 布線是PCB設計中非常重要的一部分,會直接影響PCB的性能。在PCB設計過程中,不同的布局工程師對PCB布局有自己的理解,但所有布局工程師都在如何提高布線效率方面保持一致,這不僅為客戶節省了項目開發周期,而且最大化了保證質量和成本。下面介紹PCB設計過程和提高布線效率的步驟。

2019-08-02 09:19:37 3103

3103 在混合信號PCB設計中,對電源走線有特別的要求并且要求模擬噪聲和數字電路噪聲相互隔離以避免噪聲耦合,這樣一來布局和布線的復雜性就增加了。

2020-03-15 17:14:00 1654

1654 高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。

2020-02-27 17:19:32 718

718 在PCB布線規則中,有一條“關鍵信號線優先”的原則,即電源、摸擬信號、高速信號、時鐘信號、差分信號和同步信號等關鍵信號優先布線。

2020-01-01 17:12:00 2772

2772 為了保證線路板設計時的質量問題,在PCB設計的時候,要注意PCB圖布線的部分是否符合要求。

2019-09-02 10:12:36 2190

2190 本文主要分析一下在高速PCB設計中,高速信號與高速PCB設計存在一些理解誤區。 誤區一:GHz速率以上的信號才算高速信號? 提到高速信號,就需要先明確什么是高速,MHz速率級別的信號算高速、還是

2019-11-05 11:27:17 10310

10310

高速PCB設計是指信號的完整性開始受到PCB物理特性(例如布局,封裝,互連以及層堆疊等)影響的任何設計。而且,當您開始設計電路板并遇到諸如延遲,串擾,反射或發射之類的麻煩時,您將進入高速PCB設計領域。

2020-06-19 09:17:09 1537

1537 在高速PCB設計中,“信號”始終是工程師無法繞開的一個知識點。不管是在設計環節,還是在測試環節,信號質量都值得關注。

2020-11-20 10:55:07 3418

3418 讓你布線少走彎道的15條高速PCB布線經驗分享

2022-02-12 10:44:53 5486

5486 在高速PCB設計中,差分信號的應用越來越廣泛,這主要是因為和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優勢。

2021-03-23 14:40:47 2760

2760 當我們在做高速PCB設計時,很多工程師都會糾結于包地問題,那么高速信號是否需要包地處理呢? 首先,我們要明確為什么要包地?包地的作用是什么? 實際上,包地的作用就是為了減小串擾,串擾形成的機理是有害

2021-11-09 11:28:32 8039

8039 高速電路信號完整性分析與設計—PCB設計1

2022-02-10 17:31:51 0

0 高速電路信號完整性分析與設計—PCB設計2

2022-02-10 17:34:49 0

0 在現代電子設計中,高速信號的傳輸已成為不可避免的需求。高速信號傳輸的成功與否,直接影響整個電子系統的性能和穩定性。因此,PCB設計中的高速信號傳輸優化技巧顯得尤為重要。本文將介紹PCB設計中的高速信號傳輸優化技巧。

2023-05-08 09:48:02 1143

1143 一站式PCBA智造廠家今天為大家講講PCB設計差分布線有什么要求?PCB設計差分布線要求及操作技巧。高速串行總線的普及,使得PCB板上差分信號越來越多,那么,PCB設計如何進行差分布線呢?接下來

2023-07-07 09:25:21 3156

3156

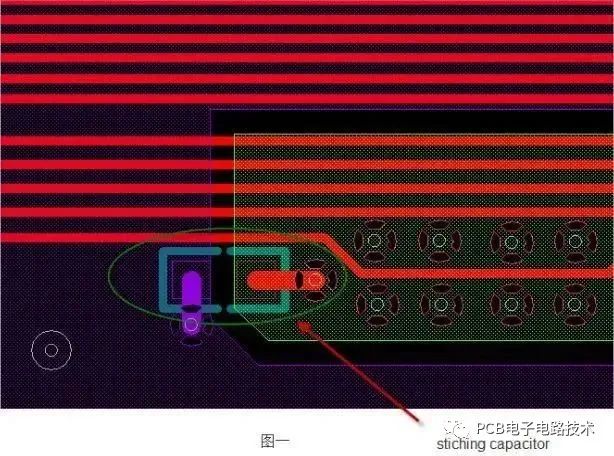

8Gbps及以上高速信號PCB布線建議 —來源:瑞星微RK3588 PCB設計白皮書 如表1-1所示,RK3588芯片以下接口的信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求

2023-08-02 07:35:01 423

423

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。高速信號布線時盡量少打孔

2023-08-03 17:31:07 662

662

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量

2023-08-03 18:15:02 486

486 PCB高速信號在當今的一個pcb設計中顯然已成為主流,一名優秀的PCB工程師,除了在實戰項目慢慢積累設計PCB高速信號的經驗外,還需通過不斷學習來提升自己的知識儲存和專業技能。本文捷多邦小編就給大家科普一下PCB高速信號的一些相關布線知識。

2023-09-15 10:19:18 720

720 能引路誤動作從而導致系統無法正常工作。接下來深圳PCBA公司為大家分享高速PCB設計布線解決信號串擾的方法。 PCB設計布線解決信號串擾的方法 一、 在可能的情況下降低信號沿的變換速率 通常在器件的時候,在滿足設計規范的同時盡量選擇慢速的器

2023-10-19 09:51:44 1234

1234 對于高速信號,pcb的設計要求會更多,因為高速信號很容易收到其他外在因素的干擾,導致實際設計出來的東西和原本預期的效果相差很多。 所以在高速信號pcb設計中,需要提前考慮好整體的布局布線,良好的布局

2023-11-06 10:04:04 340

340

高速電路無疑是PCB設計中要求非常嚴苛的一部分,因為高速信號很容易被干擾,導致信號質量下降,所以在PCB設計的過程中就需要避免或降低這種情況的發生。 在具體的高速電路布局布線中,這些知識技能需要掌握

2023-11-06 14:55:20 255

255 高速電路無疑是PCB設計中要求非常嚴苛的一部分,因為高速信號很容易被干擾,導致信號質量下降,所以在PCB設計的過程中就需要避免或降低這種情況的發生。 在具體的高速電路布局布線中,這些知識技能需要掌握

2023-11-06 15:14:06 263

263 一站式PCBA智造廠家今天為大家講講PCB設計關鍵信號如何去布線?PCB關鍵信號的布線要求。在PCB設計布線規則中,有一條“關鍵信號線優先”的原則,即電源、摸擬信號、高速信號、時鐘信號、差分信號

2023-11-22 09:11:10 377

377

在高速PCB設計中,信號層的空白區域可以敷銅,而多個信號層的敷銅在接地和接電源上應如何分配? 在高速PCB設計中,信號層的空白區域可以敷銅,而多個信號層的敷銅在接地和接電源上應該經過合理分配。接地

2023-11-24 14:38:21 635

635 PCB上信號速度高、端接元件的布局不正確或高速信號的錯誤布線都會引起信號完整性問題,從而可能使系統輸出不正確的數據、電路工作不正常甚至完全不工作,如何在PCB板的設計過程中充分考慮信號完整性的因素,并采取有效的控制措施,已經成為當今PCB設計業界中的一個熱門話題。

2024-01-11 15:28:00 86

86

的不良影響。在進行PCB布線設計時,需要遵循一定的規則和原則,下面我們將會介紹PCB設計中的六大布線規則。 PCB設計六大布線規則 一:按照傳輸信號速度分類 在布線時需要按照信號傳輸速度的不同進行分類布線。一般來說,傳輸速度越快的信號需要

2024-01-22 09:23:53 495

495

電子發燒友App

電子發燒友App

評論