高速PCB層板疊層配置實例

- 電源(244066)

- 高速信號(17617)

- PCB(13204)

相關推薦

10層板PCB,內層信號層(5,6)阻抗匹配如何選擇參考層?

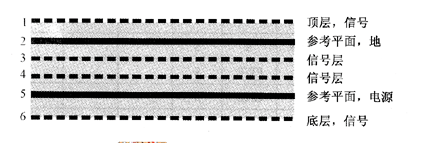

向大神請教:在設計一個10層板PCB時,一些關鍵信號需要做阻抗匹配,對于如何選擇參考層有一些不明白,如下:1、中間信號層5做阻抗匹配時,是否可以選用電源層4和電源層7共同作為參考層?2、TOP信號層1某些信號做阻抗匹配時,是否可選用信號層3作為參考層?層疊示意圖

2022-04-24 11:23:09

8層PCB 布銅問題

請教各位大師:FPGA 設計的一塊8層板,2層電源,2層地,4sig。 FPGA 信號有80M. 想問一下怎么疊層合適? 電源層有很多空余位置布電源好,還是布地線好?信號層的空余地方要布地線嗎? 謝謝。

2015-07-18 11:07:25

PCB疊層的幾種不同變體

兩個實驗設計的結果一起顯示。注意,MOSFET和層4平面之間也沒有直接連接,相應的電路拓撲將顯示在第89頁的圖2中。 (1)單層板。 (2)2層板 (3)4層板。 圖9:1、2、4層PCB疊層

2023-04-20 17:10:43

PCB疊層規則你都懂了嗎?

結構的對稱性。常用的疊層結構:下面通過4層板的例子來說明如何優選各種層疊結構的排列組合方式。對于常用的4層板來說,有以下幾種層疊方式(從頂層到底層)。(1)Siganl_1(Top),GND

2015-03-06 11:02:46

PCB疊層設計

了信號線的特征阻抗,也可有效地減少串擾。所以,對于某些高端的高速電路設計,已經明確規定一定要使用6層(或以上的)的疊層方案,如Intel對PC133內存模塊PCB的要求。這主要就是考慮到多層板在電氣

2016-05-17 22:04:05

PCB疊層設計層的排布原則和常用層疊結構

和地層之間應該緊密耦合)在設計時需要首先得到滿足,另外如果電路中需要傳輸高速信號,那么設計原則 3(電路中的高速信號傳輸層應該是信號中間層,并且夾在兩個內電層之間)就必須得到滿足。10層板PCB典型10層

2016-08-24 17:28:39

PCB疊層設計層的排布原則和常用層疊結構

在設計多層PCB電路板之前,設計者需要首先根據電路的規模、電路板的尺寸和電磁兼容(EMC)的要求來確定所采用的電路板結構,也就是決定采用4層,6層,還是更多層數的電路板。確定層數之后,再確定內電層

2018-09-17 17:41:10

PCB疊層設計的原則和結構

到的電源優先鋪整塊銅皮;易受干擾的、高速的、沿跳變的優選走內層等等。 下表給出了多層板層疊結構的參考方案,供參考。 PCB設計之疊層結構改善案例(From金百澤科技) 問題點 產品有8組網口與光口,測試

2018-09-18 15:12:16

PCB疊層設計需要注意這8件事

、EMC、制造成本等要求有關。對于大多數的設計,PCB的性能要求、目標成本、制造技術和系統的復雜程度等因素存在許多相互沖突的要求,PCB的疊層設計通常是在考慮各方面的因素后折中決定的。高速數字電路和射須電路通常采用多層板設計。

2019-09-17 14:11:49

PCB層設計怎么讓EMC設計效果最優

。 PCB的EMC設計的關鍵,是盡可能減小回流面積,讓回流路徑按照我們設計的方向流動。而層的設計是PCB的基礎,如何做好PCB層設計才能讓PCB的EMC效果最優呢? PCB層的設計思路: PCB疊層EMC

2018-08-08 17:18:29

PCB板疊層方式

L1和L4信號線,L2地線層,L3電源層。如果L4層上的元器件較少,是主布線層,那么將L2改為電源,L3為地,效果可能會更好些。 6層板:L2和L5為地線層和電源層,其它為信號層。

2019-05-21 10:19:01

PCB四層板與三層板的區別是什么

四層板指的是電路印刷板PCBPrintedCircuitBoard用4層的玻璃纖維做成,可降低PCB的成本但效能較差。 PCB板做成多層主要是減少面積,同樣面積的多層板比雙面單層板能完成復雜

2021-02-05 14:51:47

PCB四層板里面的電源層和地層是什么意思?

PCB 四層板里面的電源層和地層是什么意思,或者多層板里面的電源層和地層是什么意思?

我只是把四層板里面的中間兩層當做是裝換的或連接的,為什么教材里面說是電源層和地層呢?

2023-05-06 10:15:14

PCB機械層的問題

現在在用AD2018AD2018在PCB板可以提供15個機械層,有的機械層(比如第一層)是元器件安裝層,有的機械層(比如第二層)是元件3D層,有的機械層(比如第三層)是元器件外部邊框層,有如下兩個

2019-05-27 10:17:58

PCB熱設計之通用的4層PCB覆蓋

,對于不同的間距“d”確定結溫。結果如圖17所示。 (1)單層板。 (2)2層板 (3)4層。 圖17:4層PCB上不同間距d的兩個器件的實驗設計結果 這兩個內部層的(4層PCB)增加導致了

2023-04-21 15:04:26

PCB設計中疊層算阻抗時需注意的四大事項

在高速PCB設計流程里,疊層設計和阻抗計算是登頂的第一梯。阻抗計算方法很成熟,不同軟件的計算差別不大,相對而言比較繁瑣,阻抗計算和工藝制程之間的一些"權衡的藝術",主要是為了達到

2018-01-22 14:41:32

PCB阻抗控制和疊層設計

是電路板設計的一個重要指標,特別是在高頻電 路的PCB設計中,必須考慮導線的特性阻抗和器件或信號所要求的特性阻抗是否一致,是否匹配。這就涉及到兩個概念:阻抗控制與阻抗匹配,本文重點討論阻抗控制和疊層設計的問題。

2019-05-30 07:18:53

疊層電感-疊層陶瓷電感-貼片疊層電感-片式疊層電感

本帖最后由 yfsjdianzi 于 2014-5-11 14:23 編輯

疊層電感也就是非繞線式電感,是電感分類的其中一類。外形尺寸小,閉合電路,無交互干擾,適合于高密度安裝,無方

2014-05-10 20:04:18

疊層電感的優點是什么?

疊層電感在現實中應用也十分廣泛,目前疊層電感類產品被廣泛用于筆記本電腦數位電視,數位錄放影機,列表機,硬式磁碟機,個人電腦和其安一般消費性及電腦主品上輸入、輸出線路之雜訊消除。

2019-10-17 09:00:27

層PCB板的層疊結構

結構的對稱性。常用的疊層結構:下面通過4層板的例子來說明如何優選各種層疊結構的排列組合方式。對于常用的4層板來說,有以下幾種層疊方式(從頂層到底層)。(1)Siganl_1(Top),GND

2015-02-11 16:25:13

高速PCB又疊層設計盡量使用多層電路板

在高速電路中推薦使用多層電路板。首先,多層電路板分配內層專門給電源和地,因此 具有如下優點: · 電源非常穩定; · 電路阻抗大幅降低; · 配線長度大幅縮短。 此外,從成本角度考慮

2018-11-23 16:04:04

高速PCB多層板疊層設計原則

的低阻抗的電流返回路徑最重要的就是合理規劃這些參考平面的設計。圖1所示為一種典型多層PCB疊層配置。 信號層大部分位于這些金屬實體參考平面層之間,構成對稱帶狀線或是非對稱帶狀線。此外,板子的上、下兩個

2018-11-27 15:14:59

高速PCB,六層板最合適的結構有哪些?(附免費打樣福利)

內層有地、信號線、電源,下面通過1.6mm板厚幾個疊層結構,分析哪種結構最合適。 首先,介紹一下PCB線路板廠采用較多的六層板的普通結構,此結構使用于普通無高速信號的PCB板。(華秋電路現六層板免費打

2019-10-16 18:03:20

AD畫PCB板時,如何讓元件引腳連接到電源層

比如:我用AD畫PCB,4層板,頂和底層為信號層,中間兩側分別是GND和VCC。假如,現在我有一個元器件的引腳是要接電源層。PCB板上的空都是過孔。我怎么才能把這個引腳設置到電源層呢? 是雙擊引腳修改屬性layer to vcc么?

2015-08-16 22:58:44

DDR電路的疊層與阻抗設計

在8層通孔板疊層設計中,頂層信號 L1 的參考平面為 L2,底層信號 L8 的參考平面為 L7。

建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅

2023-12-25 13:46:25

DDR電路的疊層與阻抗設計!

在8層通孔板疊層設計中,頂層信號 L1 的參考平面為 L2,底層信號 L8 的參考平面為 L7。

建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅

2023-12-25 13:48:49

DDR跑不到速率,調整下PCB疊層就搞掂了?

是怎么怎么走的,和demo板是如何如何相似,卻沒注意到疊層設計本身已經有這么大的差別了。

這時既然客戶要省成本嘛,高速先生肯定還是尊重客戶的這個意愿的,就在客戶這個省成本的設計中去想辦法改善信號質量,從而達到

2023-06-02 15:32:02

cadence16.5 疊層設置怎樣設置正片負片

allegro16.5多層PCB板的疊層設計時,內電層設計為正片或負片的選項不知道怎樣處理,我原來用的是allegro15.7,allegro15.7設置內電層時,它有個選項,可選為正片或負片,但allegro16.5沒看到這個選項,求教知道的人指導一下

2015-09-20 18:45:24

protel99se高級視頻教程(單層板到四層板到八層ARM板)

四:添加其他的內電層區域5-5 分割內電層操作實例之五:內電層分割完成后的一些操作5-7 4層PCB設計實例之二:規劃電路板并載入網絡表5-8 4層PCB設計實例之三:元件布局5-9 4層PCB

2016-10-21 13:40:00

【干貨】阻抗設計必備:PCB阻抗參數推薦及疊層結構(4層板)

您還在為阻抗設計頭疼嗎?這里有齊全的阻抗參數及疊層結構。有它您無需再去仿真,我們已將其一一列出,如 90ohm線寬線距為7/6mil 或 5/4mil ,結合布線空間選擇對應的線寬線距。

2020-06-10 20:54:11

【精品推薦】8層板設計的核心板實例講解

小,而且走線密度大,一般都要多層板才能設計出來,最常見的形式是郵票孔形式的。02實例講解下面是一塊8層板的核心板,上下有兩排郵票孔,用來焊接。因為要貼在PCB板表面上,所以核心板的底面就沒有放置元器件

2021-04-24 06:30:02

【精選資料】PCB設計資料大全(珍藏系列)

1、淺析智能手機抗EMI的PCB Layout疊層設計簡介:關于智能手機抗EMI的PCB Layout疊層設計,分析很透徹,小伙伴們可以下載來參考參考。2、基于信號完整性分析的高速PCB仿真

2021-03-26 18:00:20

【論文】多層印制板疊層設計對信號完整性的影響研究

基于優化多層印制板,改進信號完整性的設計,主要通過調整疊層設計中的各層導線寬度、基板厚度、填充層厚度和絕緣材料厚度,4個維度參數,從而改變信號傳輸路徑特性阻抗的方法,有具體應用實例。

2021-04-06 11:15:43

【資料】PCB六層的兩種板疊層結構方案介紹

`完整的參考平面可以用來保證回路的連續性,寬的線寬可以降低信號的導體損耗,背鉆工藝可以減小過孔的Stub,提高信號的完整性,但是這樣往往會導致成本的增加。本文章將介紹兩種六層板疊層結構。`

2021-03-30 10:42:55

【資料】一些關于多層PCB疊層設計的原則

阻抗的電流返回路徑最重要的就是合理規劃這些參考平面的設計。圖1所示為一種典型多層PCB疊層配置。圖1 一種典型多層PCB疊層配置回復帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:18:25

【資料】如何創建PCB最佳疊層?

在電路板設計上創建PCB疊層也會遇到類似情況:我們可能不了解最適宜的PCB材料,也不知道如何有效地構建疊層。在作出決定之前,清楚了解我們的需求才能對設計最為有利。優化設計意味著梳理可供考慮和選擇

2021-08-04 10:13:17

【資料】淺析智能手機抗 EMI 的 PCB Layout 疊層設計

手機PCB Layout層數選擇與疊層設計方案剖析。回復帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:10:24

【資料】淺談PCB疊層設計

本文主要介紹多層PCB設計疊層的基礎知識,包括疊層結構的排布一般原則,常用的疊層結構,疊層結構的改善案例分析。回復帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:06:58

一個4層的PCB板與熱散熱過孔

4.3.6 實驗設計6:一個4層的PCB板與熱散熱過孔 為了完整性,“4層+散熱過孔”結構也被實驗設計為1層銅的幾個尺寸,并再次疊層,如圖8所示。結果如圖13所示。 (1)單層板。 (2

2023-04-21 14:51:37

一到八層電路板的疊層設計方式

本帖最后由 張飛電子學院呂布 于 2021-4-12 16:36 編輯

一到八層電路板的疊層設計方式 電路板的疊層安排是對 PCB 的整個系統設計的基礎。疊層設計如有缺陷,將最終影響到整機

2021-04-12 16:35:28

你知道高速疊層設計原則有哪些嗎

高速疊層設計原則:考慮因素:BGA 扇出、局部布線密度、阻抗控制、顧客要求、SI/PI考慮、成本、電設計源分割、板厚、板厚與孔徑比工藝要求:對稱性表層與內層不要選擇4.0mil以下介質不要選

2022-03-02 06:09:06

關于四層板差分的參考層是電源平面的問題

1.四層板疊層:S-G-P-S因差分線序交叉需打孔換層走BOTTOM,現在第四層差分對應的參考平面是電源平面。一直有個疑惑:第四層差分對應的第三層位置畫塊地銅皮做參考,這樣會不會好點?粉色為第三層

2019-08-06 09:45:08

印制電路板的疊層設計

PCB的布線規則 多層電路板的電磁兼容分析可以基于克希霍夫定律和法拉第電磁感應定律。 根據克希霍夫定律, 任何時域信號由源到負載的傳輸都必須有一個最低阻抗的路徑。 具有多層的PCB常常用于高速

2012-04-23 17:29:21

原創|PCB設計中疊層結構的設計建議

(厚的PP介質加工困難,一般會增加一個芯板導致實際疊層數量的增加從而額外增加加工成本)4、PCB外層(Top、Bottom層)一般選用0.5OZ厚度銅箔、內層一般選用1OZ厚度銅箔說明:一般根據電流

2017-01-16 11:40:35

浙江疊層電感和繞線電感的區別

貼片電感從制造工藝上可分為:繞線型、疊層型、編織型和薄膜片式電感器,常用的為繞線型電感和疊層型電感,繞線型電感是傳統繞線電感器小型化的產物,而疊層型電感采用多層印刷技術和疊層生產工藝制作,體積比繞線

2020-06-02 09:33:23

電子元器件:“疊層電感”的認識

`疊層電感也就是非繞線式電感,疊層電感是電感按結構不同對電感進行分類的其中一類。特 性: 1.外形尺寸小。 2.閉合電路,無交互干擾,適合于高密度安裝。 3.無方向性,規范化的自動貼片安裝外形

2013-08-29 17:41:52

電路板的疊層設計的相關資料分享

電路板的疊層設計是對PCB的整個系統設計的基礎,疊層設計若有缺陷,將最終影響到整機的EMC性能。疊層設計是一個復雜的,嚴謹過程,當然,設計開發,沒必要從零開始經過一系列的復雜計算和仿真,來確定設計方案是否合適,僅需要總結前人的經驗,選擇合適系統的疊層方案。

2021-11-12 07:59:58

線路板設計之疊層結構改善案例

電子電路產品信號傳輸線一般均要做阻抗控制,目前各信號傳輸一般阻抗控制公差要求10%,隨著網絡的高速發展,電子電路產品特別是通訊類電子產品,其對信號傳輸提出了越來越高的要求,PCB板上信號線的阻抗控制

2019-05-29 08:11:41

自制pcb6層板(附圖)

實現,在向里的2-3圈Pin需要就地打孔扇出,走線基本上要走L3或L4或Bottom層。4、對此運行400MHz的高速數字電路系統多層板,應不應當進行信號完整性分析及如何分析。5、PCB的疊層順序。6

2011-10-21 09:48:17

請問8層板最佳布板的疊層順序是什么樣的?

RT,現有一個項目,需要布置八層板,兩層信號,因整塊板的平均功率達50W,需要布置兩層電源,其它層全鋪地,最佳的疊層順序是怎么樣較好。

2019-09-24 05:07:43

轉: PCB疊層設計層的排布原則和常用層疊結構

需要傳輸高速信號,那么設計原則 3(電路中的高速信號傳輸層應該是信號中間層,并且夾在兩個內電層之間)就必須得到滿足。 10層板 PCB典型10層板設計 一般通用的布線順序是TOP--GND---

2016-08-23 10:02:30

避開PCB假八層結構的溫柔陷阱---淺談六層板的疊層

在《PCB的筋骨皮》一文中,我們提出了當板厚在1.6mm及以上時,怎樣避免使用假八層的疊層,而導致PCB成本增加的問題。感覺大家的回答很踴躍哈,看來這個問題還是比較典型的。本來想截取一些回答放在

2019-05-30 07:20:55

避開PCB假八層結構的溫柔陷阱---淺談六層板的疊層

在《PCB的筋骨皮》一文中,我們提出了當板厚在1.6mm及以上時,怎樣避免使用假八層的疊層,而導致PCB成本增加的問題。感覺大家的回答很踴躍哈,看來這個問題還是比較典型的。本來想截取一些回答放在

2022-03-07 16:04:23

避開假八層的溫柔陷阱----淺談六層板的疊層

在《PCB的筋骨皮》一文中,我們提出了當板厚在1.6mm及以上時,怎樣避免使用假八層的疊層,而導致PCB成本增加的問題。感覺大家的回答很踴躍哈,看來這個問題還是比較典型的。本來想截取一些回答放在

2019-05-29 07:26:53

高頻高速PCB設計中的阻抗匹配,你了解多少?

的相對位置。特性阻抗要求的差分對間的線寬/線距則取決于選擇的PCB疊層結構。

由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結構必須能實現板上的所有阻抗需求,包括內層

2023-05-26 11:30:36

電子發燒友App

電子發燒友App

評論