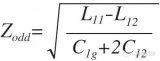

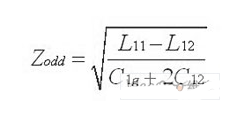

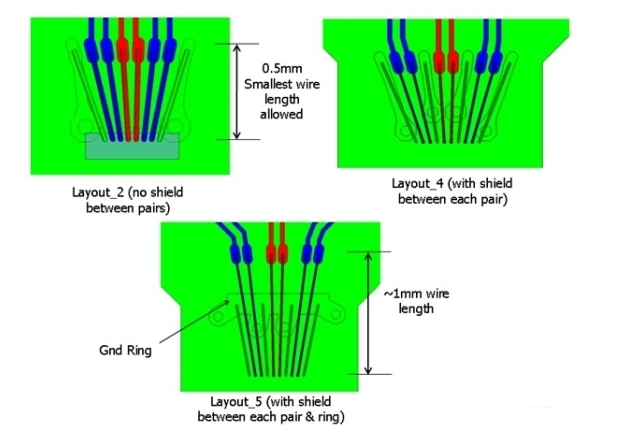

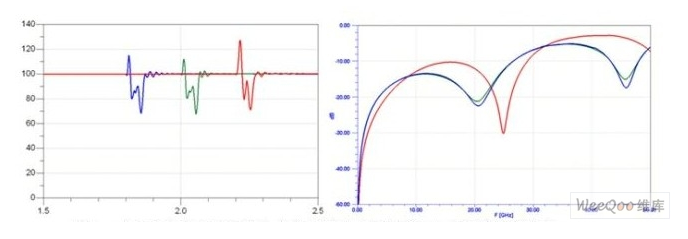

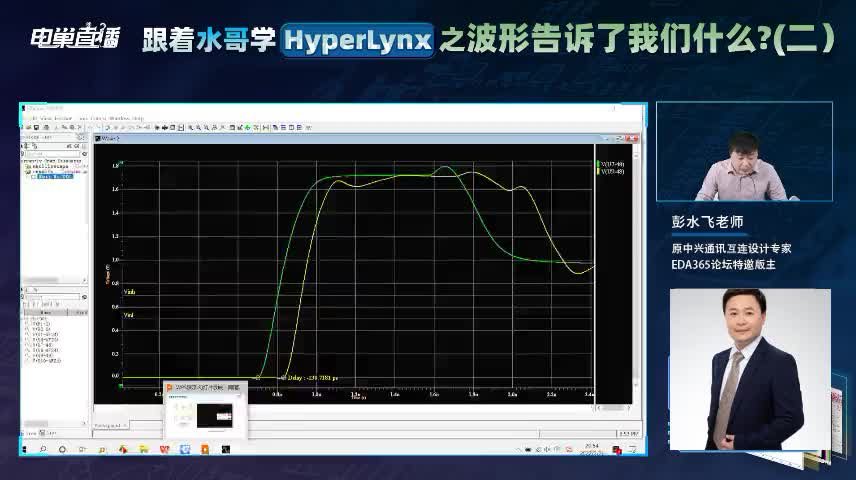

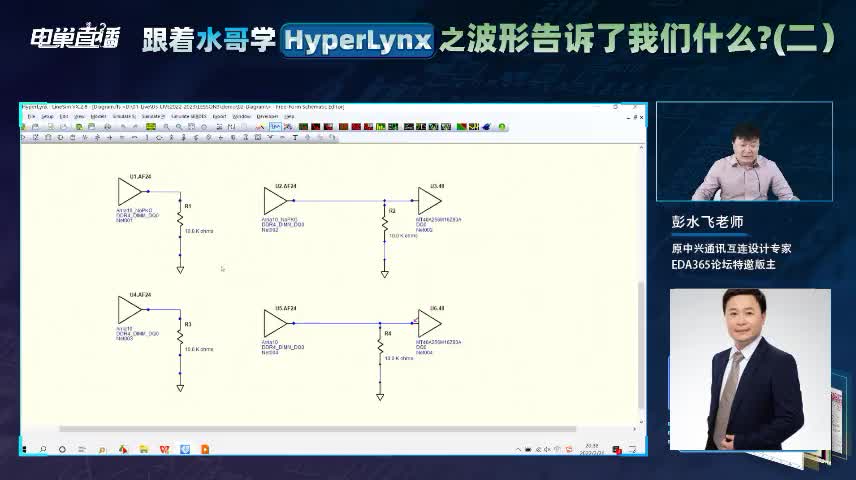

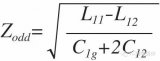

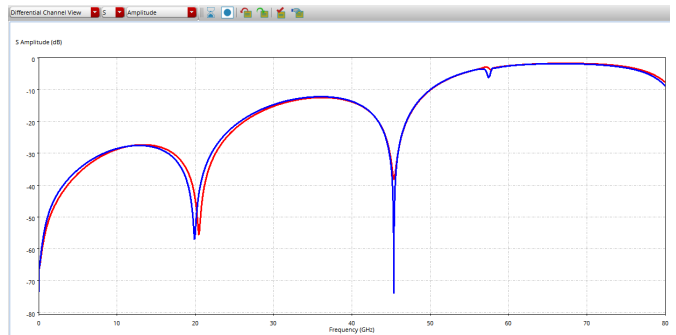

的阻抗不連續性和改善其回波損耗性能,以滿足10Gbps SerDes鍵合線封裝規范。 差分阻抗 一個典型的SerDes通道包含使用兩個單獨互連結構的互補信號發射器和接收器之間的信息交換。兩個端點之間

2018-09-12 15:29:27

自己做封裝庫時,焊盤的大小有沒有個設計規范??、要比實際器件管腳的大小大多少啊?、、求指教!!

2013-09-14 10:04:23

自己做封裝庫時,焊盤的尺寸有沒有個設計規范??、要比實際器件管腳的大小大多少啊?、、求指教!!

2013-09-14 11:33:26

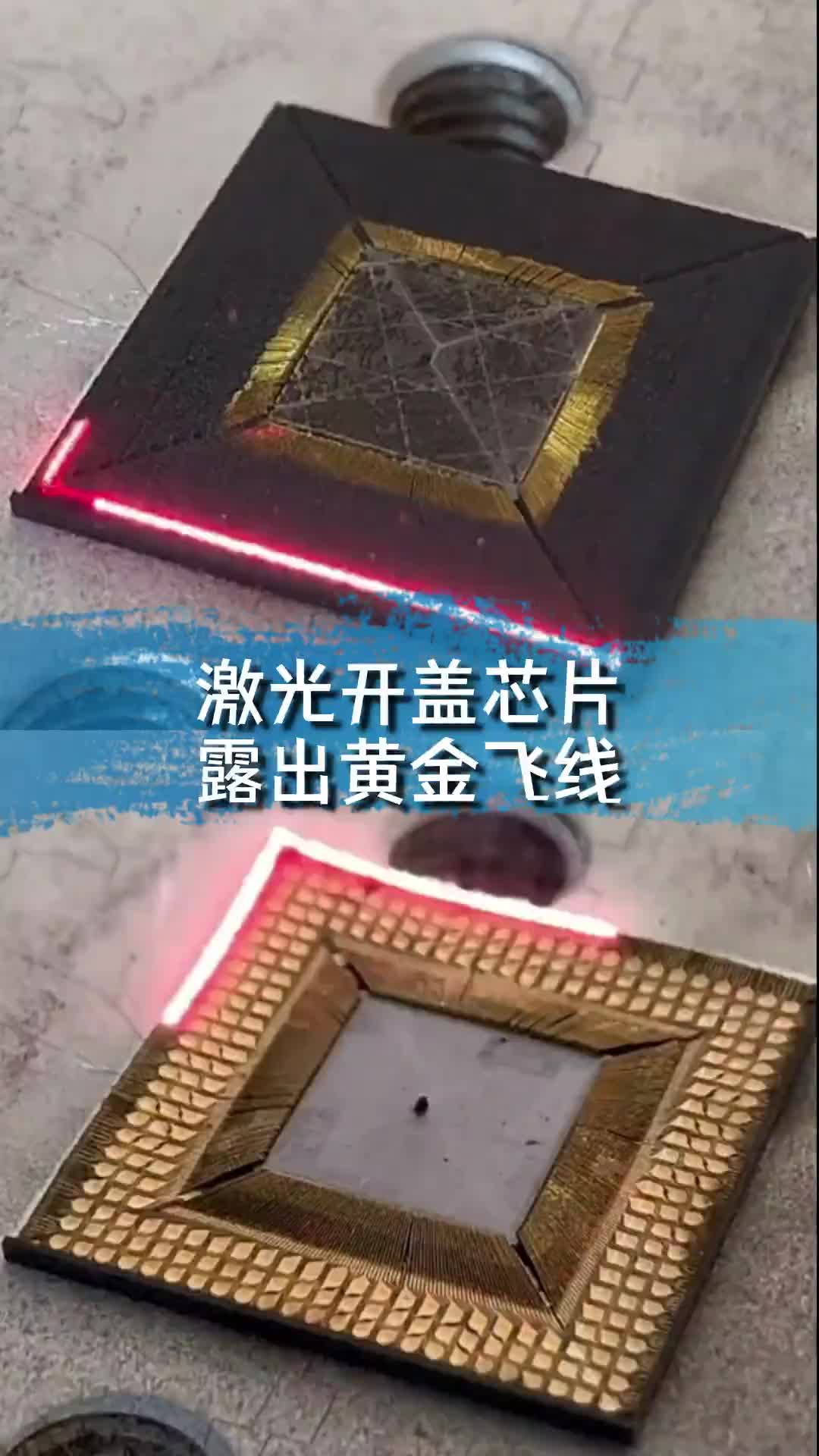

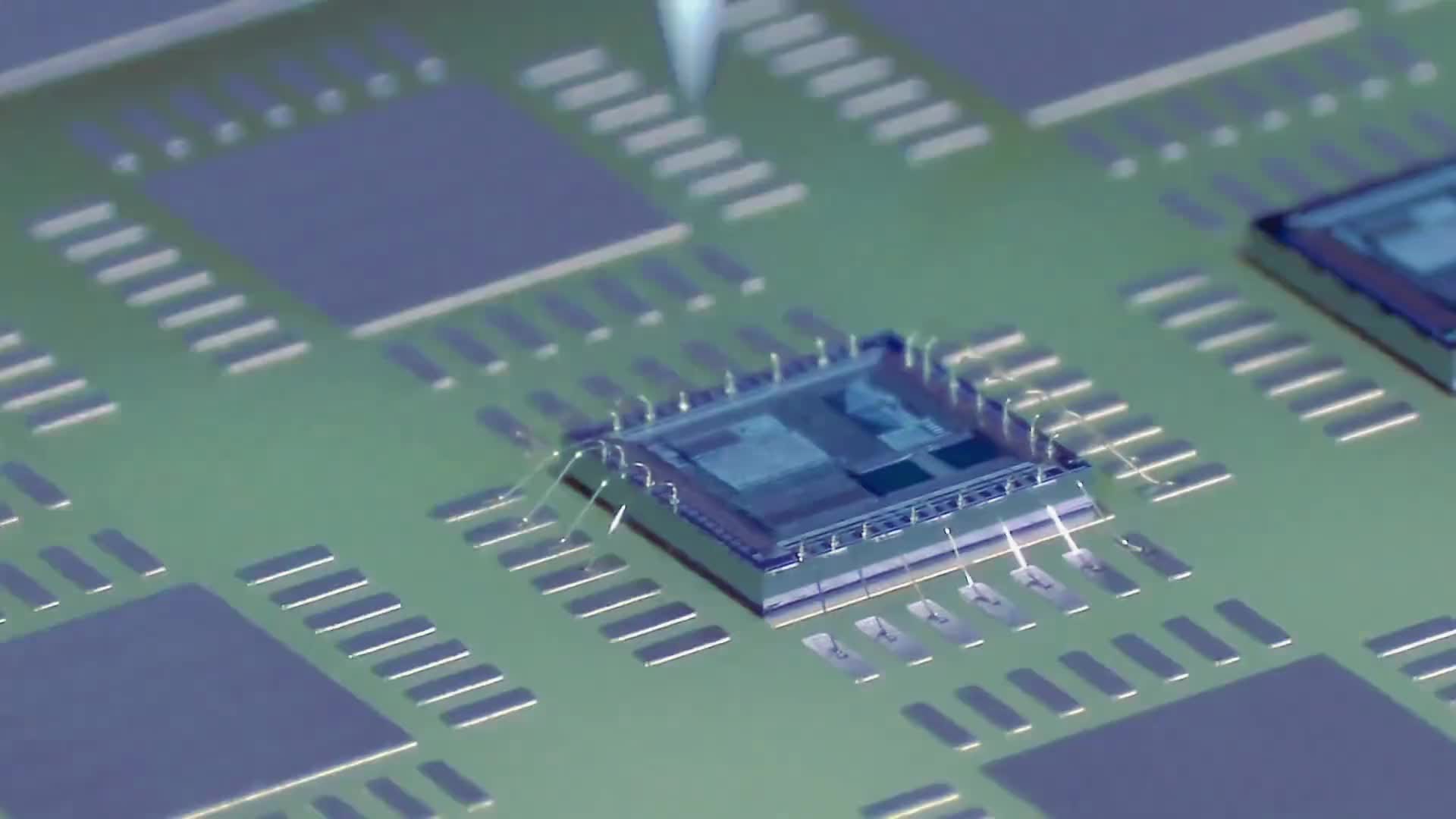

芯片進行封裝時,需利用金屬線材,將芯片(Chip)及導線架(Lead Frame)做連接,由于封裝時,可能有強度不足與污染的風險。此實驗目的,即為藉由打線拉力(Wire Bond Ppull)與推力

2018-09-27 16:22:26

(Wire Bond Shear)來驗證接合能力,確保其封裝可抵抗外在應力。iST宜特檢測可針對鋁線、金線、銅線進行試驗,線徑可小至0.8mil以下。參考規范MIL-STD-883 METHOD 2011.7JESD22-B116

2018-11-30 16:00:20

被壓縮,即使是在需要許多種供電電壓和實際輸出功率不斷增加的情況。先進的封裝形式,例如DaulCool NexFET功率MOSFET就有助于工程師在標準封裝中滿足這些需求。采用了NexFET技術的功率

2012-12-06 14:32:55

BGA封裝如何布線走線

2009-04-11 13:43:43

和基板介質間還要具有較高的粘附性能。 BGA封裝技術通常采用引線鍵合、等離子清洗、模塑封裝、裝配焊料球、回流焊等工藝流程。引線鍵合PBGA的封裝工藝流程包括PBGA基板的制備和封裝

2023-04-11 15:52:37

加速了對新型微電子封裝技術的研究與開發,諸如球形觸點陣列封裝(Ball grid array,簡稱BGA ) 技術,芯片尺寸封裝(Chipscalepackage,簡稱CSP) 技術,直接芯片鍵合

2015-10-21 17:40:21

純凈的金屬表面緊密接觸達到原子間的結合,從而形成焊接。主要焊接材料為鋁線焊頭,一般為楔形。 (3)金絲焊 球焊在引線鍵合中是最具代表性的焊接技術,因為現在的半導體封裝二、三極管封裝都采用AU線球焊

2018-09-11 15:27:57

90’s to 45’s ,把其他的勾都去掉,這樣進行優化時就不會將設計者故意彎曲的走線拉直或變形。二、Cadence 做封裝庫要注意些什么?做封裝既可以在Allegro中File-》New-

2019-05-21 10:11:28

文章目錄1、GPIO構件封裝方法與規范2、利用構件方法控制小燈閃爍3、工程文件組織框架與第一個C語言工程分析1、GPIO構件封裝方法與規范構件封裝建議、必要性與優點建議按底層硬件操作功能封裝構件

2021-11-08 06:58:21

MCM-L是采用片狀多層基板的MCM。MCM-L技術本來是高端有高密度封裝要求的PCB技術,適用于采用鍵合和FC工藝的MCM。MCM-L不適用有長期可靠性要求和使用環境溫差大的場合。

2020-03-19 09:00:46

MOSFET封裝伸援助之手 滿足芯片組移動新功能

2021-05-10 06:54:58

PADS如何畫蛇形走線元件封裝:比如用PADS畫一個引腳的藍牙天線或者2個引腳的天線,天線銅箔是蛇形走線的。

2020-07-30 10:06:57

PADS異形封裝,我想畫個封裝,想在封裝上用個2D線畫個小區域,讓這個小區域可以蓋綠油,我用阻焊層的2D線畫了還是不顯示阻焊層怎么辦?

2014-11-19 17:52:08

。人們希望防焊膜材料(液態或干膜)將其下面的電路元器件完全封裝,以保護其免受操作環境中各種侵蝕的影響。使用干膜防焊膜時為了達到這一目的,所選用的覆膜在壓合過程中必須能夠布滿電路上的所有焊墊和印制線,一

2013-02-25 11:37:02

樹脂),其組件符合工業規范要求。圖2 采用鍵合線的PQFN封裝圖3 采用銅片的PQFN封裝 例如,PQFN 5×6銅片封裝可在與現有SO-8相當的工業標準尺寸中,實現優于0.5mΩ的電阻,從裸片到

2018-09-12 15:14:20

線放入DBC襯底上的連接裝置中,從而形成完整的封裝。 除了Sn96.5-Ag3.5焊料外,還對SiN襯底上用于瞬態液相(TLP)鍵合工藝的另外兩種無鉛芯片粘接系統進行了研究。在鍵合過程中,通過互擴散

2018-09-11 16:12:04

存儲器控制器用戶指南列出了數據,地址,控制和時鐘信號的長度匹配要求。給出的數字是否必須補償FPGA和DDR2封裝內的鍵合線長度?如果是這樣,我在哪里可以找到這些長度?謝謝,TL以上來自于谷歌翻譯以下

2019-03-15 10:06:16

本帖最后由 eehome 于 2013-1-5 10:11 編輯

connex金線鍵合機編程

2012-05-19 09:03:56

印刷電路板上的半導體封裝。在大多數 BGA 中,半導體芯片和封裝基板是通過金線鍵合連接的。這些封裝基板和主板通過焊球連接。為了滿足這些連接所需的可靠性,封裝基板兩側的端子均鍍金。化學鍍金在更高

2021-07-09 10:29:30

的尺寸穩定性和低的吸潮性,具有較好的電氣性能和高可靠性。金屬薄膜、絕緣層和基板介質間還要具有較高的粘附性能。三大BGA封裝工藝及流程一、引線鍵合PBGA的封裝工藝流程1、PBGA基板的制備在BT樹脂

2018-09-18 13:23:59

芯片鍵合表面按柵陣形狀布置好焊料凸點后,芯片以倒扣方式安裝在封裝基板上,通過凸點與基板上的焊盤實現電氣連接,取代了WB和TAB 在周邊布置端子的連接方式。倒裝鍵合完畢后,在芯片與基板間用環氧樹脂進行

2017-09-18 11:34:51

無錫一家股份制企業,可以代工COB,陶瓷管殼、金屬封管殼和金屬陶瓷管殼等產品的封裝,具有貼片共晶焊/導電膠工藝、金絲/鋁絲鍵合、氣密非氣密封蓋、激光打標等能力,價格優惠,封裝評估的從下單到加工完成

2014-05-29 13:40:03

目前在做砷化鎵和磷化銦,在研究bongder和debonder工藝, 主要是超薄片很難處理,so暫定臨時鍵合解鍵合和薄片清洗流程,因為正面有保護可以做背面工藝,這里有前輩做過這個嗎?

2018-12-17 13:55:06

在剛剛使用軟件時經常要在封裝庫里面找需要的封裝找好久,今天給大家分享一個規范的 protel封裝命名參考,便于大家以后可以更加規范而且也更方便尋找所需的封裝。

2020-07-24 09:09:10

請教:最近在書上講解電感時提到一個名詞——鍵合線,望大家能給出通俗詳細解釋

2014-06-22 13:21:45

WLP的命名上還存在分歧。CSP晶片級技術非常獨特,封裝內部并沒有采用鍵合方式。封裝芯片的命名也存在分歧。常用名稱有:倒裝芯片(STMicroelectronics和Dalias

2018-08-27 15:45:31

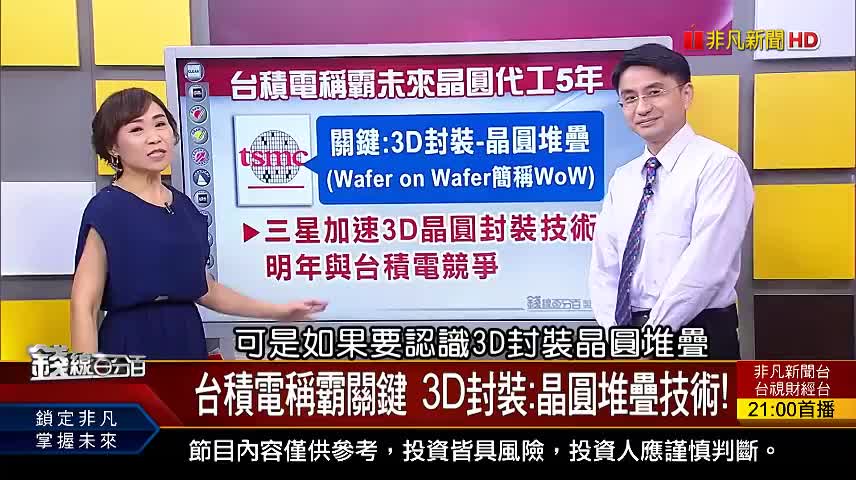

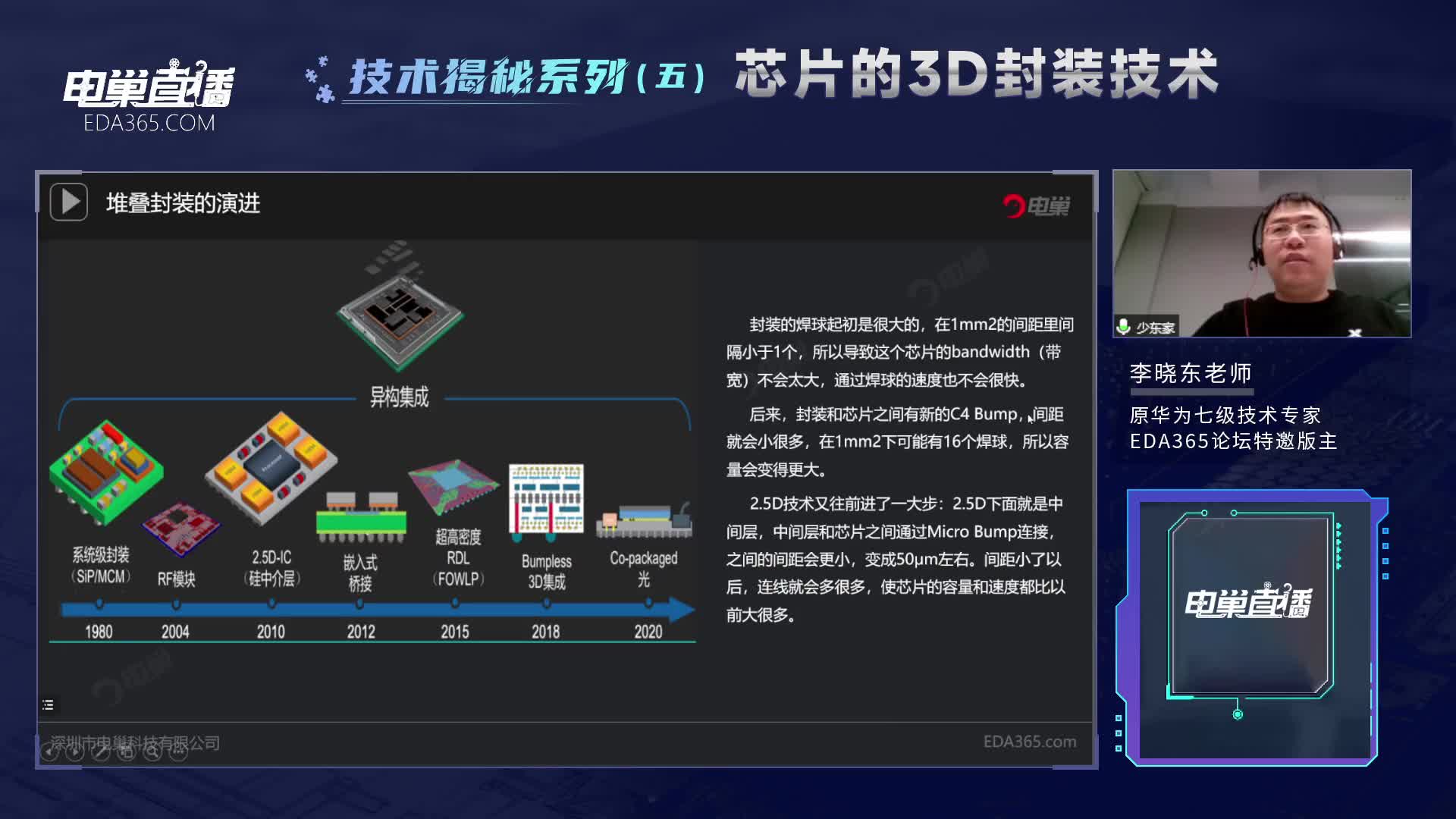

中芯片問的連接距離,持續縮小的封裝尺寸促使芯片三維重疊結構的運用,生產效率的提高需要把單個芯片的連接上藝擴展到整個硅片卜進行。硅片鍵合工藝把多層圓片上下相連同時形成電氣和機械連接以滿足這些要求。硅片

2018-11-23 17:03:35

而在鍵合引線和芯片底座上施加的載荷。進行塑封器件組裝時出現的爆米花現象就是一個典型的例子。綜合載荷應力條件在制造、組裝或者操作的過程中,諸如溫度和濕氣等失效加速因子常常是同時存在的。綜合載荷和應力條件常常會進一步加速失效。這一特點常被應用于以缺陷部件篩選和易失效封裝器件鑒別為目的的加速試驗設計。

2021-11-19 06:30:00

此文檔介紹了PCB的一些常用封裝的設計規范,共享

2018-06-08 11:16:52

分享一款不錯的優化遠程及遙測應用的視頻SERDES電路

2021-06-03 06:31:04

本帖最后由 知秋一葉03 于 2021-2-5 09:31 編輯

了解管腳焊盤,器件封裝的命名規范

2021-02-05 09:29:14

史上最全的PCB封裝命名規范

2017-11-27 17:23:32

史上最全的PCB封裝命名規范

2015-06-12 15:58:56

找了一圈,發現做線鍵合機的比較多,想知道做晶圓鍵合wafer bonding的中國廠家。

2021-04-28 14:34:57

在線監測導通電壓Von,以觀察引線鍵合點失效的后果并驗證檢測方法的可行性。圖12給出了在每個引線鍵合點被剝離后的半個調制周期內集電極電流Ion與Von的函數關系。這顯示了在不同電流值下,不同引線鍵合點

2019-03-20 05:21:33

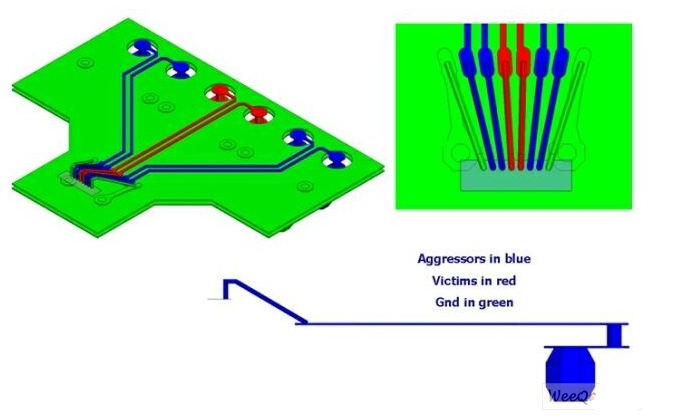

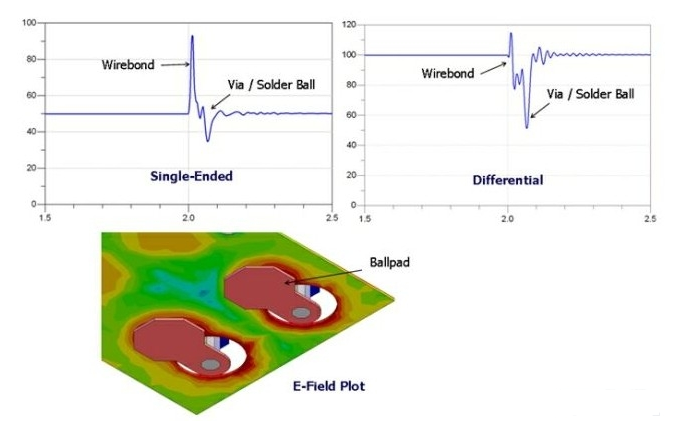

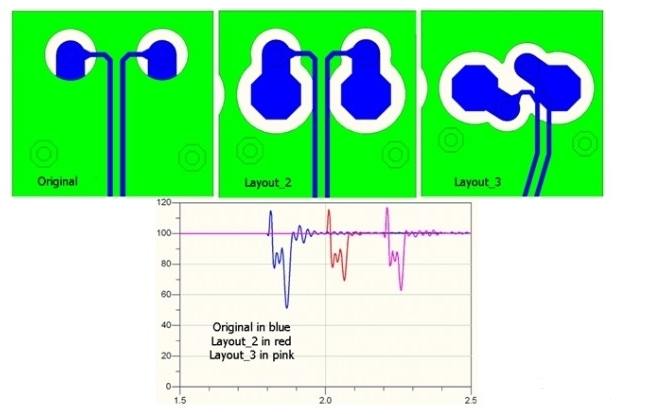

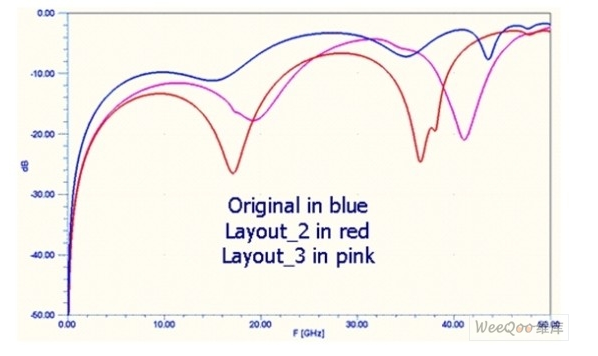

本文將討論通過優化封裝內的阻抗不連續性和改善其回波損耗性能,以滿足10Gbps SerDes鍵合線封裝規范。

2021-04-25 07:42:13

如何實現一體化芯片-封裝協同設計系統的設計?如何優化封裝和芯片接口設計?

2021-04-21 07:01:10

的距離之后,差分線的阻抗也隨之發生變化,需要調整差分走線滿足目標阻抗的要求。芯片的SMT焊盤距離參考平面距離變小之后阻抗也會變低,需要在SMT焊盤的參考平面上進行挖空處理來優化SMT焊盤的阻抗。具體挖空

2018-09-11 11:50:13

(參考APEC⒛00)。嵌入功率器件的平面金屬化封裝技術是其中較好的一種。 圖1 不用引線鍵合的集成功率模塊 圖2給出了一個集成模塊的剖面圖,應用了嵌入功率器件的多層集成封裝技術。包括:散熱板、基板、絕緣

2018-11-23 16:56:26

首先通過焊錫將芯片背部焊接在基板上,再通過金屬鍵合線引出正面電極,最后進行塑封或者灌膠。傳統封裝技術成熟,成本低,而且可兼容和替代原有 Si 基器件。 但是,傳統封裝結構導致其雜散電感參數較大,在

2023-02-22 16:06:08

論述了微電子封裝技術的發展歷程 發展現狀及發展趨勢 主要介紹了微電子封裝技術中的芯片級互聯技術與微電子裝聯技術 芯片級互聯技術包括引線鍵合技術 載帶自動焊技術 倒裝芯片技術 倒裝芯片技術是目前

2013-12-24 16:55:06

微電子封裝,首先我們要敘述一下三級封裝的概念。一般說來,微電子封裝分為三級。所謂一級封裝就是在半導體圓片裂片以后,將一個或多個集成電路芯片用適宜的封裝形式封裝起來,并使芯片的焊區與封裝的外引腳用引線鍵合

2018-09-12 15:15:28

有人又將其稱為圓片級-芯片尺寸封裝(WLP-CSP),以晶圓圓片為加工對象,在晶圓上封裝芯片。晶圓封裝中最關鍵的工藝為晶圓鍵合,即是通過化學或物理的方法將兩片晶圓結合在一起,以達到密封效果。如下

2021-02-23 16:35:18

滿足加速度大于30000g應用場景。

完成大尺寸QFN封裝金線鍵合工藝開發。

其它信息請加qq了解。(qq:972186757)

2024-03-10 14:14:51

。金絲焊也叫熱(壓)(超)聲焊主要鍵合材料為金(AU)線焊頭為球形故為球焊。 COB封裝流程 第一步:擴晶。采用擴張機將廠商提供的整張LED晶片薄膜均勻擴張,使附著在薄膜表面緊密排列的LED晶粒拉開

2018-09-17 17:12:09

貼膜(W-M)→晶圓表面去膜(WDP)→晶圓烘烤(WBK)→晶圓切割(SAW)→切割后清洗(DWC)→晶圓切割后檢查(PSI)→紫外線照射(U-V)→晶片粘結(DB)→銀膠固化(CRG)→引線鍵合(WB

2013-12-09 21:48:32

PCB的封裝是器件物料在PCB中的映射,封裝是否處理規范牽涉到器件的貼片裝配,我們需要正確的處理封裝數據,滿足實際生產的需求,有的工程師做的封裝無法滿足手工貼片,有的無法滿足機器貼片,也有的封裝

2023-04-17 16:53:30

;工藝設備復雜,成本,高,殼內零件較多易引起芯片沾污。引線鍵合技術本身存在諸多技術缺陷表現在:多根引線并聯會產生鄰近效應,導致同一硅片的鍵合線之間或同一模塊內的不同硅片的鍵合線之間電流分布不均;由于高頻

2018-08-28 11:58:28

硅-硅直接鍵合技術主要應用于SOI、MEMS和大功率器件,按照結構又可以分為兩大類:一類是鍵合襯底材料,包括用于高頻、抗輻射和VSIL的SOI襯底和用于大功率高壓器件的類外延的疏水鍵合N+-N-或

2018-11-23 11:05:56

硅襯底和砷化鎵襯底金金鍵合后,晶圓粉碎是什么原因,偶發性異常,找不出規律,有大佬清楚嗎,求助!

2023-03-01 14:54:11

微電子封裝,首先我們要敘述一下三級封裝的概念。一般說來,微電子封裝分為三級。所謂一級封裝就是在半導體圓片裂片以后,將一個或多個集成電路芯片用適宜的封裝形式封裝起來,并使芯片的焊區與封裝的外引腳用引線鍵合

2023-12-11 01:02:56

現在有哪些芯片是將IC與外圍電路做在一起的(封裝成一個IC)?同事說到后面會把晶振等較大的器件也會封裝進去,那這種IC在后面是不是一種大趨勢?如果是這樣,怎樣能保證匹配和性能,因為封裝到里,可能無法靠調整外圍電路優化,個人還不是太懂,請各位發表下自己的觀點幫忙了解些~~

2015-07-20 11:49:43

芯片封裝鍵合技術各種微互連方式簡介微互連技術簡介定義:將芯片凸點電極與載帶的引線連接,經過切斷、沖壓等工藝封裝而成。載帶:即帶狀載體,是指帶狀絕緣薄膜上載有由覆 銅箔經蝕刻而形成的引線框架,而且芯片

2012-01-13 14:58:34

芯片(Die)必須與構裝基板完成電路連接才能發揮既有的功能,焊線作業就是將芯片(Die)上的信號以金屬線鏈接到基板。iST宜特針對客戶在芯片打線封裝(Bonding, COB, Quick

2018-08-29 15:35:01

芯片封裝設計中的wire_bonding知識介紹Wire Bond/金線鍵合: 指在對芯片和基板間的膠粘劑處理以使其有更好的粘結性能后,用高純金線把芯片的接口和基板的接口鍵合 成分為金(純度為

2012-01-13 15:13:50

1、TAB技術中使用()線而不使用線,從而改善器件的熱耗散性能。A、鋁B、銅C、金D、銀2、陶瓷封裝基板的主要成分有()A、金屬B、陶瓷 C、玻璃D、高分子塑料3、“塑料封裝與陶瓷封裝技術均可以制成

2013-01-07 19:19:49

7系列系列中的SERDES是否有最小延遲規范?我想了解如果SERDES直接(最短路徑)連接到另一個SERDES以實現GTH收發器之間的最小延遲串行到串行連接,那將是什么樣的。

2020-07-22 13:45:34

是要實現電器和熱連接。我們應用IGBT過程中,導熱性是決定IGBT模塊最關鍵的因素。第二是鍵合,主要是通過鍵合線實現芯片與鍵合線之間的連接。第三是外殼安裝。第四是罐封,進行材料填充,事先與外界隔離

2012-09-17 19:22:20

介紹PCB封裝的命名規范,讓封裝庫有規律,易查詢。

2015-10-29 14:07:56 0

0 制作Altium Designer的封裝規范,包括原理圖和PCB圖的各種參數和必需尺寸等等。

2016-08-03 17:55:44 0

0 本文詳細介紹了元器件封裝的命名規則,對于規范封裝具有相當好的意義

2016-08-18 17:26:55 0

0 詳細介紹了各類元器件封裝設計規范要求,全面。

2016-08-29 16:05:01 0

0 PCB元件封裝設計規范,做封裝時有用

2016-12-16 21:20:06 0

0 基于_群封裝_技術的RADIUS認證優化_高寶

2017-03-19 11:31:31 0

0 對于10Gbps及以上數據速率的SerDes,每個數據位的單位間隔是隨著近 20~30ps的信號上升/下降時間而縮短的。

2018-07-18 17:18:48 7390

7390

幾乎每天都有小伙伴在后臺留言說想要 PCB 封裝設計的規范文檔,小編為了滿足大家,今天就給大家上菜了,希望大家喜歡,記得幫忙轉發,點贊哦,謝謝您。 器件封裝設計原則: 1、公司封裝庫中沒有的器件

2022-12-09 10:59:45 505

505 如果設計不合適,一個通道中的這些多重轉換將會影響信號完整性性能。在10Gbps及以上,通過最大限度地減少阻抗不連續性,得到適合的互連設計已成為提高系統性能的一個重要的考慮因素。由于封裝內有許多不連續區,該收發器封裝在提高回波損耗性能方面存在一個重要瓶頸。

2020-11-12 15:31:05 2606

2606

PCB的封裝是器件物料在PCB中的映射,封裝是否處理規范牽涉到器件的貼片裝配,我們需要正確的處理封裝數據,滿足實際生產的需求,有的工程師做的封裝無法滿足手工貼片,有的無法滿足機器貼片,也有的封裝

2021-01-21 11:27:06 8765

8765

適用于主流EDA工具的封裝命名規范,規范的命名可以提高審核效率,較少工程師犯錯。

2022-10-21 16:06:45 0

0 PCB 封裝命名規范注解 1. 命名中所涉及到的任何數據均由相應計算公式或規格書獲得 2. PCB 庫命名只涉及二維尺寸,封裝的高度 H 不做標注 3. 命名格式中字母含義解釋 [PKT

2022-12-09 10:40:09 0

0 自動化建模和優化112G封裝過孔 ——封裝Core層過孔和BGA焊盤區域的阻抗優化

2023-11-29 15:19:51 179

179

電子發燒友App

電子發燒友App

評論