一、印制板設(shè)計(jì)要求

1、正確

這是印制板設(shè)計(jì)基本、重要的要求,準(zhǔn)確實(shí)現(xiàn)電原理圖的連接關(guān)系,避免出現(xiàn)“短路”和“斷路”這兩個(gè)簡(jiǎn)單而致命的錯(cuò)誤。這一基本要求在手工設(shè)計(jì)和用簡(jiǎn)單CAD軟件設(shè)計(jì)的PCB中并不容易做到,一般的產(chǎn)品都要經(jīng)過兩輪以上試制修改,功能較強(qiáng)的CAD軟件則有檢驗(yàn)功能,可以保證電氣連接的正確性。

2、可靠

這是PCB 設(shè)計(jì)中較高一層的要求。連接正確的電路板不一定可靠性好,例如板材選擇不合理,板厚及安裝固定不正確,元器件布局布線不當(dāng)?shù)榷伎赡軐?dǎo)致PCB不能可靠地工作,早期失效甚至根本不能正確工作。再如多層板和單、雙面板相比,設(shè)計(jì)時(shí)要容易得多,但就可靠而言卻不如單、雙面板。從可靠性的角度講,結(jié)構(gòu)越簡(jiǎn)單,使用面越小,板子層數(shù)越少,可靠性越高。

3、合理

這是PCB 設(shè)計(jì)中更深一層,更不容易達(dá)到的要求。一個(gè)印制板組件,從印制板的制造、檢驗(yàn)、裝配、調(diào)試到整機(jī)裝配、調(diào)試,直到使用維修,無不與印制板的合理與否息息相關(guān),例如板子形狀選得不好加工困難,引線孔太小裝配困難,沒留試點(diǎn)高度困難,板外連接選擇不當(dāng)維修困難等等。每一個(gè)困難都可能導(dǎo)致成本增加,工時(shí)延長(zhǎng)。而每一個(gè)造成困難的原因都源于設(shè)計(jì)者的失誤。沒有合理的設(shè)計(jì),只有不斷合理化的過程。它需要設(shè)計(jì)者的責(zé)任心和嚴(yán)謹(jǐn)?shù)淖黠L(fēng),以及實(shí)踐中為斷總結(jié)、提高的經(jīng)驗(yàn)。

4、經(jīng)濟(jì)

這是一個(gè)不難達(dá)到、又不易達(dá)到,但必須達(dá)到的目標(biāo)。說“不難”,板材選低價(jià),板子尺寸盡量小,連接用直焊導(dǎo)線,表面涂覆用的,選擇價(jià)格的加工廠等等,印制板制造價(jià)格就會(huì)下降。但是不要忘記,這些廉價(jià)的選擇可能造成工藝性,可靠性變差,使制造費(fèi)用、維修費(fèi)用上升,總體經(jīng)濟(jì)性不一定分理處,因此說“不易”。“必須”則是市場(chǎng)競(jìng)爭(zhēng)的原則。競(jìng)爭(zhēng)是無情的,一個(gè)原理先進(jìn),技術(shù)高新的產(chǎn)品可能因?yàn)榻?jīng)濟(jì)性原因夭折。

體會(huì):

1、要有合理的走向:如輸入/輸出,交流/直流,強(qiáng)/弱信號(hào),高頻/低頻,高壓/低壓等,它們的走向應(yīng)該是呈線形的(或分離),不得相互交融。其目的是防止相互干擾。的走向是按直線,但一般不易實(shí)現(xiàn),不利的走向是環(huán)形,所幸的是可以設(shè)隔離帶來改善。對(duì)于是直流,小信號(hào),低電壓PCB設(shè)計(jì)的要求可以低些。所以“合理”是相對(duì)的。

2、選擇好接地點(diǎn):小小的接地點(diǎn)不知有多少工程技術(shù)人員對(duì)它做過多少論述,足見其重要性。一般情況下要求共點(diǎn)地,如:前向放大器的多條地線應(yīng)匯合后再與干線地相連等等。現(xiàn)實(shí)中,因受各種限制很難完全辦到,但應(yīng)盡力遵循。這個(gè)問題在實(shí)際中是相當(dāng)靈活的。每個(gè)人都有自己的一套解決方案。如能針對(duì)具體的電路板來解釋就容易理解。

3、合理布置電源濾波/退耦電容:一般在原理圖中僅畫出若干電源濾波/退耦電容,但未指出它們各自應(yīng)接于何處。其實(shí)這些電容是為開關(guān)器件(門電路)或其它需要濾波/退耦的部件而設(shè)置的,布置這些電容就應(yīng)盡量靠近這些元部件,離得太遠(yuǎn)就沒有作用了。有趣的是,當(dāng)電源濾波/退耦電容布置的合理時(shí),接地點(diǎn)的問題就顯得不那么明顯。

4、線條有講究:有條件做寬的線決不做細(xì);高壓及高頻線應(yīng)園滑,不得有尖銳的倒角,拐彎也不得采用直角。地線應(yīng)盡量寬,使用大面積敷銅,這對(duì)接地點(diǎn)問題有相當(dāng)大的改善。

5、有些問題雖然發(fā)生在后期制作中,但卻是PCB設(shè)計(jì)中帶來的,它們是:過線孔太多,沉銅工藝稍有不慎就會(huì)埋下隱患。所以,設(shè)計(jì)中應(yīng)盡量減少過線孔。同向并行的線條密度太大,焊接時(shí)很容易連成一片。所以,線密度應(yīng)視焊接工藝的水平來確定。 焊點(diǎn)的距離太小,不利于人工焊接,只能以降低工效來解決焊接質(zhì)量。否則將留下隱患。所以,焊點(diǎn)的距離的確定應(yīng)綜合考慮焊接人員的素質(zhì)和工效。焊盤或過線孔尺寸太小,或焊盤尺寸與鉆孔尺寸配合不當(dāng)。前者對(duì)人工鉆孔不利,后者對(duì)數(shù)控鉆孔不利。容易將焊盤鉆成“c”形,重則鉆掉焊盤。導(dǎo)線太細(xì),而大面積的未布線區(qū)又沒有設(shè)置敷銅,容易造成腐蝕不均勻。即當(dāng)未布線區(qū)腐蝕完后,細(xì)導(dǎo)線很有可能腐蝕過頭,或似斷非斷,或完全斷。所以,設(shè)置敷銅的作用不僅僅是增大地線面積和抗干擾。

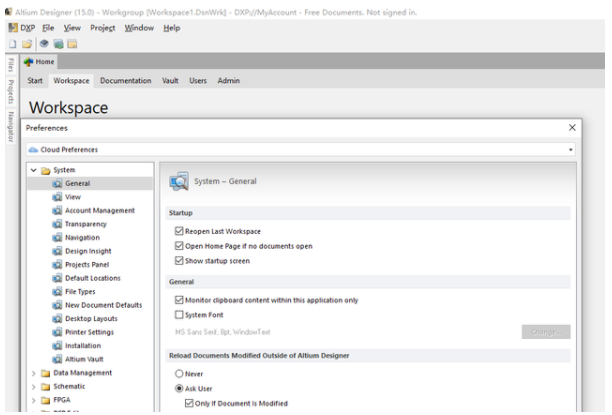

二、Protel 打印設(shè)置

SCH的打印設(shè)置較簡(jiǎn)單,在Margins的Top Bottom Left Right內(nèi)全填上0然后點(diǎn)擊Refresh,這樣就能范圍的占用頁(yè)面,使打印出的SCH圖更大些。

PCB的設(shè)置:打開File》Setup Printer…進(jìn)行打印前的設(shè)置。

在彈出的Printer Setup菜單中,要先選擇您的打印機(jī):幾個(gè)是默認(rèn)的打印機(jī),后面兩個(gè)是我們安裝了的打印機(jī),(我的機(jī)子上是這樣)兩個(gè)中一個(gè)后綴為Final,一個(gè)是Composite,前一個(gè)的意思是打印機(jī)只打印一個(gè)層(不管您選了幾個(gè)層,只是分幾次打印而已),后一個(gè)是打印所有你選中的層面,根據(jù)需要自己選擇!下一步:點(diǎn)擊下方的Options按鈕,進(jìn)行屬性設(shè)置。假設(shè)我們選final然后進(jìn)入Options進(jìn)行設(shè)置,進(jìn)入后的選項(xiàng)一般不用動(dòng),Scale為打印比例,默認(rèn)的為1:1,如果想滿頁(yè)打印,就將那個(gè)小框打上鉤,哦!右邊的Show Hole蠻重要,選中他就可以把電路板上的孔打印出來(做光刻板就要選這個(gè),有幫助),好了,點(diǎn)擊Setup進(jìn)行紙張大小設(shè)置就完成了打印機(jī) Options。還沒完呢!麻煩把!回到選打印機(jī)屬性的對(duì)話框,選擇Layers,進(jìn)行打印層的設(shè)置,進(jìn)去以后,看見了吧!是不是很熟悉呢!根據(jù)自己需要選擇吧。

三、常用的PCB庫(kù)文件

1.librarypcbconnectors目錄下的元件數(shù)據(jù)庫(kù)所含的元件庫(kù)含有絕大部分接插件元件的PCB封裝

1).D type connectors.ddb,含有并口,串口類接口元件的封裝

2).headers.ddb:含有各種插頭元件的封裝

2.librarypcbgeneric footprints目錄下的數(shù)據(jù)庫(kù)所含的元件庫(kù)含有絕大部分的普通元件的PCB封狀

1).general ic.ddb,含有CFP,DIP,JEDECA,LCC,DFP,ILEAD,SOCKET,PLCC系列以及表面貼裝電阻,電容等元件封裝

2).international rectifiers.ddb,含有IR公司的整流橋,二極管等常用元件的封裝

3).Miscellaneous.ddb,含有電阻,電容,二極管等的封裝

4).PGA.ddb,含有PGA封裝

5).Transformers.ddb,含有變壓器元件的封裝

6).Transistors.ddb含有晶體管元件的封裝

3.librarypcbIPC footprints目錄下的元件數(shù)據(jù)庫(kù)所含的元件庫(kù)中有絕大部分的表面帖裝元件的封裝

四、PCB及電路抗干擾措施

印制電路板的抗干擾設(shè)計(jì)與具體電路有著密切的關(guān)系,這里僅就PCB抗干擾設(shè)計(jì)的幾項(xiàng)常用措施做一些說明。

1.電源線設(shè)計(jì)

根據(jù)印制線路板電流的大小,盡量加租電源線寬度,減少環(huán)路電阻。同時(shí)、使電源線、地線的走向和數(shù)據(jù)傳遞的方向一致,這樣有助于增強(qiáng)抗噪聲能力。

2.地線設(shè)計(jì)的原則

(1)數(shù)字地與模擬地分開。若線路板上既有邏輯電路又有線性電路,應(yīng)使它們盡量分開。低頻電路的地應(yīng)盡量采用單點(diǎn)并聯(lián)接地,實(shí)際布線有困難時(shí)可部分串聯(lián)后再并聯(lián)接地。高頻電路宜采用多點(diǎn)串聯(lián)接地,地線應(yīng)短而租,高頻元件周圍盡量用柵格狀大面積地箔。

(2)接地線應(yīng)盡量加粗。若接地線用很紉的線條,則接地電位隨電流的變化而變化,使抗噪性能降低。因此應(yīng)將接地線加粗,使它能通過三倍于印制板上的允許電流。如有可能,接地線應(yīng)在2~3mm以上。

(3)接地線構(gòu)成閉環(huán)路。只由數(shù)字電路組成的印制板,其接地電路布成團(tuán)環(huán)路大多能提高抗噪聲能力。

3.退藕電容配置

PCB設(shè)計(jì)的常規(guī)做法之一是在印制板的各個(gè)關(guān)鍵部位配置適當(dāng)?shù)耐伺弘娙荨M伺弘娙莸囊话闩渲迷瓌t是:

(1)電源輸入端跨接10~100uf的電解電容器。如有可能,接100uF以上的更好。

(2)原則上每個(gè)集成電路芯片都應(yīng)布置一個(gè)0.01pF的瓷片電容,如遇印制板空隙不夠,可每4~8個(gè)芯片布置一個(gè)1~10pF的鉭電容。

(3)對(duì)于抗噪能力弱、關(guān)斷時(shí)電源變化大的器件,如RAM、ROM存儲(chǔ)器件,應(yīng)在芯片的電源線和地線之間直接接入退藕電容。

(4)電容引線不能太長(zhǎng),尤其是高頻旁路電容不能有引線。

(5)在印制板中有接觸器、繼電器、按鈕等元件時(shí).操作它們時(shí)均會(huì)產(chǎn)生較大火花放電,必須采用RC電路來吸收放電電流。一般R取1~2K,C取2.2~47UF。

(6) CMOS的輸入阻抗很高,且易受感應(yīng),因此在使用時(shí)對(duì)不用端要接地或接正電源。

五、PCB布線原則

在PCB設(shè)計(jì)中,布線是完成產(chǎn)品設(shè)計(jì)的重要步驟,可以說前面的準(zhǔn)備工作都是為它而做的,在整個(gè)PCB中,以布線的設(shè)計(jì)過程限定,技巧細(xì)、工作量。PCB布線有單面布線、 雙面布線及多層布線。布線的方式也有兩種:自動(dòng)布線及交互式布線,在自動(dòng)布線之前,可以用交互式預(yù)先對(duì)要求比較嚴(yán)格的線進(jìn)行布線,輸入端與輸出端的邊線應(yīng)避免相鄰平行, 以免產(chǎn)生反射干擾。必要時(shí)應(yīng)加地線隔離,兩相鄰層的布線要互相垂直,平行容易產(chǎn)生寄生耦合。

自動(dòng)布線的布通率,依賴于良好的布局,布線規(guī)則可以預(yù)先設(shè)定, 包括走線的彎曲次數(shù)、導(dǎo)通孔的數(shù)目、步進(jìn)的數(shù)目等。一般先進(jìn)行探索式布經(jīng)線,快速地把短線連通,然后進(jìn)行迷宮式布線,先把要布的連線進(jìn)行全局的布線路徑優(yōu)化,它可以根據(jù)需要斷開已布的線。 并試著重新再布線,以改進(jìn)總體效果。

對(duì)目前高密度的PCB設(shè)計(jì)已感覺到貫通孔不太適應(yīng)了, 它浪費(fèi)了許多寶貴的布線通道,為解決這一矛盾,出現(xiàn)了盲孔和埋孔技術(shù),它不僅完成了導(dǎo)通孔的作用,還省出許多布線通道使布線過程完成得更加方便,更加流暢,更為完善,PCB 板的設(shè)計(jì)過程是一個(gè)復(fù)雜而又簡(jiǎn)單的過程,要想很好地掌握它,還需廣大電子工程設(shè)計(jì)人員去自已體會(huì),才能得到其中的真諦。

1 、電源、地線的處理

既使在整個(gè)PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會(huì)使產(chǎn)品的性能下降,有時(shí)甚至影響到產(chǎn)品的成功率。所以對(duì)電源、地線的布線要認(rèn)真對(duì)待,把電源、地線所產(chǎn)生的噪音干擾降到限度,以保證產(chǎn)品的質(zhì)量。

對(duì)每個(gè)從事電子產(chǎn)品設(shè)計(jì)的工程人員來說都明白地線與電源線之間噪音所產(chǎn)生的原因,現(xiàn)只對(duì)降低式抑制噪音作以表述:

眾所周知的是在電源、地線之間加上去耦電容。

盡量加寬電源、地線寬度,是地線比電源線寬,它們的關(guān)系是:地線>電源線>信號(hào)線,通常信號(hào)線寬為:0.2~0.3mm,經(jīng)細(xì)寬度可達(dá)0.05~0.07mm,電源線為1.2~2.5 mm

對(duì)數(shù)字電路的PCB可用寬的地導(dǎo)線組成一個(gè)回路, 即構(gòu)成一個(gè)地網(wǎng)來使用(模擬電路的地不能這樣使用)

用大面積銅層作地線用,在印制板上把沒被用上的地方都與地相連接作為地線用。或是做成多層板,電源,地線各占用一層。

2、數(shù)字電路與模擬電路的共地處理

現(xiàn)在有許多PCB不再是單一功能電路(數(shù)字或模擬電路),而是由數(shù)字電路和模擬電路混合構(gòu)成的。因此在布線時(shí)就需要考慮它們之間互相干擾問題,特別是地線上的噪音干擾。

數(shù)字電路的頻率高,模擬電路的敏感度強(qiáng),對(duì)信號(hào)線來說,高頻的信號(hào)線盡可能遠(yuǎn)離敏感的模擬電路器件,對(duì)地線來說,整人PCB 對(duì)外界只有一個(gè)結(jié)點(diǎn),所以必須在PCB內(nèi)部進(jìn)行處理數(shù)、模共地的問題,而在板內(nèi)部數(shù)字地和模擬地實(shí)際上是分開的它們之間互不相連,只是在PCB與外界連接的接口處(如插頭等)。數(shù)字地與模擬地有一點(diǎn)短接,請(qǐng)注意,只有一個(gè)連接點(diǎn)。也有在PCB上不共地的,這由系統(tǒng)設(shè)計(jì)來決定。

3、信號(hào)線布在電(地)層上

在多層印制板布線時(shí),由于在信號(hào)線層沒有布完的線剩下已經(jīng)不多,再多加層數(shù)就會(huì)造成浪費(fèi)也會(huì)給生產(chǎn)增加一定的工作量,成本也相應(yīng)增加了,為解決這個(gè)矛盾,可以考慮在電(地)層上進(jìn)行布線。首先應(yīng)考慮用電源層,其次才是地層。因?yàn)槭潜A舻貙拥耐暾浴?/p>

4、大面積導(dǎo)體中連接腿的處理

在大面積的接地(電)中,常用元器件的腿與其連接,對(duì)連接腿的處理需要進(jìn)行綜合的考慮,就電氣性能而言,元件腿的焊盤與銅面滿接為好,但對(duì)元件的焊接裝配就存在一些不良隱患如:①焊接需要大功率加熱器。②容易造成虛焊點(diǎn)。所以兼顧電氣性能與工藝需要,做成十字花焊盤,稱之為熱隔離(heat shield)俗稱熱焊盤(Thermal),這樣,可使在焊接時(shí)因截面過分散熱而產(chǎn)生虛焊點(diǎn)的可能性大大減少。多層板的接電(地)層腿的處理相同。

5、布線中網(wǎng)絡(luò)系統(tǒng)的作用

在許多CAD系統(tǒng)中,布線是依據(jù)網(wǎng)絡(luò)系統(tǒng)決定的。網(wǎng)格過密,通路雖然有所增加,但步進(jìn)太小,圖場(chǎng)的數(shù)據(jù)量過大,這必然對(duì)設(shè)備的存貯空間有更高的要求,同時(shí)也對(duì)象計(jì)算機(jī)類電子產(chǎn)品的運(yùn)算速度有極大的影響。而有些通路是無效的,如被元件腿的焊盤占用的或被安裝孔、定們孔所占用的等。網(wǎng)格過疏,通路太少對(duì)布通率的影響極大。所以要有一個(gè)疏密合理的網(wǎng)格系統(tǒng)來支持布線的進(jìn)行。

標(biāo)準(zhǔn)元器件兩腿之間的距離為0.1英寸(2.54mm),所以網(wǎng)格系統(tǒng)的基礎(chǔ)一般就定為0.1英寸(2.54 mm)或小于0.1英寸的整倍數(shù),如:0.05英寸、0.025英寸、0.02英寸等。

6、設(shè)計(jì)規(guī)則檢查(DRC)

布線設(shè)計(jì)完成后,需認(rèn)真檢查布線設(shè)計(jì)是否符合設(shè)計(jì)者所制定的規(guī)則,同時(shí)也需確認(rèn)所制定的規(guī)則是否符合印制板生產(chǎn)工藝的需求,一般檢查有如下幾個(gè)方面:

線與線,線與元件焊盤,線與貫通孔,元件焊盤與貫通孔,貫通孔與貫通孔之間的距離是否合理,是否滿足生產(chǎn)要求。

電源線和地線的寬度是否合適,電源與地線之間是否緊耦合(低的波阻抗)?在PCB中是否還有能讓地線加寬的地方。

對(duì)于關(guān)鍵的信號(hào)線是否采取了措施,如長(zhǎng)度短,加保護(hù)線,輸入線及輸出線被明顯地分開。

模擬電路和數(shù)字電路部分,是否有各自獨(dú)立的地線。

后加在PCB中的圖形(如圖標(biāo)、注標(biāo))是否會(huì)造成信號(hào)短路。

對(duì)一些不理想的線形進(jìn)行修改。

在PCB上是否加有工藝線?阻焊是否符合生產(chǎn)工藝的要求,阻焊尺寸是否合適,字符標(biāo)志是否壓在器件焊盤上,以免影響電裝質(zhì)量。

多層板中的電源地層的外框邊緣是否縮小,如電源地層的銅箔露出板外容易造成短路。

六、關(guān)于濾波

濾波技術(shù)是抑制干擾的一種有效措施,尤其是在對(duì)付開關(guān)電源EMI信號(hào)的傳導(dǎo)干擾和某些輻射干擾方面,具有明顯的效果。

任何電源線上傳導(dǎo)干擾信號(hào),均可用差模和共模干擾信號(hào)來表示。

差模干擾在兩導(dǎo)線之間傳輸,屬于對(duì)稱性干擾;共模干擾在導(dǎo)線與地(機(jī)殼)之間傳輸,屬于非對(duì)稱性干擾。在一般情況下,差模干擾幅度小、頻率低、所造成的干擾較小,共模干擾幅度大、頻率高,還可以通過導(dǎo)線產(chǎn)生輻射,所造成的干擾較大。因此,欲削弱傳導(dǎo)干擾,把EMI信號(hào)控制在有關(guān)EMC標(biāo)準(zhǔn)規(guī)定的極限電平以下。除抑制干擾源以外,有效的方法就是在開關(guān)源輸入和輸出電路中加裝EMI濾波器。一般設(shè)備的工作頻率約為10~50 kHz。EMC很多標(biāo)準(zhǔn)規(guī)定的傳導(dǎo)干擾電平的極限值都是從10 kHz算起。對(duì)開關(guān)電源產(chǎn)生的高頻段EMI信號(hào),只要選擇相應(yīng)的去耦電路或網(wǎng)絡(luò)結(jié)構(gòu)較為簡(jiǎn)單的EMI濾波器,就不難滿足符合EMC標(biāo)準(zhǔn)的濾波效果。

1 .1瞬態(tài)干擾

是指交流電網(wǎng)上出現(xiàn)的浪涌電壓、振鈴電壓、火花放電等瞬間干擾信號(hào),其特點(diǎn)是作用時(shí)間極短,但電壓幅度高、瞬態(tài)能量大。瞬態(tài)干擾會(huì)造成單片開關(guān)電源輸出電壓的波動(dòng);當(dāng)瞬態(tài)電壓疊加在整流濾波后的直流輸入電壓VI上,使VI超過內(nèi)部功率開關(guān)管的漏-源擊穿電壓V(BR)DS時(shí),還會(huì)損壞TOPSwitch芯片,因此必須采用抑制措施。通常,靜電放電(ESD)和電快速瞬變脈沖群(EFT)對(duì)數(shù)字電路的危害甚于其對(duì)模擬電路的影響。靜電放電在5 — 200MHz的頻率范圍內(nèi)產(chǎn)生強(qiáng)烈的射頻輻射。此輻射能量的峰值經(jīng)常出現(xiàn)在35MHz — 45MHz之間發(fā)生自激振蕩。許多I/O電纜的諧振頻率也通常在這個(gè)頻率范圍內(nèi),結(jié)果,電纜中便串入了大量的靜電放電輻射能量。當(dāng)電纜暴露在4 — 8kV靜電放電環(huán)境中時(shí),I/O電纜終端負(fù)載上可以測(cè)量到的感應(yīng)電壓可達(dá)到600V。這個(gè)電壓遠(yuǎn)遠(yuǎn)超出了典型數(shù)字的門限電壓值0.4V。典型的感應(yīng)脈沖持續(xù)時(shí)間大約為400納秒。將I/O電纜屏蔽起來,且將其兩端接地,使內(nèi)部信號(hào)引線全部處于屏蔽層內(nèi),可以將干擾減小60 — 70dB,負(fù)載上的感應(yīng)電壓只有0.3V或更低。電快速瞬變脈沖群也產(chǎn)生相當(dāng)強(qiáng)的輻射發(fā)射,從而耦合到電纜和機(jī)殼線路。電源線濾波器可以對(duì)電源進(jìn)行保護(hù)。線 — 地之間的共模電容是抑制這種瞬態(tài)干擾的有效器件,它使干擾旁路到機(jī)殼,而遠(yuǎn)離內(nèi)部電路。當(dāng)這個(gè)電容的容量受到泄漏電流的限制而不能太大時(shí),共模扼流圈必須提供更大的保護(hù)作用。這通常要求使用專門的帶中心抽頭的共模扼流圈,中心抽頭通過一只電容(容量由泄漏電流決定)連接到機(jī)殼。共模扼流圈通常繞在高導(dǎo)磁率鐵氧體芯上,其典型電感值為15 ~ 20mH。

1.2傳導(dǎo)的抑制

往往單純采用屏蔽不能提供完整的電磁干擾防護(hù),因?yàn)樵O(shè)備或系統(tǒng)上的電纜才是有效的干擾接收與發(fā)射天線。許多設(shè)備單臺(tái)做電磁兼容實(shí)驗(yàn)時(shí)都沒有問題,但當(dāng)兩臺(tái)設(shè)備連接起來以后,就不滿足電磁兼容的要求了,這就是電纜起了接收和輻射天線的作用。的措施就是加濾波器,切斷電磁干擾沿信號(hào)線或電源線傳播的路徑,與屏蔽共同夠成完善的電磁干擾防護(hù),無論是抑制干擾源、消除耦合或提高接收電路的抗能力,都可以采用濾波技術(shù)。針對(duì)不同的干擾,應(yīng)采取不同的抑制技術(shù),由簡(jiǎn)單的線路清理,至單個(gè)元件的干擾抑制器、濾波器和變壓器,再至比較復(fù)雜的穩(wěn)壓器和凈化電源,以及價(jià)格昂貴而性能完善的不間斷電源,下面分別作簡(jiǎn)要敘述。

1.3 專用線路

只要通過對(duì)供電線路的簡(jiǎn)單清理就可以取得一定的干擾抑制效果。如在三相供電線路中認(rèn)定一相作為干擾敏感設(shè)備的供電電源;以另一相作為外部設(shè)備的供電電源;再以一相作為常用測(cè)試儀器或其他輔助設(shè)備的供電電源。這樣的處理可避免設(shè)備間的一些相互干擾,也有利于三相平衡。值得一提的是在現(xiàn)代電子設(shè)備系統(tǒng)中,由于配電線路中非線性負(fù)載的使用,造成線路中諧波電流的存在,而零序分量諧波在中線里不能相互抵消,反而是疊加,因此過于纖細(xì)的中線會(huì)造成線路阻抗的增加,干擾也將增加。同時(shí)過細(xì)的中線還會(huì)造成中線過熱。

1.4 瞬變干擾抑制器

屬瞬變干擾抑制器的有氣體放電管、金屬氧化物壓敏電阻、硅瞬變吸收二極管和固體放電管等多種。其中金屬氧化物壓敏電阻和硅瞬變吸收二極管的工作有點(diǎn)象普通的穩(wěn)壓管,是箝位型的干擾吸收器件;而氣體放電管和固體放電管是能量轉(zhuǎn)移型干擾吸收器件(以氣體放電管為例,當(dāng)出現(xiàn)在放電管兩端的電壓超過放電管的著火電壓時(shí),管內(nèi)的氣體發(fā)生電離,在兩電極間產(chǎn)生電弧。由于電弧的壓降很低,使大部分瞬變能量得以轉(zhuǎn)移,從而保護(hù)設(shè)備免遭瞬變電壓破壞)。瞬變干擾抑制器與被保護(hù)設(shè)備并聯(lián)使用。

1.5氣體放電管

氣體放電管也稱避雷管,目前常用于程控交換機(jī)上。避雷管具有很強(qiáng)的浪涌吸收能力,很高的絕緣電阻和很小的寄生電容,對(duì)正常工作的設(shè)備不會(huì)帶來任何有害影響。但它對(duì)浪涌的起弧響應(yīng),與對(duì)直流電壓的起弧響應(yīng)之間存在很大差異。例如90V氣體放電管對(duì)直流的起弧電壓就是90V,而對(duì)5kV/μs的浪涌起弧電壓值可能達(dá)到1000V。這表明氣體放電管對(duì)浪涌電壓的響應(yīng)速度較低。故它比較適合作為線路和設(shè)備的保護(hù)。此外,氣體放電管的電壓檔次很少。

1.6金屬氧化物壓敏電阻

由于價(jià)廉,壓敏電阻是目前廣泛應(yīng)用的瞬變干擾吸收器件。描述壓敏電阻性能的主要參數(shù)是壓敏電阻的標(biāo)稱電壓和通流容量即浪涌電流吸收能力。前者是使用者經(jīng)常易弄混淆的一個(gè)參數(shù)。壓敏電阻標(biāo)稱電壓是指在恒流條件下(外徑為7mm以下的壓敏電阻取0.1mA;7mm以上的取1mA)出現(xiàn)在壓敏電阻兩端的電壓降。由于壓敏電阻有較大的動(dòng)態(tài)電阻,在規(guī)定形狀的沖擊電流下(通常是8/20μs的標(biāo)準(zhǔn)沖擊電流)出現(xiàn)在壓敏電阻兩端的電壓(亦稱是限制電壓)大約是壓敏電阻標(biāo)稱電壓的1.8~2倍(此值也稱殘壓比)。這就要求使用者在選擇壓敏電阻時(shí)事先有所估計(jì),對(duì)確有可能遇到較大沖擊電流的場(chǎng)合,應(yīng)選擇使用外形尺寸較大的器件(壓敏電阻的電流吸收能力正比于器件的通流面積,耐受電壓正比于器件厚度,而吸收能量正比于器件體積)。使用壓敏電阻要注意它的固有電容。根據(jù)外形尺寸和標(biāo)稱電壓的不同,電容量在數(shù)千至數(shù)百pF之間,這意味著壓敏電阻不適宜在高頻場(chǎng)合下使用,比較適合于在工頻場(chǎng)合,如作為晶閘管和電源進(jìn)線處作保護(hù)用。特別要注意的是,壓敏電阻對(duì)瞬變干擾吸收時(shí)的高速性能(達(dá)ns)級(jí),故安裝壓敏電阻必須注意其引線的感抗作用,過長(zhǎng)的引線會(huì)引入由于引線電感產(chǎn)生的感應(yīng)電壓(在示波器上,感應(yīng)電壓呈尖刺狀)。引線越長(zhǎng),感應(yīng)電壓也越大。為取得滿意的干擾抑制效果,應(yīng)盡量縮短其引線。關(guān)于壓敏電阻的電壓選擇,要考慮被保護(hù)線路可能有的電壓波動(dòng)(一般取1.2~1.4倍)。如果是交流電路,還要注意電壓有效值與峰值之間的關(guān)系。所以對(duì) 220V線路,所選壓敏電阻的標(biāo)稱電壓應(yīng)當(dāng)是220×1.4×1.4≈430V。此外,就壓敏電阻的電流吸收能力來說,1kA(對(duì)8/20μs的電流波)用在晶閘管保護(hù)上,3kA用在電器設(shè)備的浪涌吸收上;5kA用在雷擊及電子設(shè)備的過壓吸收上;10kA用在雷擊保護(hù)上。壓敏電阻的電壓檔次較多,適合作設(shè)備的或二次保護(hù)。

1.7硅瞬變電壓吸收二極管(TVS管)

硅瞬變電壓吸收二極管具有極快的響應(yīng)時(shí)間(亞納秒級(jí))和相當(dāng)高的浪涌吸收能力,及極多的電壓檔次。可用于保護(hù)設(shè)備或電路免受靜電、電感性負(fù)載切換時(shí)產(chǎn)生的瞬變電壓,以及感應(yīng)雷所產(chǎn)生的過電壓。 TVS管有單方向(單個(gè)二極管)和雙方向(兩個(gè)背對(duì)背連接的二極管)兩種,它們的主要參數(shù)是擊穿電壓、漏電流和電容。使用中TVS管的擊穿電壓要比被保護(hù)電路工作電壓高10%左右,以防止因線路工作電壓接近TVS擊穿電壓,使TVS漏電流影響電路正常工作;也避免因環(huán)境溫度變化導(dǎo)致TVS管擊穿電壓落入線路正常工作電壓的范圍。 TVS管有多種封裝形式,如軸向引線產(chǎn)品可用在電源饋線上;雙列直插的和表面貼裝的適合于在印刷板上作為邏輯電路、I/O總線及數(shù)據(jù)總線的保護(hù)。 TVS管在使用中應(yīng)注意的事項(xiàng): ·對(duì)瞬變電壓的吸收功率(峰值)與瞬變電壓脈沖寬度間的關(guān)系。手冊(cè)給的只是特定脈寬下的吸收功率(峰值),而實(shí)際線路中的脈沖寬度則變化莫測(cè),事前要有估計(jì)。對(duì)寬脈沖應(yīng)降額使用。 ·對(duì)小電流負(fù)載的保護(hù),可有意識(shí)地在線路中增加限流電阻,只要限流電阻的阻值適當(dāng),不會(huì)影響線路的正常工作,但限流電阻對(duì)干擾所產(chǎn)生的電流卻會(huì)大大減小。這就有可能選用峰值功率較小的TVS管來對(duì)小電流負(fù)載線路進(jìn)行保護(hù)。 ·對(duì)重復(fù)出現(xiàn)的瞬變電壓的抑制,尤其值得注意的是TVS管的穩(wěn)態(tài)平均功率是否在安全范圍之內(nèi)。 ·作為半導(dǎo)體器件的TVS管,要注意環(huán)境溫度升高時(shí)的降額使用問題。 ·特別要注意TVS管的引線長(zhǎng)短,以及它與被保護(hù)線路的相對(duì)距離。 ·當(dāng)沒有合適電壓的TVS管供采用時(shí),允許用多個(gè)TVS管串聯(lián)使用。串聯(lián)管的電流決定于所采用管中電流吸收能力的一個(gè)。而峰值吸收功率等于這個(gè)電流與串聯(lián)管電壓之和的乘積。 ·TVS管的結(jié)電容是影響它在高速線路中使用的關(guān)鍵因素,在這種情況下,一般用一個(gè)TVS管與一個(gè)快恢復(fù)二極管以背對(duì)背的方式連接,由于快恢復(fù)二極管有較小的結(jié)電容,因而二者串聯(lián)的等效電容也較小,可滿足高頻使用的要求。 ·固體放電管 固體放電管是一種較新的瞬變干擾吸收器件,具有響應(yīng)速度較快(10~20ns級(jí))、吸收電流較大、動(dòng)作電壓穩(wěn)定和使用壽命長(zhǎng)等特點(diǎn)。固體放電管與氣體放電管同屬能量轉(zhuǎn)移型。圖2.2為其伏安特性。當(dāng)外界干擾低于觸發(fā)電壓時(shí),管子呈截止?fàn)睢R坏└蓴_超出觸發(fā)電壓時(shí),伏安特性發(fā)生轉(zhuǎn)折,進(jìn)入負(fù)阻區(qū),此時(shí)電流極大,而導(dǎo)通電阻極小,使干擾能量得以轉(zhuǎn)移。隨著干擾減小,通過放電管電流的回落,當(dāng)放電管的通過電流低于維持電流時(shí),放電管就迅速走出低阻區(qū),而回到高阻態(tài),完成放電過程。固體放電管的一個(gè)優(yōu)點(diǎn)是它的短路失效模式(器件失效時(shí),兩電極間呈短路狀),為不少應(yīng)用場(chǎng)合所必須,已在國(guó)內(nèi)外得到廣泛應(yīng)用。固體放電管的電壓檔次較少,比較適合于作網(wǎng)絡(luò)、通信設(shè)備,乃至部件的保護(hù)。

七、PCB使用技巧

1、元器件標(biāo)號(hào)自動(dòng)產(chǎn)生或已有的元器件標(biāo)號(hào)取消重來

Tools工具|Annotate…注釋

All Part:為所有元器件產(chǎn)生標(biāo)號(hào)

Reset Designators:撤除所有元器件標(biāo)號(hào)

2、單面板設(shè)置:

Design設(shè)計(jì)|Rules…規(guī)則|Routing layers

Toplayer設(shè)為NotUsed

Bottomlayer設(shè)為Any

3、自動(dòng)布線前設(shè)定好電源線加粗

Design設(shè)計(jì)|Rules…規(guī)則|Width Constraint

增加:NET,選擇網(wǎng)絡(luò)名VCC GND,線寬設(shè)粗

4、PCB封裝更新,只要在原封裝上右鍵彈出窗口內(nèi)的footprint改為新的封裝號(hào)

5、100mil=2.54mm;1mil=1/1000英寸

6、快捷鍵“M”,下拉菜單內(nèi)的Dram Track End 拖拉端點(diǎn)====拉PCB內(nèi)連線的一端點(diǎn)處繼續(xù)連線。

7、定位孔的放置

在KeepOutLayer層(禁止布線層)中畫一個(gè)圓,Place|Arc(圓心弧)center,然后調(diào)整其半徑和位置

8、設(shè)置圖紙參數(shù)

Design|Options|Sheet Options

(1)設(shè)置圖紙尺寸:Standard Sytle選擇

(2)設(shè)定圖紙方向:Orientation選項(xiàng)----Landscape(小平方向)----Portrait(垂直方向)

(3)設(shè)置圖紙標(biāo)題欄(Title BlocK):選擇Standard為標(biāo)準(zhǔn)型,ANSI為美國(guó)國(guó)家協(xié)會(huì)標(biāo)準(zhǔn)型

(4)設(shè)置顯示參考邊框Show Reference Zones

(5)設(shè)置顯示圖紙邊框Show Border

(6)設(shè)置顯示圖紙模板圖形Show Template Graphics

(7)設(shè)置圖紙柵格Grids

鎖定柵格Snap On,可視柵格設(shè)定Visible

(8)設(shè)置自動(dòng)尋找電器節(jié)點(diǎn)

10、元件旋轉(zhuǎn):

Space鍵:被選中元件逆時(shí)針旋轉(zhuǎn)90

在PCB中反轉(zhuǎn)器件(如數(shù)碼管),選中原正向器件,在拖動(dòng)或選中狀態(tài)下,

X鍵:使元件左右對(duì)調(diào)(水平面);Y鍵:使元件上下對(duì)調(diào)(垂直面)

11、元件屬性:

Lib Ref:元件庫(kù)中的型號(hào),不允件修改

Footprint:元件的封裝形式

Designator:元件序號(hào)如U1

Part type:元件型號(hào)(如芯片名AT89C52 或電阻阻值10K等等)(在原理圖中是這樣,在PCB中此項(xiàng)換為Comment)

12、生成元件列表(即元器件清單)Reports|Bill of Material

13、原理圖電氣法則測(cè)試(Electrical Rules Check)即ERC

是利用電路設(shè)計(jì)軟件對(duì)用戶設(shè)計(jì)好的電路進(jìn)行測(cè)試,以便能夠檢查出人為的錯(cuò)誤或疏忽。

原理圖繪制窗中Tools工具|ERC…電氣規(guī)則檢查

ERC對(duì)話框各選項(xiàng)定義:

Multiple net names on net:檢測(cè)“同一網(wǎng)絡(luò)命名多個(gè)網(wǎng)絡(luò)名稱”的錯(cuò)誤

Unconnected net labels:“未實(shí)際連接的網(wǎng)絡(luò)標(biāo)號(hào)”的警告性檢查

Unconnected power objects:“未實(shí)際連接的電源圖件”的警告性檢查

Duplicate sheet mnmbets:檢測(cè)“電路圖編號(hào)重號(hào)”

Duplicate component designator:“元件編號(hào)重號(hào)”

bus label format errors:“總線標(biāo)號(hào)格式錯(cuò)誤”

Floating input pins:“輸入引腳浮接”

Suppress warnings:“檢測(cè)項(xiàng)將忽略所有的警告性檢測(cè)項(xiàng),不會(huì)顯示具有警告性錯(cuò)誤的測(cè)試”

Create report file:“執(zhí)行完測(cè)試后程序是否自動(dòng)將測(cè)試結(jié)果存在文件中”

Add error markers:是否會(huì)自動(dòng)在錯(cuò)誤位置放置錯(cuò)誤符號(hào)

Descend into sheet parts:將測(cè)試結(jié)果分解到每個(gè)原理圖中,針對(duì)層次原理圖而言

Sheets to Netlist:選擇所要進(jìn)行測(cè)試的原理圖文件的范圍

Net Identifier Scope:選擇網(wǎng)絡(luò)識(shí)別器的范圍

14、系統(tǒng)原帶庫(kù)Miscellanous Devices.ddb中的DIODE(二級(jí)管)封裝應(yīng)該改,也就把管腳說明1(A) 2(K)改為A(A) K(K)這樣畫PCB導(dǎo)入網(wǎng)絡(luò)表才不會(huì)有錯(cuò)誤:Note Not Found

15、PCB布線的原則如下

(1)輸入輸出端用的導(dǎo)線應(yīng)盡量避免相鄰平行。加線間地線,以免發(fā)生反饋藕合。

(2)印制攝導(dǎo)線的寬度主要由導(dǎo)線與絕緣基扳間的粘附強(qiáng)度和流過它們的電流值決定。

當(dāng)銅箔厚度為0.05mm、寬度為1~15mm時(shí).通過2A的電流,溫度不會(huì)高于3℃,因此導(dǎo)線寬度為1.5mm(60mil)可滿足要求。對(duì)于集成電路,尤其是數(shù)字電路,通常選0.02~0.3mm(0.8~12mil)導(dǎo)線寬度。當(dāng)然,只要允許,還是盡可能用寬線.尤其是電源線和地線。導(dǎo)線的間距主要由壞情況下的線間絕緣電阻和擊穿電壓決定。對(duì)于集成電路,尤其是數(shù)字電路,只要工藝允許,可使間距小至5~8mm。

(3)印制導(dǎo)線拐彎處一般取圓弧形,而直角或夾角在高頻電路中會(huì)影響電氣性能。此外,盡量避免使用大面積銅箔,否則.長(zhǎng)時(shí)間受熱時(shí),易發(fā)生銅箔膨脹和脫落現(xiàn)象。必須用大面積銅箔時(shí),用柵格狀。這樣有利于排除銅箔與基板間粘合劑受熱產(chǎn)生的揮發(fā)性氣體。

(4)焊盤:焊盤中心孔要比器件引線直徑稍大一些。焊盤太大易形成虛焊。焊盤外徑D一般不小于(d+1.2)mm,其中d為引線孔徑。對(duì)高密度的數(shù)字電路,焊盤直徑可取(d+1.0)mm。

16、工作層面類型說明

⑴、信號(hào)層(Signal Layers),有16個(gè)信號(hào)層,TopLayer BottomLayer MidLayer1-14。

⑵、內(nèi)部電源/接地層(Internal Planes),有4個(gè)電源/接地層Planel1-4。

⑶、機(jī)械層(Mechanical Layers),有四個(gè)機(jī)械層。

⑷、鉆孔位置層(Drill Layers),主要用于繪制鉆孔圖及鉆孔的位置,共包括Drill Guide 和Drill drawing兩層。

⑸、助焊層(Solder Mask),有TopSolderMask和BottomSolderMask兩層,手工上錫。

⑹、錫膏防護(hù)層(Paste Mask)有TopPaste和BottomPaster兩層。

⑺、絲印層(Silkscreen),有TopOverLayer和BottomOverLayer兩層,主要用于繪制元件的外形輪廓。

⑻、其它工作層面(Other):

KeepOutLayer:禁止布線層,用于繪制印制板外邊界及定位孔等鏤空部分。

MultiLayer:多層

Connect:連接層

DRCError:DRC錯(cuò)誤層

VisibleGrid:可視柵格層

Pad Holes:焊盤層。

Via Holes:過孔層。

17、PCB自動(dòng)布線前的設(shè)置

⑴Design|Rules……

⑵Auto Route|Setup……

Lock All Pro-Route:鎖定所有自動(dòng)布線前手工預(yù)布的連線。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論