如上圖所示,-48V供電單板,控制風扇轉動,EMI濾波電路中2個22nf共模濾波電容和100nf差摸濾波電容故障燒毀,現(xiàn)在基本上可以排除是器件來料和機械應力導致,看單板上面有小蟲子爬過的痕跡,有沒有可能是小蟲子導致短路引起的,各位大神有遇到過這樣的情況嗎?求解答

2016-07-19 23:25:57

單板部分電路要求有上拉,但供電只有-48V電源,怎么實現(xiàn)?加一個3.3V電源?

2015-08-11 23:23:34

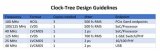

從今天開始我們分5期講述一下電子產品系統(tǒng)中一個非常重要的部位 - 時鐘。多數(shù)工程師意識不到它的重要性,覺得只要板子上的晶體/晶振能工作就可以了,其實不然,在今天數(shù)字邏輯、數(shù)字計算統(tǒng)治的世界里,幾乎

2019-07-21 21:43:14

復位是什么意思?時鐘可分為哪幾種?時鐘有什么作用?晶體振蕩器有哪些功能及用途?晶體振蕩器的特性是什么?

2021-07-01 07:38:04

晶體管電路設計(上),需要完整版的朋友可以下載附加保存哦~

2021-09-29 10:17:07

F28377D的外部時鐘,在手冊中是下面這樣的controlsuite中原理圖是下面這樣的這圖中是晶體,但好像不是手冊中的電路,請問是怎么回事

2018-11-26 11:30:06

Fsys系統(tǒng)時鐘 Fosc晶體時鐘 請問Fsub是什么意思?

2015-07-22 16:48:03

焊盤屬性是鋪地屬性是用的軟件是AD09,謝謝~

2019-05-15 04:16:26

PCB中包地與鋪地(鋪銅)有什么區(qū)別?需要包地的地方直接用GND鋪銅可以嗎?

2023-04-11 17:29:22

在多層PCB設計中,在中間層有很多的地層,這樣做的好處是什么?

2016-05-06 11:24:33

本帖最后由 gk320830 于 2015-3-7 13:54 編輯

PCB板上沒有絲印的好處 自從開始從事電子設計以來,制作各種各樣功能的PCB就一直貫穿始終。每次正面都印上了絲印,如果背面

2013-10-11 10:57:10

右下這3個選項幫解釋下,我能看懂英文,但是沒怎么理解,現(xiàn)在想鋪地把之前連的地線全部融合,包含了,選哪個應該?

2019-04-22 06:36:58

我正在嘗試一個PIC12F1571UP并運行一個晶體。不是一個諧振器,只是一個晶體。數(shù)據(jù)表第5.1節(jié)說“時鐘源可以從外部振蕩器、石英晶體諧振器、陶瓷諧振器提供……”,但是沒有具體說明你可以從晶體上

2019-09-10 12:58:30

時鐘,RC振蕩器4.LSE是低速外部時鐘,接頻率為32.768kHz的石英晶體5.PLL為鎖相環(huán)倍頻輸出,其時鐘輸入源可選擇為HSI或者HSE在STM32上如果不使用外部晶振,OSC_IN和OSC_OUT的接法:如果使用內部RC振蕩器而不使用外部晶振,請按照下面方法處理:1.100腳或1..

2022-01-26 06:39:54

我正在基于 STM32H7B3I-EVAL 評估板使用 STM32H7B3LIH6Q 設計定制板。從提供的示意圖中可以看出,評估板上使用的晶體為 24 MHz。 現(xiàn)在,我正在構建自己的電路板并注意到

2023-02-01 08:20:55

下面是一個STM32芯片的時鐘樹圖1、LSI是低速內部時鐘,RC振蕩器,頻率為32kHz左右。供獨立看門狗和自動喚醒單元使用。 2、LSE是低速外部時鐘,接頻率為32.768kHz的石英晶體。這個

2021-08-12 07:45:54

按照說明去寫的tf卡1. sudo ./mksdcard.sh2.拷貝文件3.撥碼開關123 on單板上電串口一點打印也沒有

2021-12-31 06:11:15

如題:pcb沒有網表能鋪銅鋪地嗎?

2011-05-02 11:15:52

多孔接地)。時鐘晶體下面鋪地的好處: 晶體振蕩器內部的電路會產生射頻電流,如果晶體是金屬外殼封裝的,直流電源腳是直流電壓參考和晶體內部射頻電流回路參考的依靠,通過地平面釋放外殼被射頻輻射產生的瞬態(tài)電流

2015-12-20 19:27:25

是:

【野火魯班貓2單板電腦=物聯(lián)網+綜合小項目】 野火魯班貓2單板電腦=物聯(lián)網+綜合小項目_嗶哩嗶哩_bilibili

歡迎小伙伴去站觀看我的視頻,多多分享,給我投票點贊。

下面是項目演示中的一些照片:

2023-05-18 20:06:03

請教給位大神,晶振下方到底是挖空好還是鋪地好& p& V2 I/ Q- M# O比如說我兩層板,頂層是貼片晶振,那么底層是挖空還是鋪地好,網上看了兩種說法都有,這讓我很糾結

2018-12-26 11:55:00

突然發(fā)現(xiàn)外國工程師信號層(大多數(shù)頂層)好像都不鋪地,底層和中間層大面積普通,這有什么原因嗎?

2019-07-29 03:21:25

某工控設備開發(fā)廠商的設備中采用單片機控制電路,單片機使用外接的兩腳晶體振蕩器產生11.0592MHz的工作時鐘。用戶希望能夠精確測量工作時鐘的頻率,但用示波器測量時一方面測不準,另一方面測量時還會出現(xiàn)晶體停振的情況,對于這種晶體的頻率測量有沒有好的辦法呢?

2019-08-09 06:57:06

接地技術的引入最初是為了防止電力或電子等設備遭雷擊而采取的保護性措施,但是隨著電子通信和其它數(shù)字領域的發(fā)展,在接地系統(tǒng)中只考慮防雷和安全已遠遠不能滿足要求了。想請教一下 為什么要將模擬地和數(shù)字地分開?單板上的信號如何接地?

2021-04-06 09:58:17

1、時鐘線等長概念 在一塊主板上,從北橋芯片到CPU、內存、AGP插槽的距離應該相等,主板設計的基本要求,即所謂的“時鐘線等長”概念。作為CPU與內存連接橋梁的北橋芯片,在布局上是很有講究的。例如

2018-08-30 10:14:47

什么叫PCB單板 ?是單層板的意思嗎?PCB聯(lián)板又是什么意思?

2023-04-23 16:15:11

使用stc89c52單板機下載程序,板子上是u***,如何查看u***是

2012-03-04 17:17:01

非常精確的時候可以省掉外部晶體和兩個電容,好處是可以簡化布線,節(jié)省成本并進一步降低功耗;缺點也很明顯,HSI不夠精準,官方給出的誤差是在1%(25攝氏度)。根據(jù)手冊,USB時鐘不能用HSI經PLL后得...

2021-08-12 08:18:25

各位大神: 我想請教下,如果雙面板布板要抗干擾好的話(比如過群脈沖),是不是應該盡量把線路都畫在同一層,然后另外一層鋪一整塊比較完整的地,這樣是不是抗干擾會大大提升呢?如果是的話,我想問鋪地的那層

2019-10-24 22:38:45

描述Commodore 64 診斷加密狗(5 合 1)這個項目是一個單板解決方案,它取代了運行 Commodore 64 診斷盒 586220 所需的 5 個部件。為不同的端口安裝了不同的組件。所有

2022-07-07 07:29:11

`可靠性案例分享——單板低溫啟動不成功問題問題描述:A單板在調試過程中發(fā)現(xiàn)概率性啟動不成功,電流顯示在0.31A左右,測試發(fā)現(xiàn)晶體不起振,定位為晶體不起振問題 `

2016-09-03 16:15:14

1、外部晶體/陶瓷諧振器(HSE晶體)模式 這種模式用得比較常見,HSE晶體可以為系統(tǒng)提供較為精確的時鐘源。在時鐘控制寄存器RCC_CR中的HSERDY位用來指示高速外部振蕩器是否穩(wěn)定。在啟動時

2021-08-10 08:18:52

`32.768KHZ是一個很有意義的數(shù)字,我們每天都要用到它,它給我們帶來太多的好處.只是生活中太少有人去關注了,只關注著它給我們帶來的演變數(shù)字.32.768khz比較容易分頻以便于產生1秒的時鐘

2016-05-28 11:18:32

如何識別STM32五個時鐘源及其不接外部晶體時的管腳配置?A:1.HSI是高速內部時鐘,RC振蕩器,頻率為8MHz。2. HSE是高速外部時鐘,可接石英/陶瓷諧振器,或者接外部時鐘源,頻率范圍為

2021-08-10 06:34:21

小弟正聯(lián)系使用AD09畫PCB。進入鋪地階段。開發(fā)板的鋪地是怎么實現(xiàn)的呢?開發(fā)板的鋪地和元件的管腳之間的間距很大,但是我的鋪地和管腳之間的距離很小,請問,如何設置?開發(fā)板的鋪地:我自己的鋪地:感激不盡呀!!

2019-01-18 06:36:26

,無論純石英晶體或13M組件電路,均需要電源正常工作輸出供電,13M電路才能產生13M輸出。 2、 實時時鐘頻率的產生 手機中的實時時鐘頻率基本上都是32.768KHz,是由32.768KHz晶體配合其他

2016-11-01 17:43:34

我鋪地的時候它老是短路焊盤!可是人家為什么都可以不短路呢?

2016-02-12 18:16:26

LTC2949,請協(xié)助確認是否可以使用LTC29498MHz 晶體作為外部時鐘輸入的外部時鐘嗎 ? 非常感謝

2024-01-04 08:00:14

大家好,我想知道是否可以使用當前為主 MCU (STM32F334) 提供時鐘的單個現(xiàn)有晶體振蕩器為另一個 STM32 MCU (STMF031) 提供時鐘。它真的可以為我節(jié)省空間、功耗、成本和電路板上的另一個時鐘源。如果是,如何?

2023-01-12 07:25:54

`管腳連接了地線,copper pour鋪地就無法連接了?COPPER POUR區(qū)域也定義為GND網絡了。打樣回來的板子也沒有問題,不知道為什么點擊地線網絡,鋪地沒有鏈接到一起?`

2011-06-22 11:20:36

我設計的板子,繼電器下面鋪了地的,使用起來沒什么問題。但我看別人設計的,在繼電器下面是不鋪地的,不知道我的設計會有什么問題

2013-12-11 15:24:32

Hi(圖片請參考附件) 本人在使用HMC 6300/6301中發(fā)現(xiàn)6350評估板上時鐘的對接和耦合方式非常奇怪,違反通識。 6350單板上通往6300/6350連接器的最后一級時鐘如下圖: 從

2018-07-30 10:24:27

時鐘多米諾邏輯是晶體管級的結構,請問其結構如何,有何作用?如何理解比較好。

2019-07-25 05:56:04

畫PCB鋪地時候,什么時候鋪實地什么時候網格地,有什么區(qū)別?求教!!!!!!!!!!!!

2019-02-13 06:36:32

先鋪地在接地線是這樣的。先接地線,再鋪地,是這樣的。怎么樣才能讓它先接地線,再鋪地也與前一張一樣呢?謝謝,

2019-01-30 06:36:39

外部晶體時鐘或內部RC振蕩器時鐘在“時鐘源選項”的配置位

2020-12-09 07:51:15

-- 今天無數(shù)電子線路和應用需要精確定時或時鐘基準信號。晶體時鐘振蕩器極為適 合這方面的許多應用。時鐘振蕩器有多種封裝,它的特點是電氣性能規(guī)范多種多樣。它有好幾

2009-12-02 15:35:46 0

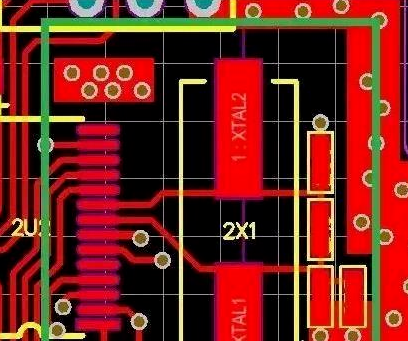

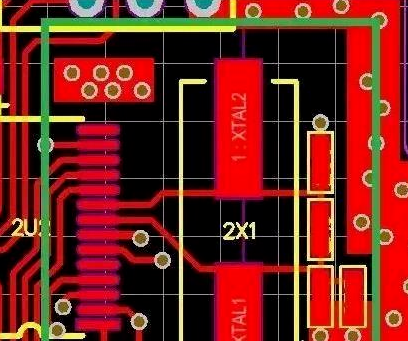

0 PCB單板及拼板設計 一.單板設計 圖1 單板PCB設計 1. 適用條件: 采用手工焊接或單板尺寸較大的PCB,可采用單板方式設計; 2. 設置基準點(坐標0,0): 推薦將板邊左下角設為基準點,

2012-06-28 12:54:50 0

0 2、單板高溫老化0218

2017-01-08 16:28:07 0

0 除了少數(shù)罕見的特例以外,幾乎所有的電子系統(tǒng)都至少擁有一個時鐘功能,這已經不是新聞。在大多數(shù)情況下,該時鐘功能是通過采用石英晶體加上相關振蕩器或時鐘發(fā)生器集成電路實現(xiàn),這種基本的實現(xiàn)方式可提供一個單一

2017-10-15 10:51:47 0

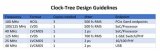

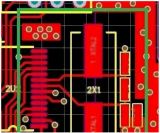

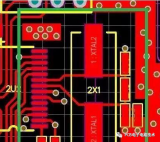

0 分下一層最好不要走線 在PCB時鐘電路區(qū)域只布與時鐘電路有關的器件,避免布設其他電路,晶體附近或者下面不要布其他信號線:在時鐘發(fā)生電路、晶體下使用地平面,若其他信號穿過該平面,違反了映像平面功能,如果讓信號穿越這個地平面的

2018-02-20 20:26:00 3462

3462

我們將對多層電路板進行射頻線仿真,為了更好的做出對比,將仿真的PCB分為表層鋪地前的和鋪地后的兩塊板分別進行仿真對比;表層未鋪地的PCB文件如下圖1所示。

2018-04-09 15:54:00 4789

4789

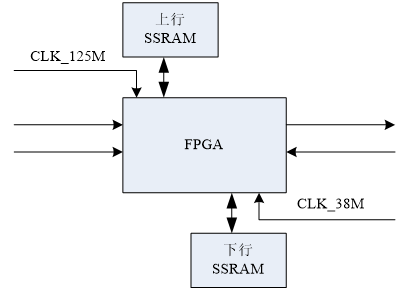

我們系統(tǒng)中,主板與從板之間通過交換網片的HW0、HW4互連,要使主板與從板的交換網之間能夠正常交換,必須使這兩個交換網片有一致的幀同步時鐘及位同步時鐘。在現(xiàn)在的單板中,從板的時鐘由主板直接送出。整個系統(tǒng)采用的時鐘源有3種方式:

2018-10-30 11:36:23 7

7 了解新的UltraScale ASIC時鐘架構:如何使用它,它帶來的好處以及從現(xiàn)有設計遷移的容易程度。

另請參閱如何使用時鐘向導配置時鐘網絡。

2018-11-29 06:40:00 3390

3390 首先將線寬不同的兩塊板(表層鋪地前)由ALLEGRO導入SIWAVE,在目標線上加入50Ω端口。針對不同線寬0.1016mm和0.35mm, 我們的仿真結果如圖2所示,圖中顯示的曲線是S21,仿真頻率范圍為800MHz-1GHz。

2019-09-17 14:42:42 4244

4244 雖然很多人都考慮過pcba外包,卻并不真正清楚pcba外包的好處。下面說一說選擇pcba外包的理由和好處。

2020-07-06 09:44:51 3038

3038 舉個例子來說吧。我們將對多層電路板進行射頻線仿真,為了更好的做出對比,將仿真的PCB分為表層鋪地前的和鋪地后的兩塊板分別進行仿真對比;表層未鋪地的PCB文件如下圖1所示(兩種線寬):

2020-11-03 10:40:00 5

5 Kyle Beckmeyer特別于近期撰寫一篇技術文章,說明關于新型智能汽車的時鐘設計關鍵需求與理想的時鐘發(fā)生器解決方案。 您將了解到 汽車電子中所需的精密參考時鐘數(shù)量正在增加系統(tǒng)設計的復雜性并改變最佳實踐方法。 將時鐘需求從石英換成硅芯片的好處

2021-05-03 18:31:00 1315

1315

華為單板熱設計培訓資源下載

2021-06-03 10:09:15 50

50 如何從PCB布局上來考慮EMC問題;4.如何正確使用磁珠、電容、共模電感等EMC元器件,在單板原理圖階段全面考慮電磁兼容的問題;6.如何從PCB中考慮多種地的隔離、分割.7.如何從PCB設計的過程中控制EMC問題,如時鐘走線、電源走線以及接口走線控制。

2021-11-23 10:55:59 5531

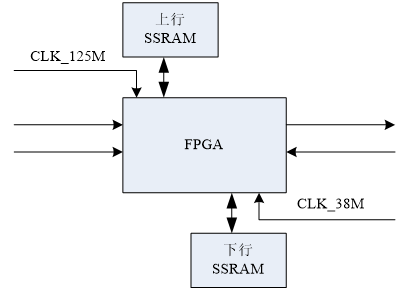

5531 本文結合某單板(下文中統(tǒng)一稱M單板)FPGA調試過程中發(fā)現(xiàn)地彈噪聲造成某重要時鐘信號劣化從而導致單板業(yè)務丟包的故障,來談下如何最大程度地降低地彈噪聲對單板信號完整性影響。

2022-07-27 09:12:17 531

531 時鐘晶體電路一般有兩種:無源晶體電路和有源震蕩器電路。時鐘晶體電路一般是輻射發(fā)射的干擾源。

2022-10-10 15:51:12 1693

1693 壓接技術在連接器行業(yè)非常流行,那么什么是壓接技術呢?壓接技術能為連接器提供哪些好處?下面,康瑞連接器廠商將為大家分享壓接技術為連接器提供的三大好處!

2022-11-18 16:52:48 1763

1763 CCE4510單板

2023-01-11 18:41:27 0

0 本應用筆記介紹了將32,768Hz晶體連接到實時時鐘(RTC)的晶體選擇和布局技術。它還提供有關振蕩器電路設計標準、系統(tǒng)設計和制造問題的信息。

2023-02-07 14:40:39 302

302

時鐘晶體和相關電路應布置在PCB的中央位置并且要有良好的地層,而不是靠近I/O接口處。不可將時鐘產生電路做成子卡或者子板的形式,必須做在單獨的時鐘板上或者承載板上。

2023-02-08 09:12:00 413

413 時鐘晶體和相關電路應布置在PCB的中央位置并且要有良好的地層,而不是靠近I/O接口處。

2023-02-22 09:22:50 306

306 單板上時鐘的注意事項,主要有以下幾個方面可以考慮。

2023-05-09 10:09:15 593

593

本文結合某單板(下文中統(tǒng)一稱M單板)FPGA調試過程中發(fā)現(xiàn)地彈噪聲造成某重要時鐘信號劣化從而導致單板業(yè)務丟包的故障,來談下如何最大程度地降低地彈噪聲對單板信號完整性影響。

2023-06-26 10:17:37 381

381

晶體振蕩器內部的電路會產生射頻電流,如果晶體是金屬外殼封裝的,直流電源腳是直流電壓參考和晶體內部射頻電流回路參考的依靠,通過地平面釋放外殼被射頻輻射產生的瞬態(tài)電流。

2023-06-30 14:16:31 323

323

CCE4510單板

2023-06-30 20:17:51 2

2 介紹:

Pericom為選定的獨立實時時鐘(RTC)產品提供集成晶體封裝選項。新的封裝將串行接口(I2C RTC器件)與兼容的32.768 kHz石英晶體集成到單個8引腳中DFN4×4 或 16 引腳 SOIC 封裝。

我們在下面列出了一些關于新的集成晶體封裝選項的常見問題。

2023-07-24 16:14:45 0

0 單片機時鐘電路主要由晶體振蕩器和相應的外圍電路組成。晶體振蕩器通常使用晶體作為振蕩元件,當施加合適的電壓和電流時,晶體會以特定的頻率振蕩。晶體振蕩器將晶體振蕩的信號轉換為一個穩(wěn)定的時鐘信號,供單片機系統(tǒng)使用。

2023-08-07 16:49:46 4120

4120 定義:指導PCBA單板工藝應變測試,以及在單板加工過程中的應變管控重點。

2023-08-10 09:44:36 1297

1297

定義:指導PCBA單板工藝應變測試,以及在單板加工過程中的應變管控重點。

2023-08-28 14:33:15 544

544

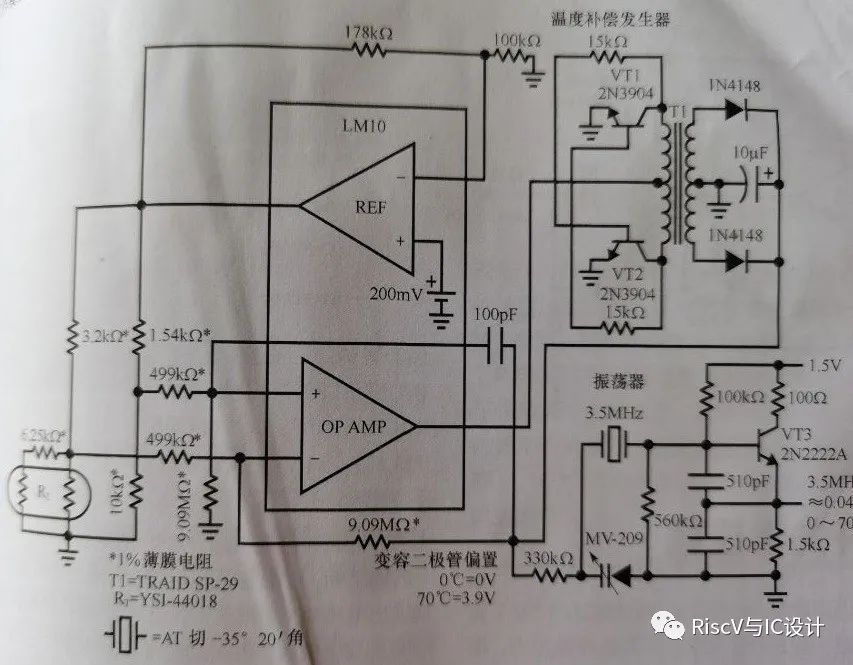

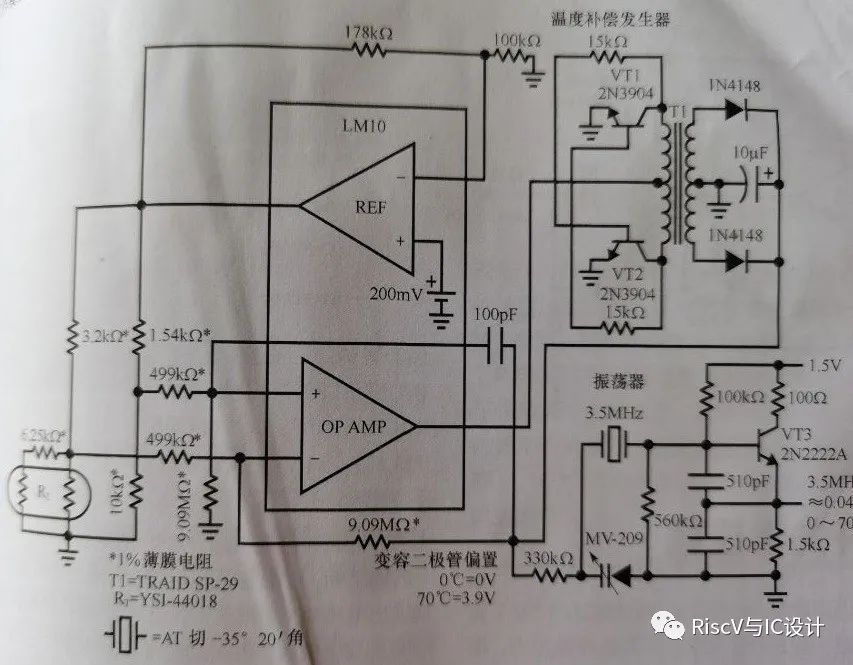

電子系統(tǒng)都需要一個穩(wěn)定的時鐘源,一般都采用晶體振蕩器,設計一個低壓1.5V的振蕩器相對容易,如果振蕩器需要良好的溫度穩(wěn)定性,由于晶體的溫漂特性,設計就變得復雜了。

2023-10-13 14:42:02 315

315

時鐘晶體下面鋪地和走線

2023-11-24 15:37:09 429

429

晶振頻率和時鐘頻率本質上有何區(qū)別呢?時鐘頻率有什么作用? 晶振頻率和時鐘頻率是兩個相關但又有所不同的概念。下面我們將逐一介紹這兩個概念的含義、區(qū)別和作用。 首先,我們來了解晶振頻率。晶振是一種

2024-01-24 16:11:35 307

307 石英晶體振蕩器是如何產生時鐘信號的呢? 石英晶體振蕩器是一種電子振蕩器,它使用石英晶體作為諧振元件來產生穩(wěn)定的時鐘信號。在現(xiàn)代電子設備中,石英晶體振蕩器被廣泛應用于各種計算機、通信設備、電子表

2024-01-29 13:58:19 191

191 單板上時鐘的注意事項 單板上時鐘晶體下面鋪地的好處 單板上時鐘是指將時鐘晶體組件直接鋪裝在電路板上,這種設計方案在電子設備中廣泛應用。在介紹單板上時鐘的注意事項之前,讓我們先了解一下為什么要在單板

2024-02-06 16:06:50 161

161

電子發(fā)燒友App

電子發(fā)燒友App

評論