摘要:本應用筆記介紹了如何配置DS3184中的時鐘速率適配器(CLAD)功能單元。同樣適用于其他Dallas Semiconductor的器件,例如DS3181, DS3182和DS3183。DS3181, DS3182, DS3183和DS3184 (DS318x)集成了ATM信元/HDLC分組處理器、DS3/E3成幀器和LIU,能夠逐端口地將ATM信元或分組按照DS3幀(C位或M23)、E3幀(G.751或G.832)或凈信道數據流方式,映射/去映射到最多四條DS3/E3物理層銅纜上。

DS318x內的CLAD單元用來從單一參考時鐘(由CLKA引腳輸入)生成內部電路工作所需的多個DS3、E3或STS-1時鐘。加到CLKA引腳的時鐘頻率應該是以下幾種頻率中的一種:

給出其中一種時鐘,另外兩種可由電路產生。內部產生的時鐘可驅動輸出引腳CLKB和CLKC,如果需要,可供外部電路使用。

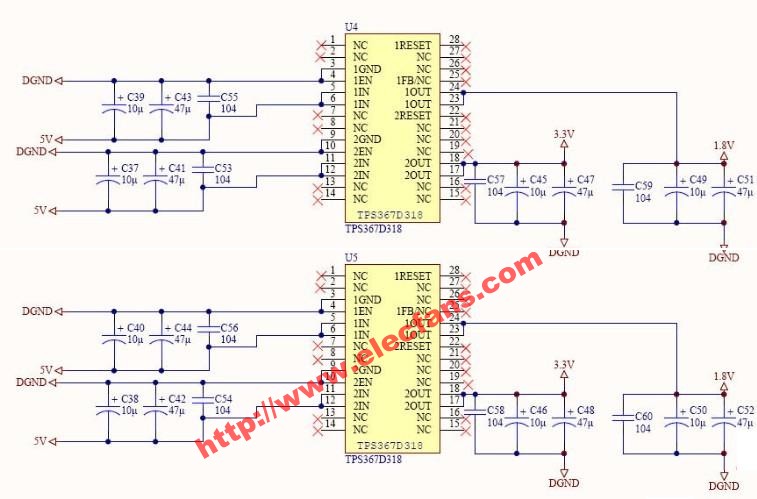

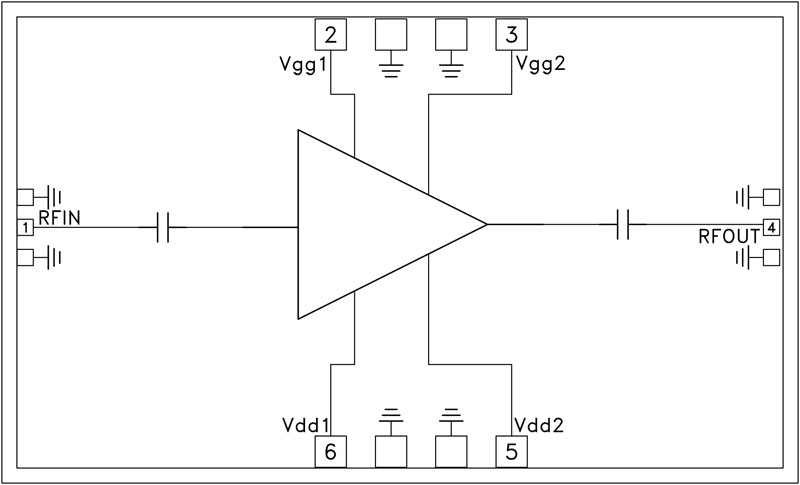

至少,用戶必須提供三種頻率(DS3、E3、STS-1)中的一種給CLKA引腳。CLAD[3:0]位告訴PLL加到引腳上的頻率是多少。圖1表示DS318x的CLAD單元。

圖1. DS318x的CLAD單元

FM位(位于PORT.CR2內)控制CLAD輸出并供給LIU和發送器的時鐘的選擇。CLAD為設計者提供了最大的靈活性。系統只需提供三種時鐘速率中的任意一種,就可用CLAD產生所需要的所有時鐘。

也可以關閉CLAD,而從外部通過CLKA、CLKB和CLKC引腳輸入全部三種時鐘。當CLAD被關閉后,三路參考時鐘(DS3、E3和STS-1)分別被饋送到CLKA、CLKB和CLKC引腳。如果三種頻率中的任何一種不會用到,就無需將其送入CLAD時鐘引腳了。

CLAD的CLAD MODE輸入由CLAD[3:0]控制位(位于GL.CR2寄存器)組成,它們決定了各引腳作為輸入還是輸出,以及各個引腳上的時鐘速率。詳細信息參見表1。

當CLAD[3:0] = 00XX時,PLL電路被關閉,時鐘輸入引腳(CLKA, CLKB和CLKC)上的信號被用作內部LIU的參考時鐘。當CLAD[3:0] = (01XX或10XX或11XX)時,零、一或二個PLL電路被使能,根據CLAD[3:0]位、幀模式(FM[5:0])和線路模式控制位(LM[2:0],位于PORT.CR2)的設定產生內部電路需要的時鐘。

線路模式位選擇主端口-接口的工作模式。如果不需要向CLAD時鐘輸出引腳輸出某個時鐘頻率,或向LIU提供某個頻率的參考時鐘,那用來產生該時鐘的PLL就可以關閉并進入掉電模式。

表1. CLAD I/O引腳譯碼

CLAD提供參考時鐘給接收LIU。接收LIU根據用戶通過幀模式(FM)位選擇的模式選擇時鐘頻率。FM位選擇主成幀操作模式。如果利用PORT.CR3.CLADC寄存器位選定的話,CLAD輸出也可用作發送時鐘源。

簡介

本應用筆記概述了DS3184中時鐘速率適配器(CLAD)單元的配置。所提供的信息同樣適用于其他Dallas Semiconductor的器件,例如DS3181, DS3182和DS3183。DS318x (DS3181, DS3182, DS3183和DS3184)集成了ATM信元/HDLC分組處理器、DS3/E3成幀器和LIU,能夠逐端口地將ATM信元或分組按照DS3幀(C位或M23)、E3幀(G.751或G.832)或凈信道數據流方式,映射/去映射到最多四條DS3/E3物理層銅纜上。DS318x內的CLAD單元用來從單一參考時鐘(由CLKA引腳輸入)生成內部電路工作所需的多個DS3、E3或STS-1時鐘。加到CLKA引腳的時鐘頻率應該是以下幾種頻率中的一種:

A. DS3 (44.736MHz)

B. E3 (34.368MHz)

C. STS-1 (51.84MHz)

給出其中一種時鐘,另外兩種可由電路產生。內部產生的時鐘可驅動輸出引腳CLKB和CLKC,如果需要,可供外部電路使用。

CLAD特性

DS318x內的CLAD可從單一輸入參考頻率產生內部電路需要的DS3 (44.736MHz), E3 (34.368MHz)和STS-1 (51.84MHz)時鐘。這個輸入參考頻率可以是51.84MHz、44.736MHz或34.368MHz。這些內部導出的時鐘可被用作LIU和抖動抑制器的基準,還可送到片外供外部系統使用。配置CLAD

如果要使用DS318x的LIU,就需要CLAD提供時鐘給DS318x的接收LIU。可通過GL.CR2寄存器中的CLAD位來配置DS318x的CLAD。在此情況下,用戶必須向CLKA引腳提供一路DS3、E3或STS-1時鐘。至少,用戶必須提供三種頻率(DS3、E3、STS-1)中的一種給CLKA引腳。CLAD[3:0]位告訴PLL加到引腳上的頻率是多少。圖1表示DS318x的CLAD單元。

圖1. DS318x的CLAD單元

FM位(位于PORT.CR2內)控制CLAD輸出并供給LIU和發送器的時鐘的選擇。CLAD為設計者提供了最大的靈活性。系統只需提供三種時鐘速率中的任意一種,就可用CLAD產生所需要的所有時鐘。

也可以關閉CLAD,而從外部通過CLKA、CLKB和CLKC引腳輸入全部三種時鐘。當CLAD被關閉后,三路參考時鐘(DS3、E3和STS-1)分別被饋送到CLKA、CLKB和CLKC引腳。如果三種頻率中的任何一種不會用到,就無需將其送入CLAD時鐘引腳了。

CLAD的CLAD MODE輸入由CLAD[3:0]控制位(位于GL.CR2寄存器)組成,它們決定了各引腳作為輸入還是輸出,以及各個引腳上的時鐘速率。詳細信息參見表1。

當CLAD[3:0] = 00XX時,PLL電路被關閉,時鐘輸入引腳(CLKA, CLKB和CLKC)上的信號被用作內部LIU的參考時鐘。當CLAD[3:0] = (01XX或10XX或11XX)時,零、一或二個PLL電路被使能,根據CLAD[3:0]位、幀模式(FM[5:0])和線路模式控制位(LM[2:0],位于PORT.CR2)的設定產生內部電路需要的時鐘。

線路模式位選擇主端口-接口的工作模式。如果不需要向CLAD時鐘輸出引腳輸出某個時鐘頻率,或向LIU提供某個頻率的參考時鐘,那用來產生該時鐘的PLL就可以關閉并進入掉電模式。

CLAD配置寄存器

下面簡單介紹一下用于配置CLAD的兩個寄存器。寄存器名:GL.CR2

寄存器描述:全局控制寄存器2

寄存器地址:004h

| Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| Name | - | - | - | G8KRS2 | G8KRS1 | G8KRS0 | G8K0S | G8KIS |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | - | - | - | - | CLAD3 | CLAD2 | CLAD1 | CLAD0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位3到0:CLAD I/O模式[3:0] (CLAD[3:0])

這些位用于控制CLAD時鐘I/O引腳CLKA、CLKB和CLKC。這些寄存器位決定了使用哪個時鐘來從LIU線路中恢復接收時鐘。詳情見表1。表1. CLAD I/O引腳譯碼

| GL.CR2 | CLKA PIN | CLKB PIN | CLKC PIN |

| CLAD[3:0] | |||

| 00 XX | DS3 clock input | E3 clock input | STS-1 clock input |

| 01 00 | DS3 clock input | Low output | Low output |

| 01 01 | DS3 clock input | E3 clock output | Low output |

| 01 10 | DS3 clock input | Low output | STS-1 clock output |

| 01 11 | DS3 clock input | STS-1 clock output | E3 clock output |

| 10 00 | E3 clock input | Low output | Low output |

| 10 01 | E3 clock input | DS3 clock output | Low output |

| 10 10 | E3 clock input | Low output | STS-1 clock output |

| 10 11 | E3 clock input | STS-1 clock output | DS3 clock output |

| 11 00 | STS-1 clock input | Low output | Low output |

| 11 01 | STS-1 clock input | E3 output | Low output |

| 11 10 | STS-1 clock input | Low output | DS3 clock output |

| 11 11 | STS-1 clock input | DS3 clock output | E3 clock output |

CLAD提供參考時鐘給接收LIU。接收LIU根據用戶通過幀模式(FM)位選擇的模式選擇時鐘頻率。FM位選擇主成幀操作模式。如果利用PORT.CR3.CLADC寄存器位選定的話,CLAD輸出也可用作發送時鐘源。

寄存器名:PORT.CR3

寄存器描述:端口控制寄存器3

寄存器地址:(0, 2, 4, 6)44h

| Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| Name | - | - | RCLKS | RSOFOS | RPFPE | TCLKS | TSOFOS | TPFPE |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | P8KRS1 | P8KRS0 | P8KREF | LOOPT | CLADC | RFTS | TFTS | TLTS |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位3: CLAD發送時鐘源控制(CLADC)

這一位用來使CLAD時鐘作為內部發送部分的時鐘源。該位功能的執行還和其他控制位有關。0 = 采用CLAD時鐘作為發送時鐘

1 = 不用CLAD時鐘作為發送時鐘(如果沒有使能環回,時鐘源為TCLKIn)

電子發燒友App

電子發燒友App

評論