ADI最近推出業界性能最高的ADF4159 13 GHz PLL頻率合成器。ADF4159實現了突破性的110 MHz鑒頻鑒相器工作頻率,同時功耗低于100mW,僅為競爭解決方案的五分之一

2012-07-04 09:30:43 1726

1726 Analog Devices, Inc.(ADI),最近發布了一款提供領先相位噪聲性能的PLL頻率合成器ADF4153A。

2012-11-01 09:09:20 1497

1497 通過正確的設計方法,結合使用現代低成本高集成度的PLL和直接數字合成器(DDS)集成電路(IC)可以極大地促進高性能架構的實現。

2013-05-17 10:05:58 3325

3325

幾乎每個RF和微波系統都需要頻率合成器。頻率合成器產生本振信號以驅動混頻器、調制器、解調器及其他許多RF和微

2017-12-07 07:11:00 8835

8835

已經有段時間了。但是,在要求快速切換速度、低相位噪聲或低雜散信號電平的場合,有必要使用更為復雜的架構。通過正確的設計方法,結合使用現代低成本高集成度的PLL和直接數字合成器(DDS)集成電路(IC)可以極大地促進高性能架構的實現。

2022-10-14 10:30:36 2025

2025 本篇文章是關于相位鎖定環(PLL)頻率合成器的設計和分析,重點討論了相位噪聲和頻率噪聲的測量、建模和仿真方法。文章以設計一個假想的PLL頻率合成器為例,詳細介紹了設計過程和步驟。從規格選擇、電路配置

2023-10-26 15:30:51 483

483

概述:ADF41020是一款18GHz微波PLL頻率合成器,ADF41020 頻率合成器在無線接收機和發射機的上變頻和下變頻部分中,可用來實現高達18 GHz 的本振。

2021-04-12 07:59:42

DDS直接數字頻率合成器、信號發生器、函數發生器1.DDS直接數字頻率合成器、信號發生器、函數發生器他們之間有哪些異同?2.目前只發現ADI有相關的產品,國產有哪些品牌可以推薦3.如果要輸出的頻率和功率是實時可調的,用MCU控制DDS芯片是否可以實現?

2022-03-24 18:10:02

的輸出,并且如果正弦波不夠完美的話,在振蕩器內部稍微改造下來改變它的性能。當合成器執行反饋時,它們有時稱為鎖相環或PLL。www實際生活中的介成器作常復雜,也很昂貴。它們可以完成許多功能而不僅僅是反饋

2017-12-06 14:06:07

頻率合成器的高性能架構實現技術詳解

2021-04-07 06:48:49

(DDS),內置一個12位數模轉換器,目標工作速率最高達3.5 GSPS。該器件采用先進的DDS技術,連同高速、高性能數模轉換器,構成數字可編程的完整高頻合成器,能夠產生最高1.4 GHz的頻率捷變模擬輸出

2019-06-17 15:28:25

`AD9914BCPZ直接數字頻率合成器AD9914是一款直接數字頻率合成器(DDS),內置一個12位數模轉換器,目標工作速率最高達3.5 GSPS。該器件采用先進的DDS技術,連同高速、高性能

2020-11-18 11:36:18

的DDS技術,連同高速、高性能數模轉換器,構成數字可編程的完整高頻合成器,能夠產生1.4 GHz的頻率捷變模擬輸出正弦波。AD9914專為提供快速跳頻和精密調諧分辨率(標準模式下32位、可編程模數模式下

2019-04-29 15:06:55

DAC模擬乘法器、DDS(頻率合成器)、信號發生器1.DAC模擬乘法器構成的混頻器是否可以和DDS(頻率合成器)、信號發生器一樣?可以生成任意目前波形?2.DDS(頻率合成器)、信號發生器它倆之間有存在哪些異同?

2022-03-24 17:24:37

。選擇頻率合成器芯片時,第一步是決定使用整數N還是分數N型頻率合成器。設計良好的Σ-Δ分數N頻率合成器能夠在相位噪聲、PLL鎖定時間和鑒相噪聲抑制方面提供優異的性能。雖然分數N頻率合成器的成本不斷降低,但

2019-06-26 06:42:04

的輸出能否具有調幅(AM)、調頻(FM)和調相(PM)等功用。 隨著電子技術的不時開展,對頻率合成器性能的請求越來越高。20世紀80年代以來,各國都在研制和開展各自的DDS產品,如今盛行的DDS產品以

2020-03-17 14:54:24

頻率合成技術是現代通信的重要組成部分,它是將一個高穩定度和高準確度的基準頻率經過四則運算,產生同樣穩定度和準確度的任意頻率。頻率合成器是電子系統的心臟,是影響電子系統性能的關鍵因素之一。本文結合

2019-06-25 06:36:13

問:什么是PLL頻率合成器?

2019-09-17 19:00:51

和相位來生成被調制信號,因此對于數字通信系統來說可以產生任意的波形。軟件無線電系統中的數字上下變頻、本地載波的產生以及壓控震蕩器等重要環節都可以用DDS技術實現。 采用DDS技術的直接數字頻率合成器

2019-08-19 19:18:00

限,因此在設計工作頻率寬、調協精度高的頻率合成器時,這兩種方式均不能滿足技術要求。但是,采用DDS+PLL方式,可以滿足高精度和寬頻帶的需要,其實現的難點是如何提高合成器輸出頻譜純度。在實際印制電路板制作中,DDS的良好接地和合理布線非常有助于系統設計的實現。來源:與非網

2011-07-16 09:09:54

(DDS)技術,提出毫米波頻率合成器的設計方案。進行方案系統實驗,結果表明,相位噪聲為-85dBc/Hz@10kHz,提升了整個毫米波通信系統的性能。【關鍵詞】:毫米波;;頻率合成;;相位噪聲;;頻率

2010-04-22 11:47:22

直接數字頻率合成(DDS)在過去十年受到了頻率合成器設計工程師極大的歡迎,它被認為是一種具有低相位噪聲和優良雜散性能的靈活的頻率源,基于DDS的頻率合成器在許多應用中能比基于鎖相環(PLL)頻率

2019-07-08 07:26:17

本文設計了一種多環鎖相頻率合成器。多環鎖相環路有直接數字頻率合成(DDS)環路和鎖相頻率合成環路(PLL)組成。充分利用兩個不同環路的優點,既保證了高的輸出頻率,又得到了較高的頻率分辨率。【關鍵詞

2010-05-13 09:09:53

電子技術應用頻率合成技術是現代通信的重要組成部分,它是將一個高穩定度和高準確度的基準頻率經過四則運算,產生同樣穩定度和準確度的任意頻率。頻率合成器是電子系統的心臟,是影響電子系統性能的關鍵因素之一

2019-07-30 07:55:22

PLL應用中頗具價值的注意事項和使用技巧基于鎖相環(PLL)技術的頻率合成器

2021-05-12 06:59:03

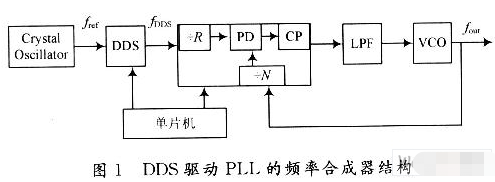

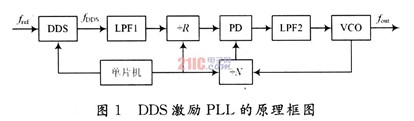

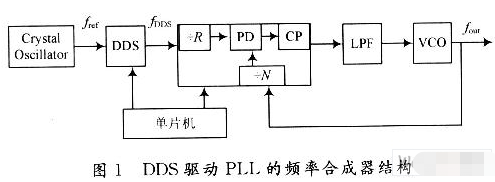

本文將介紹DDS和PLL的工作原理,并結合一電臺(工作頻率2 MHz~500 MHz)的設計,給出DDS做參考的PLL頻率合成器的設計方案。

2021-04-20 06:42:27

的技術和器件產,它的性牟指標尚不能與已有的技術盯比,故未受到重視。近1年間,隨著微電子技術的迅速發展,直接數字頻率合成器(Direct Digital Frequency Synthesis簡稱DDS

2019-08-21 07:45:04

用DDS制作數控信號合成器

2016-11-04 21:52:02

EV-ADF41020EB1Z,用于ADF41020 PLL頻率合成器評估板的評估板。評估用于鎖相環(PLL)的ADF41020頻率合成器。它包含ADF41020合成器,100 MHz TCXO,電源,USB接口和RF輸出。板載有一個有源環路濾波器和一個13 GHz VCO

2019-02-28 07:23:02

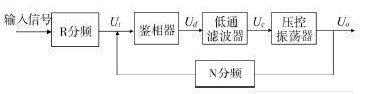

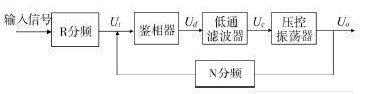

)可以極大地促進高性能架構的實現。大部分高頻系統都使用傳統的基于整數分頻器的設計(圖1)或基于分數N分頻器的設計。不管是使用哪種設計,聯合使用單個通用頻率合成器IC和一個外部壓控振蕩器(VCO)通常都可以

2019-07-08 06:10:06

DDS9850的原理是什么?怎樣去設計數字化可編程頻率合成器?DDS與使用PLL技術實現的頻率合成器相比,有哪些優勢?

2021-04-20 07:30:07

AD9914 / PCBZ,評估板,采用AD9914,3.5 GSPS直接數字頻率合成器,內置12位DAC。 AD9914是一款直接數字頻率合成器(DDS),具有12位DAC。 AD9914采用先進的DDS技術,并配有內部高速,高性能DAC,可形成數字編程

2019-03-01 08:00:00

頻率合成器的主要性能指標鎖相環頻率合成器原理鎖相環頻率合成器捕捉過程的分析與仿真

2021-04-22 06:27:35

AD9850 是AD I 公司采用先進的DDS 技術, 1996年推出的高集成度DDS 頻率合成器, 它內部包括可編程DDS 系統、高性能DAC 及高速比較器, 能實現全數字編程控制的頻率合成器和時鐘

2008-04-10 13:14:29 83

83 在介紹DDS 芯片STEL-1479 和PIC16C73A 單片機的基礎上,設計了一種利用單片機控制DDS 芯片實現的中波頻率合成器。進行了詳細的硬件和軟件設計,給出了具體的硬件電路及軟件流程。

2009-09-03 09:16:06 17

17 本文討論了DDS+PLL 結構頻率合成器硬件電路設計中需要考慮的幾方面問題并給出了設計原則,依此原則我們設計了一套短波波段頻率合成器,實驗結果證實了其可行性。

2009-09-07 16:07:29 34

34 直接數字合成(DDS)是近年發展起來的一種新型合成技術,有頻率分辨率高,轉換時間短,相位噪聲低等特點,與鎖相合成技術(PLL)配合,可以設計出頻帶寬、分辨率高的頻率

2009-09-11 15:55:32 13

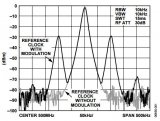

13 PLL頻率合成器的噪聲基底測量

在無線應用中,相位噪聲是頻率合成器的關鍵性能參數。像PHS、GSM和IS-54等相位調制蜂窩系統的RF系統設計均需要低噪聲本地振蕩(L

2010-04-07 15:25:21 22

22 直接數字合成(DDS)是近年發展起來的一種新型合成技術,有頻率分辨率高,轉換時間短,相位噪聲低等特點,與鎖相合成技術(PLL)配合,可以設計出頻帶寬、分辨率高的頻率合

2010-08-04 15:57:03 0

0 應用FPGA,采用PLL頻率合成技術,結合教學實驗平臺的需要,設計出了一個整數/半整數頻率合成器,輸出范圍為1kHz~999.5kHz,步進頻率可達到0.5kHz。與以前的教學實驗裝置相比,系統在性能指

2010-09-01 09:43:34 45

45 摘要:討論了DDS的工作原理及性能性點,介紹了目前實現DDS常用的三種技術方案,并對各方案的特點作了簡單的說明。 關鍵詞:直接數字頻率合成器 相位累加

2008-03-25 23:51:27 887

887

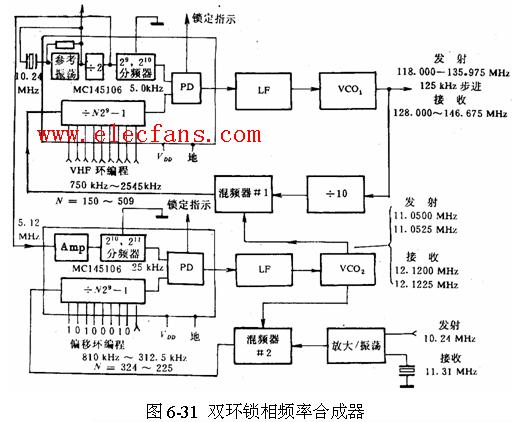

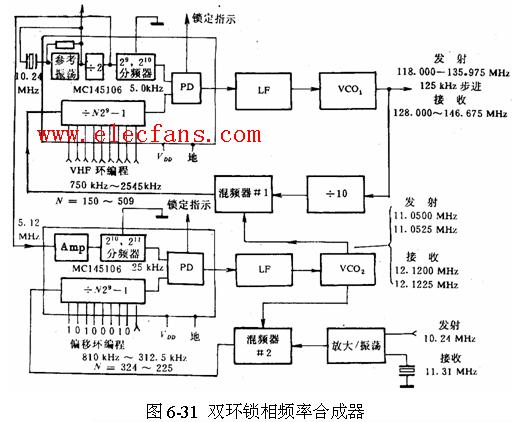

雙環鎖相頻率合成器

2008-04-21 14:38:36 1088

1088

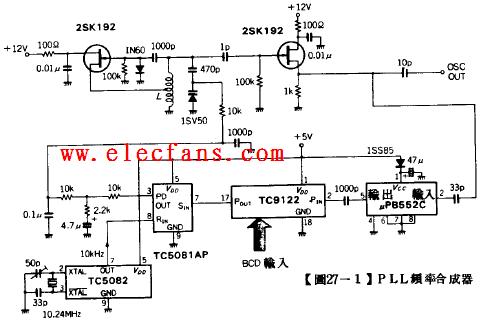

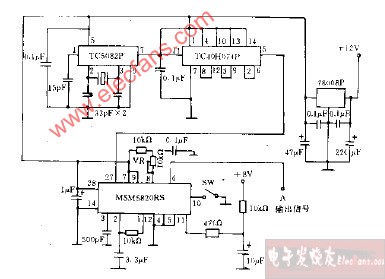

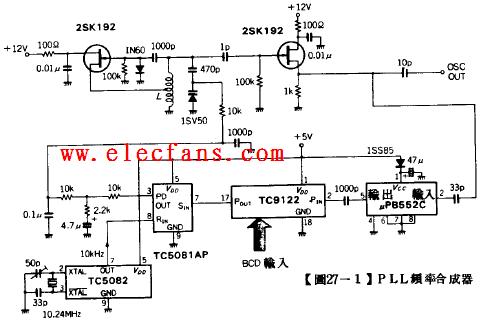

80M~120MHz頻帶PLL頻率合成器圖27-1為使用PLL IC TC9122(東芝)之80~120MHz的

2008-08-17 16:16:50 2106

2106

超高速頻率合成器方案的設計與實現

綜合考慮各個方案的優缺點,采用了一種DDS加倍頻鏈的合成方法,研制了105 跳/s的寬帶超高速頻率

2009-03-01 17:20:21 1143

1143 對CDMA手機頻率合成器的各關鍵部分進行分析,提出了設計方案。 關鍵詞:CDMA手機,射頻前端,頻率合成器,相位噪聲

2009-05-10 13:11:40 1253

1253

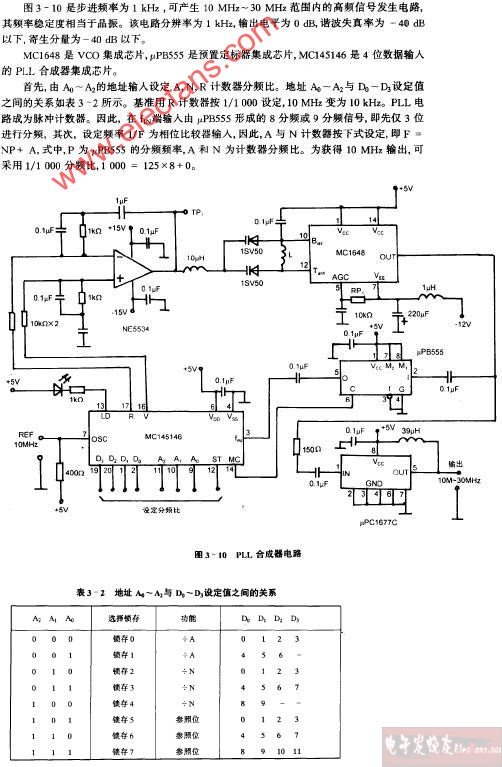

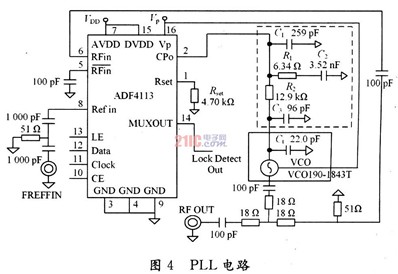

PLL合成器電路圖

2009-07-14 17:08:22 439

439

采用PLL的頻率合成器電路圖

2009-07-20 11:38:29 1118

1118

用AD9850激勵的鎖相環頻率合成器

提出了一種DDS和PLL相結合的頻率合成方案,介紹了DDS芯片AD9850的基本工作原理、性能特點及引腳功能,給出了以AD9850作

2009-12-08 15:27:31 1556

1556

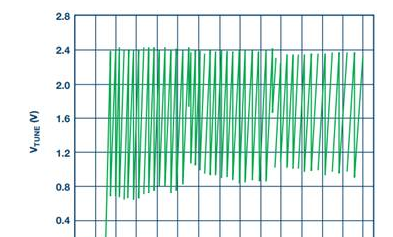

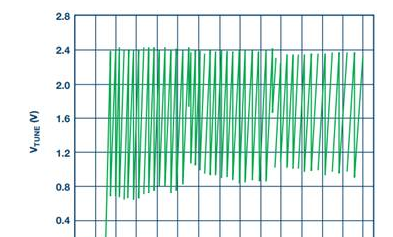

ADI推出的 ADF4158 PLL 合成器

ADI最新推出的 ADF4158 PLL 合成器,可靈活 、高性價比地實現 FMCW (頻率調制連續波)雷達系統。FMCW 雷達系統廣泛應用于汽車、航空、軍事、工業

2010-01-13 11:38:55 1287

1287 頻率合成器,頻率合成器原理及作用是什么?

所謂的頻率合成器,就是以一個精確度、穩定度極好的石英晶體振蕩器作為基準頻率,并利用加、減

2010-03-23 11:04:54 14601

14601 單環鎖相頻率合成器,單環鎖相頻率合成器是什么意思

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統的“心臟”。現代戰爭是

2010-03-23 11:36:28 883

883 集成鎖相環頻率合成器,什么是集成鎖相環頻率合成器

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統

2010-03-23 11:45:44 770

770 針對RF設計的新版PLL頻率合成器設計軟件

ADI全球領先的高性能信號處理解決方案供應商,和提供覆蓋整個RF信號鏈的RF IC功能模塊的全球領導者,最

2010-05-24 11:21:08 731

731 對體積、速度和省電的更進一步的要求推動了頻率合成器技術的發展。目前頻率合成器的一個明顯趨勢是集成了越來越多的微型鎖相環(PLL)/壓控振蕩器(VCO)元件。過去在PCB上的多個元

2010-05-28 11:11:31 1858

1858 全球領先的高性能信號處理解決方案和 RF IC供應商,最近推出一款用于無線通信系統的 PLL(鎖相環)頻率合成器ADF4351。

2011-06-21 16:50:02 2278

2278 針對高性能DDS芯片AD9858設計寬帶 頻率合成器 , 分析DDS的工作原理,給出寬帶頻率合成器的原理框圖和實現過程,并對軟件控制流程進行了詳細說明,結合理論對系統的相位噪聲和雜散

2011-06-22 10:49:03 50

50 本文將介紹DDS和PLL的工作原理,并結合一電臺(工作頻率2 MHz~500 MHz)的設計,給出DDS做參考的PLL頻率合成器的設計方案。

2011-07-18 09:38:02 3423

3423

雜散抑制是PLL 頻率合成器的幾個關鍵指標之一。在實際設計中,雜散的輸出種類比較多,產生的原因也各不一樣,但是它們中的大多數并不常見。首先從雜散的基本概念出發,詳細地介紹了

2011-09-01 16:34:56 68

68 同步多個基于DDS的頻率合成器AD9850

2011-11-29 16:03:42 56

56 隨著微電子技術的迅速發展,直接數字頻率合成器(Direct Digital Frequency Synthesis簡稱DDS或DDFS)得到了飛速的發展,它以有別于其它頻率合成方法的優越性能和特點成為現代頻率合成技術中

2012-03-30 11:38:22 2608

2608 摘 要:結合數字式頻率合成器(DDs)和集成鎖相環(PLL)各自的優點,研制并設計了以DDS芯片AD9954和集成鎖相芯片ADF4113構成的高分辨率、低雜散、寬頻段頻率合成器,并對該頻率合成器

2012-06-25 13:53:59 2540

2540

在非相參雷達測試系統中,頻率合成技術是其中的關鍵技術.針對雷達測試系統的要求,介紹了一種用DDS激勵PLL的X波段頻率合成器的設計方案。文中給出了主要的硬件選擇及具體電路設

2012-06-28 17:33:39 39

39 為了滿足寬頻段、細步進頻率綜合器的工程需求,對基于多環鎖相的頻率合成器進行了分析和研究。在對比傳統單環鎖相技術基礎上,介紹了采用DDS+PLL多環技術實現寬帶細步進頻綜,輸

2013-04-27 16:26:51 48

48 △∑小數頻率合成器中的小數分頻器設計設計方案、技術指標、調試等。

2016-05-24 10:03:05 9

9 DDS-PLL組合跳頻頻率合成器,有需要的都可以看看。

2016-07-20 15:48:57 42

42 學習單片機電路圖的很好的資料——DDS-PLL組合跳頻頻率合成器

2016-11-03 15:15:39 0

0 結合數字式頻率合成器(DDs)和集成鎖相環(PLL)各自的優點,研制并設計了以DDS芯片AD9954和集成鎖相芯片ADF4113構成的高分 辨率、低雜散、寬頻段頻率合成器,并對該頻率合成器進行了分析

2017-10-27 17:54:21 8

8 頻率合成器是決定電子系統性能的關鍵設備,隨著通信、數字電視、衛星定位、航空航天、雷達和電子對抗等技術的發展,對頻率合成器提出了越來越高的要求。頻率合成理論自20世紀30年代提出以來,已取得了迅速

2017-11-02 10:49:36 4

4 頻率合成器是決定電子系統性能的關鍵設備,隨著通信、數字電視、衛星定位、航空航天、雷達和電子對抗等技術的發展,對頻率合成器提出了越來越高的要求。頻率合成理論自20世紀30年代提出以來,已取得了迅速

2017-11-02 11:56:26 0

0 無線電系統會因為各種各樣的原因而采用基于鎖相環(PLL)技術的頻率合成器。PLL 的好處包括: (1)易于集成到 IC 中。 (2)無線信道間隔中的靈活性。 (3)可獲得高性能。 (4)頻率合成器

2017-11-16 15:28:13 15

15 頻率合成器主要有直接式、鎖相式、直接數字式和混合式4種。目前,鎖相式和數字式容易實現系列化、小型化、模塊化和工程化,性能也越來越好,已逐步成為最為典型和廣泛的應用頻率合成器[1]。本文主要采用集成鎖相環PLLphase-Lockde Loop芯片CD4046,運用FPGA來實現PLL頻率合成器。

2019-01-07 09:52:00 3076

3076

PLL頻率合成器和ADIsimFrequencyPlanner

2019-07-01 06:12:00 3764

3764 直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的雜散等。此類雜散是實際DDS設計中的 有限相位和幅度分辨率造成的結果。

2019-11-14 17:10:08 5173

5173

幾乎每個RF和微波系統都需要頻率合成器。頻率合成器產生本振信號以驅動混頻器、調制器、解調器及其他許多RF和。頻率合成器常被視為系統的心跳,創建方法之一是使用鎖相環(PLL)頻率合成器。傳統

2020-10-15 10:43:00 8

8 利用頻率合成器,你可以產生單一參考頻率的各種不同倍數的輸出頻率。其主要應用是為RF信號 的上變頻和下變頻產生本振(LO)信號。頻率合成器在鎖相環(PLL)中工作,其中鑒頻鑒相器(PFD)將反饋頻率

2020-10-12 10:43:00 0

0 要滿足苛刻的頻率合成器要求,通常需要做到一定程度的設計靈活性。基本的鎖相環(PLL)頻率合成器能以低成本、高空間效率、低功耗封裝提供合理的頻譜純度和頻率捷變,因此它在射頻(RF)系統核心位置發揮作用已經有段時間了。但是,在要求快速切換速度、低相位噪聲或低雜散信號電平的場合,有必要使用更為復雜的架構。

2020-09-29 10:44:00 2

2 AN-605: 同步多個基于DDS的頻率合成器AD9852

2021-03-19 09:08:03 0

0 UG-161:PLL頻率合成器評估板

2021-03-20 09:54:34 6

6 AN-1254: 同步多個基于DDS的頻率合成器AD9915

2021-03-20 19:59:38 2

2 ADF4107:PLL頻率合成器數據表

2021-04-14 09:44:36 8

8 ADF4106:PLL頻率合成器數據表

2021-04-29 08:52:36 12

12 ADF4108:PLL頻率合成器數據表

2021-05-19 18:23:27 13

13 圖1所示電路使用帶集成式VCO和外部PLL的ADF4350頻率合成器,通過隔離PLL頻率合成器電路與VCO電路將雜散輸出降至最低。集成PLL和VCO的器件可從數字PLL電路饋通至VCO,由于PLL

2021-05-28 17:50:57 7

7 直接數字頻率合成技術(DDS+PLL)資料下載。

2021-06-07 14:41:54 38

38 結合數字式頻率合成器(DDs)和集成鎖相環(PLL)各自的優點,研制并設計了以DDS芯片AD9954和集成鎖相芯片ADF4113構成的高分辨率、低雜散、寬頻段頻率合成器,并對該頻率合成器進行了分析

2021-06-08 14:07:08 3049

3049

ADF4107 PLL頻率合成器數據表

2021-06-18 10:01:57 7

7 pll頻率合成器工作原理與pll頻率合成器的原理圖解釋 我們要搞清楚pll頻率合成器工作原理與pll頻率合成器的原理圖就要先搞清楚pll和頻率合成器的概念。 頻率合成器:將一個高穩定度和高精度的標準

2023-02-24 18:19:52 8262

8262

MAX2902 ISM發送器設計用于與外部頻率合成器IC組合,形成完整的TX路徑方案。根據系統要求,可以使用小數N分頻或整數N分頻頻率合成器IC。了解兩種頻率合成器的通道步長、相位噪聲和PLL鎖定時間有何不同,對于確定哪種頻率合成器更適合特定應用是必要的。本說明將嘗試說明主要差異,以便正確選擇合成器。

2023-03-03 15:22:43 429

429

電子發燒友網站提供《一種用DDS激勵PLL的X波段頻率合成器的設計方案.pdf》資料免費下載

2023-10-24 09:10:26 4

4

電子發燒友App

電子發燒友App

評論