DDR存儲器的發展歷程

由于幾乎在所有要求快速處理大量數據(可能是計算機、服務器或游戲系統)的應用中都要求具有RAM(隨機存儲器),因而DDR存儲器也變得日益重要,其應用也更加廣泛。自問世以來,RAM就已經變得至關重要,主要因為它是一種能夠保存易失性信息的存儲器,并且可以以一種更快速、更直接的方式存取信息。當在數據計算的世界里談及系統速度和效率時,這一點顯得尤為重要。

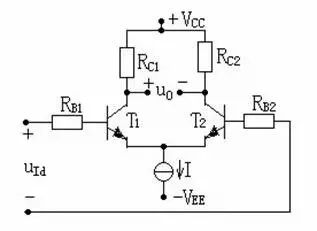

DDR SDRAM(雙數據速率同步動態隨機存儲器),其可以通過在時鐘周期的上升和下降沿上分別提取數據而使數據率加倍,現在看來它正發展成為最先進的RAM芯片集。這與以往的SDR SDRAM大不相同,因為后者僅能在時鐘周期的一個邊沿上提取數據。從圖1可以看出,DRAM正在向著速度和數據傳輸率都不斷提高的方向發展。

近些年來,CPU時鐘頻率經歷了指數增長,從而為RAM存儲器的時鐘頻率增長提供了動力。

在1997年,SD RAM在市場亮相,它可以取代DRAM和SRAM兩種存儲器并提供更快的時鐘速率。這主要源于SDRAM具有更簡捷的通信協議;所有指令、地址和數據都由一個單獨的時鐘信號控制并且工作在突發模式,可以在66MHz的時鐘頻率下突發一系列數據字。在1998年,SD RAM頻率已經增長到100MHz 的突發脈沖速率。

在1999年,英特爾和AMD間的企業競爭升級,在CPU時鐘速度方面也不例外。處理器行業的蓬勃發展進一步加大了CPU時鐘速度與其它系統組件間的差距。在此期間,盡管存儲器總線速度已經全力達到了133MHz,但卻仍然遠遠落后于CPU所能完成的速度,因此,總的來說,這也成為提高整體應用速度的瓶頸。

為了解決這個問題,DDR RAM(雙數據速率傳輸)的設計應運而生。DDR RAM允許分別在時鐘的上升沿和下降沿上提取數據,從而加倍了時鐘的有效傳輸速率。例如,一個100MHz的DDR時鐘能夠達到相當于200MHz時鐘頻率的峰值傳輸速率。這就是DDR1技術,其速度可高達400MHz。??

下一代DDR,即我們所說的DDR2。DDR2技術將數據傳輸速率從400MHz提升到800MHz,數據總線為64位(8字節)。它不能與前一代DDR1存儲器實現物理兼容,這種二代存儲器現在已經是由RAM存儲器廠商普遍生產的產品。

DDR3技術在2006年年底就已經投放使用,并補充了DDR2的不足(達到800Mbps的帶寬),將速度提升到1.6 Gbps。

除了眾所周知的PC應用,DDR存儲器還廣泛用于高速并對存儲器提出高要求的應用中,如:圖形卡、刀片式服務器、網絡裝置和通信裝置等。

在市場細分中,對速度和更低工作電壓都有苛刻要求的一個領域是便攜式消費領域。舉例來說,我們已注意到越來越多的電子元器件都能提供圖形和動態圖片(視頻)能力,從而滿足了我們對于更多DRAM存儲器的高需求。像PSP(便攜式游戲機)游戲系統、智能電話、數碼相機或GPS(全球定位服務)裝置等產品都會采用某種DRAM,而且都將要求盡可能低的功耗,以使電池的運行時間更長。

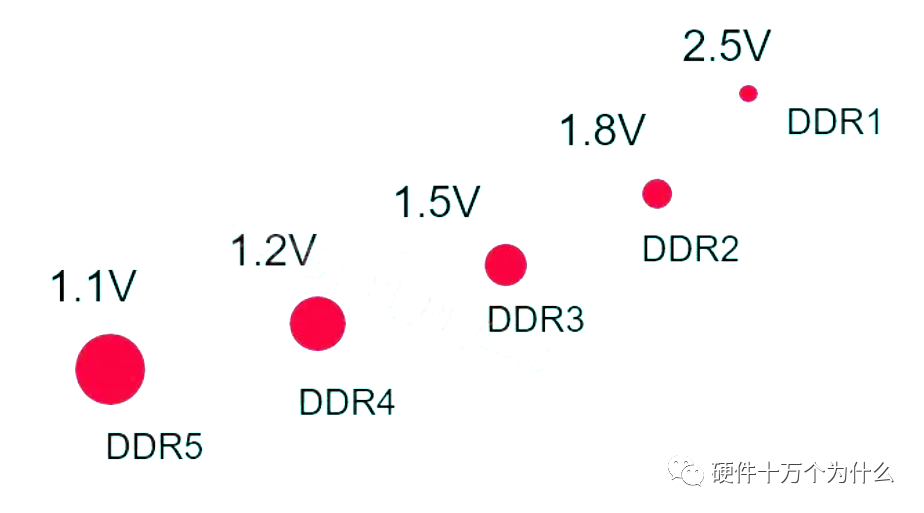

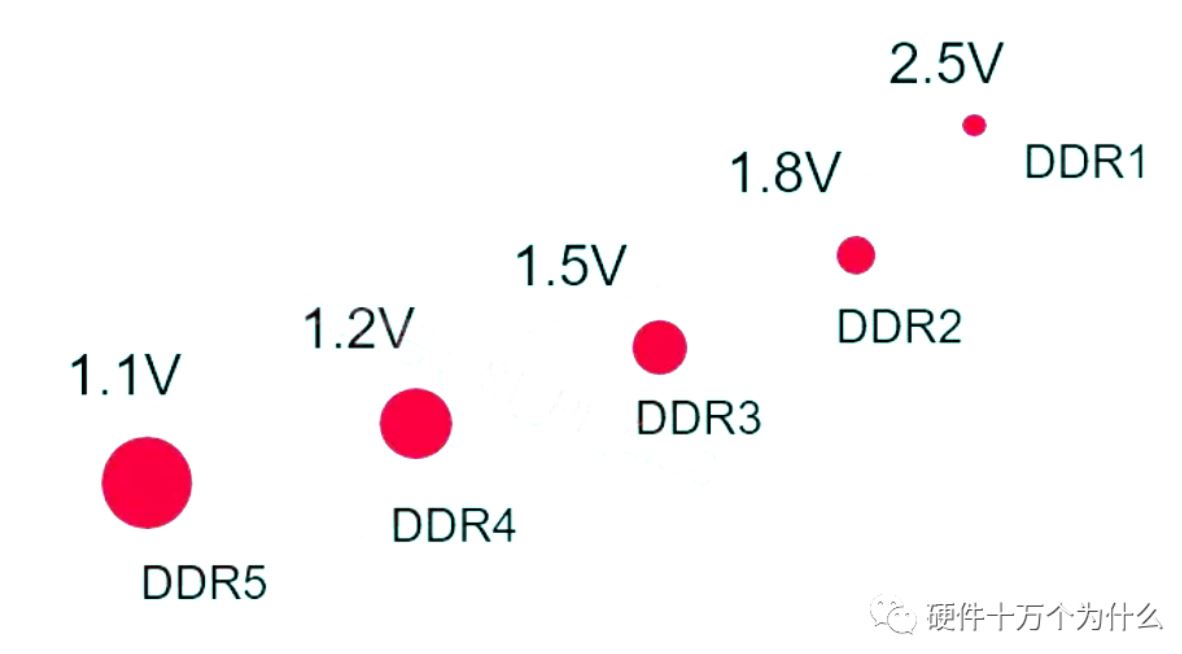

由于DDR存儲器數據速率隨著技術的發展而不斷提高,那么工作電壓也在隨之變化。目前用于驅動DDR3 SDRAM的DDR3標準電壓為1.5V(圖2)。因此我們注意到隨著標準的升級,新的技術正在推動電壓變得越來越低。

表1顯示了RAM存儲器芯片集在時鐘和轉換速率方面的簡要對比,這些芯片集主要用于當今的PC電腦,其中包括SDR、DDR1、DDR2和最新推出的DDR3模塊。

DDR標準

為了對DDR1、DDR2和DDR3 SDRAM間的差異進行比較,參考表2。

先將運行時鐘頻率或速度放在一邊,單從工作電壓這一點來看,我們能夠看出DDR1、DDR2和DDR3存儲器分別由2.8,1.8和1.5V的電壓來供電。因此,與使用3.3V電壓的SDRAM標準芯片集相比,這些存儲器在產生更少熱量同時還實現了更高的效率。DDR3通過采用 1.5V的工作電壓,消耗的功率比DDR2(采用1.8V)更少——較DDR2降低了16.3%。DDR2和DDR3存儲器都具有節能的特性,如采用了更小的頁面尺寸和有效的掉電模式。而且,DDR存儲器接口采用新的串聯端接邏輯(SSTL)拓樸,旨在提高抗噪性、增加電源抑制并通過更低的電源電壓來降低功耗(針對可比的速度)。另外值得注意的一點是,DDR3和DDR2 SDRAM支持片內端接,而DDR1 SDRAM不支持。

這些特性和功耗優勢使它們特別適合用于筆記本電腦, 服務器和低功率移動應用。

這里,我們總結了不同的DDR SDRAM的電源管理系統需求。SDRAM和目前正在應用的DDR SDRAM相比的主要差別是:

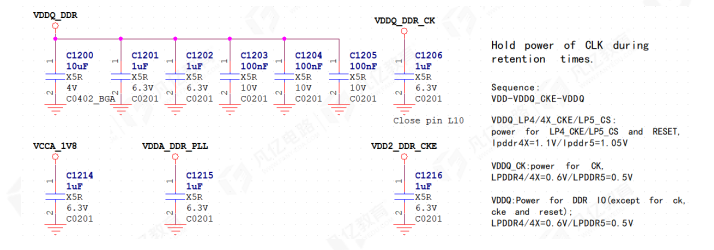

對于電源電壓,DDR SDRAM系統要求三個電源,分別為表3所列的VDDQ、VTT和VREF。

我們將深入研究需要這些電壓的原因。

盡管DDR存儲器在無需加倍時鐘頻率的情況下使數據傳輸率加倍,避免了PC板設計和布局的復雜性,但它要求有更嚴格的dc穩壓、更高的電流和對端電源電壓(VTT)和存儲總線電壓(VDD)緊密的跟蹤。新型串聯端接邏輯(SSTL)拓樸的引入是用于提高抗噪性、增加電源抑制并使用更低的電源電壓以降低功耗。

JEDEC標準JESD8-9A(用于SSTL_2)和JESD8-15(用于SSTL_18)定義了VDDQ、VTT和VERF以及驅動器/接收器規格以分別滿足在VDDQ= 2.5 V (用于 DDR1) 和VDDQ = 1.8 V (用于 DDR2)時的噪聲容限。下面,我們看看這種接口以更好的理解VREF和VTT的需要。

SSTL接口

圖3顯示了DDR存儲器的新型串聯端接邏輯(SSTL)拓樸。

SSTL_2的接口具有下述特性:

VTT電源的電流流向隨著總線狀態的變化而變化。因此,VTT電源需要提供電流和吸收電流 (source & sink),如圖4中紅色和藍色箭頭所示。

由于VTT電源必須在 1/2 VDDQ提供和吸收電流,因此如果沒有通過分流來允許電源吸收電流,那么就不能使用一個標準的開關電源。而且,由于連接到VTT的每條數據線都有較低的阻抗,因而電源就必須非常穩定。在這個電源中的任何噪聲都會直接進入數據線。

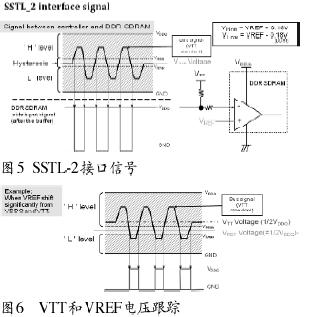

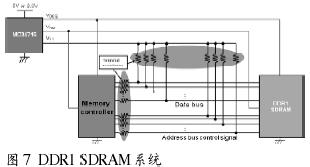

圖5詳細闡述了信號如何流過SSTL_2接口。

總線信號以VTT電壓為中心上下擺動。當總線信號電壓超過比較器的閥值電壓時,它將輸出一個如圖所示的反向電壓。在這個系統中,比較器的閥值電壓為電源所提供的VREF電壓。

由于在比較器中存在滯回現象,信號的圖片將有一個時間偏移,如圖所示。

因此,在VIHmin 和VIlmax之間,仍保持著先前的VTT狀態。

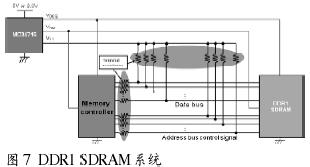

VTT和VREF的電壓跟蹤

為了保持信號的目標特性,VTT和VREF必須跟蹤VDDQ。它們必須控制在1/2 VDDQ的范圍內。

當VTT和VREF的跟蹤失效時,由于‘High ’和‘ Low ’的周期不同, 信號的目標特性將會惡化,從而引起定時漂移。

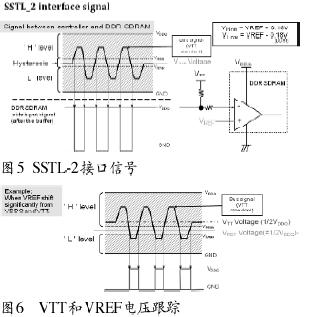

DDR1 SDRAM系統

在DDR1 SDRAM應用中,VTT被用來從電源IC中獲取電壓,以給數據總線和地址總線提供電源。

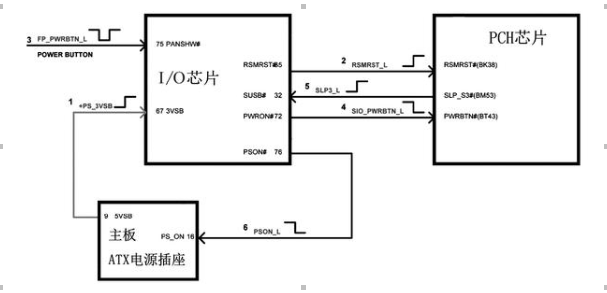

如圖7所示,地址指令和控制線要求系統級端口接到一個等于1/2存儲器電源電壓(VDDQ)的電壓(VTT)。在中點具有端電壓,電源保證轉換時間的對稱。

VTT被用來從電源IC中獲取電壓,以給數據總線和地址總線提供電源。對于DDR1 SDRAM應用中的地址總線控制信號和數據總線信號都有端接電阻。需要一個沒有任何的噪聲或者電壓變化的參考電壓(VREF),用作DDR SDRAM輸入接收器,VREF也等于1/2 VDDQ。VREF的變化將會影響存儲器的設置和保持時間。

為了符合DDR的要求并保證最優的性能,VTT和VREF需要在電壓、溫度和噪聲容限上進行嚴密的控制以便跟蹤1/2 VDDQ。

DDR2 SDRAM系統

我們將會看到兩個特別的例子,說明對于一個典型的DDR2系統,DDR總線如何連接。在下面描述的第一個存儲器應用示例中。用于數據總線的VTT由VDDQ在存儲器內通過ODT來生成。然而,有必要從電源IC中提供VTT來給地址總線控制信號。

注意:對于DDR2存儲器,內置有數據總線的端接電阻,但是在DDR1存儲器的應用中,仍需要用于地址總線控制信號的端接電阻。

現在,讓我們來看一種特殊情況,其中DDR2存儲器的應用連接不需要VTT電源和端電阻,在這種情況下,當控制器和存儲器之間的地址總線控制信號的導線長度足夠短的情況(如小于63.5mm);VTT的電源和端接電組是多余的。

從圖9可見,因為無需VTT,所以也無需源自電源芯片的VTT電源——標示為MC34716。

采用飛思卡爾DDR電源的應用示例

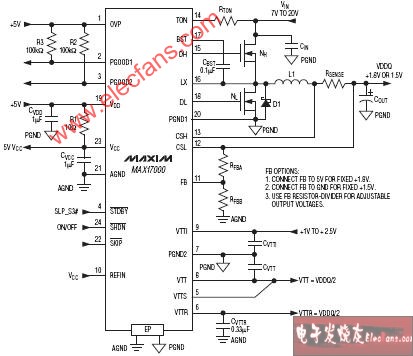

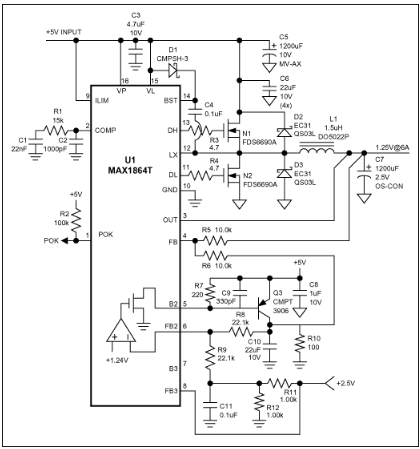

圖10為采用MC34712 & MC34713的DDR電源管理的應用示例。

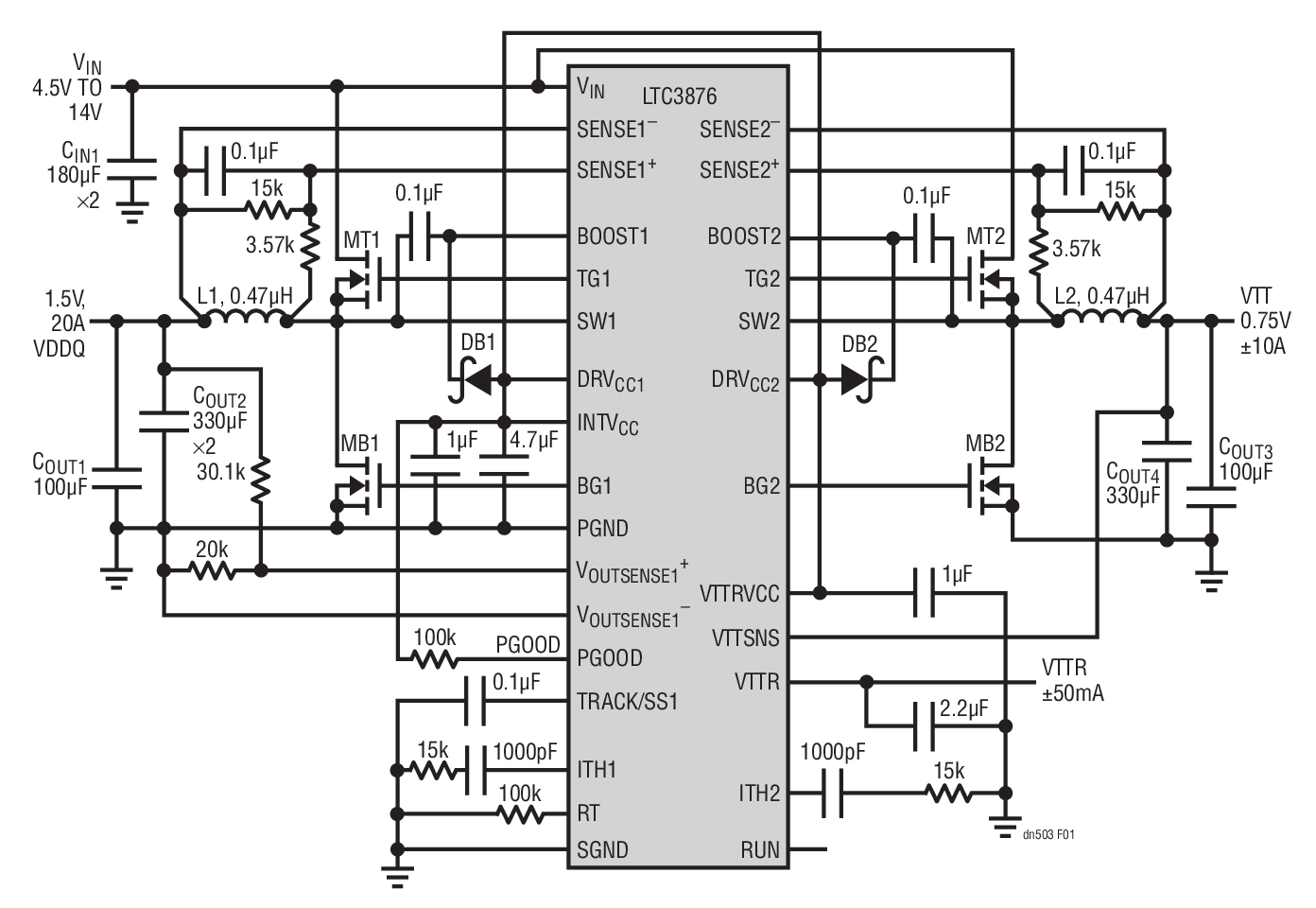

MC34713器件用作系統的VDDQ電源,其中用于DDR1的為2.5V,用于DDR2的為1.8V,而用于DDR3的為1.5V。MC34713產生了VDDQ然后將其注入MC34712。然后,MC34712跟蹤注入“VDDQ”以生成用于存儲器系統的VTT和VREF。此電壓將用作為用于DDR存儲器和電源和輸入參考電壓,如圖10所示。

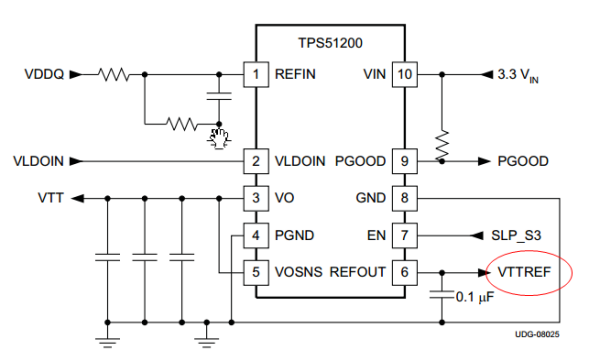

引腳“VREFOUT”直接與DDR存儲器的VREF相連接,提供一個等于1/2 VDDQ的穩定的參考電壓。

端口/SHTD,/STBY和PGOOD被用作接口,借助于一個DDR存儲器控制器與MCU相連接來控制DDR芯片集。

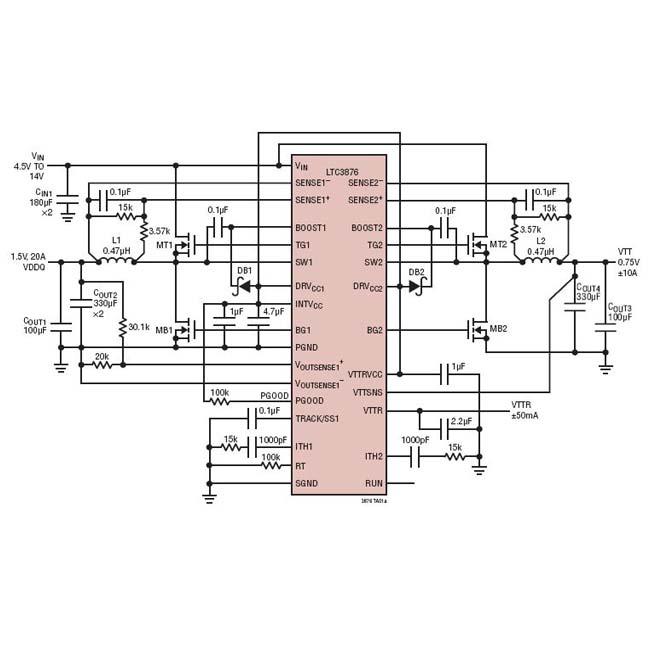

圖11是采用飛思卡爾MC34716的DDR存儲器電源管理的另外一個應用示例。

注意MC34716電源不依賴于DDR存儲器電源。在這種情況下,SW1將給DDR存儲器提供電源(VDDQ)。它也與MC34716上終端的VREFIN和PVIN2相連接。MC34716的端口的SW2為存儲器芯片數據總線提供VTT電壓,并跟蹤VDDQ來取得1/2 VDDQ。

引腳VREFOUT直接連接到DDR存儲器的VREF,提供一個穩定的等于1/2 VDDQ的參考電壓。

端口/SHTD,/STBY和PGOOD被用作接口,借助于一個DDR存儲器控制器與MCU相連接來控制DDR芯片集。

由于幾乎在所有要求快速處理大量數據(可能是計算機、服務器或游戲系統)的應用中都要求具有RAM(隨機存儲器),因而DDR存儲器也變得日益重要,其應用也更加廣泛。自問世以來,RAM就已經變得至關重要,主要因為它是一種能夠保存易失性信息的存儲器,并且可以以一種更快速、更直接的方式存取信息。當在數據計算的世界里談及系統速度和效率時,這一點顯得尤為重要。

DDR SDRAM(雙數據速率同步動態隨機存儲器),其可以通過在時鐘周期的上升和下降沿上分別提取數據而使數據率加倍,現在看來它正發展成為最先進的RAM芯片集。這與以往的SDR SDRAM大不相同,因為后者僅能在時鐘周期的一個邊沿上提取數據。從圖1可以看出,DRAM正在向著速度和數據傳輸率都不斷提高的方向發展。

近些年來,CPU時鐘頻率經歷了指數增長,從而為RAM存儲器的時鐘頻率增長提供了動力。

在1997年,SD RAM在市場亮相,它可以取代DRAM和SRAM兩種存儲器并提供更快的時鐘速率。這主要源于SDRAM具有更簡捷的通信協議;所有指令、地址和數據都由一個單獨的時鐘信號控制并且工作在突發模式,可以在66MHz的時鐘頻率下突發一系列數據字。在1998年,SD RAM頻率已經增長到100MHz 的突發脈沖速率。

在1999年,英特爾和AMD間的企業競爭升級,在CPU時鐘速度方面也不例外。處理器行業的蓬勃發展進一步加大了CPU時鐘速度與其它系統組件間的差距。在此期間,盡管存儲器總線速度已經全力達到了133MHz,但卻仍然遠遠落后于CPU所能完成的速度,因此,總的來說,這也成為提高整體應用速度的瓶頸。

為了解決這個問題,DDR RAM(雙數據速率傳輸)的設計應運而生。DDR RAM允許分別在時鐘的上升沿和下降沿上提取數據,從而加倍了時鐘的有效傳輸速率。例如,一個100MHz的DDR時鐘能夠達到相當于200MHz時鐘頻率的峰值傳輸速率。這就是DDR1技術,其速度可高達400MHz。??

下一代DDR,即我們所說的DDR2。DDR2技術將數據傳輸速率從400MHz提升到800MHz,數據總線為64位(8字節)。它不能與前一代DDR1存儲器實現物理兼容,這種二代存儲器現在已經是由RAM存儲器廠商普遍生產的產品。

DDR3技術在2006年年底就已經投放使用,并補充了DDR2的不足(達到800Mbps的帶寬),將速度提升到1.6 Gbps。

除了眾所周知的PC應用,DDR存儲器還廣泛用于高速并對存儲器提出高要求的應用中,如:圖形卡、刀片式服務器、網絡裝置和通信裝置等。

在市場細分中,對速度和更低工作電壓都有苛刻要求的一個領域是便攜式消費領域。舉例來說,我們已注意到越來越多的電子元器件都能提供圖形和動態圖片(視頻)能力,從而滿足了我們對于更多DRAM存儲器的高需求。像PSP(便攜式游戲機)游戲系統、智能電話、數碼相機或GPS(全球定位服務)裝置等產品都會采用某種DRAM,而且都將要求盡可能低的功耗,以使電池的運行時間更長。

由于DDR存儲器數據速率隨著技術的發展而不斷提高,那么工作電壓也在隨之變化。目前用于驅動DDR3 SDRAM的DDR3標準電壓為1.5V(圖2)。因此我們注意到隨著標準的升級,新的技術正在推動電壓變得越來越低。

表1顯示了RAM存儲器芯片集在時鐘和轉換速率方面的簡要對比,這些芯片集主要用于當今的PC電腦,其中包括SDR、DDR1、DDR2和最新推出的DDR3模塊。

DDR標準

為了對DDR1、DDR2和DDR3 SDRAM間的差異進行比較,參考表2。

先將運行時鐘頻率或速度放在一邊,單從工作電壓這一點來看,我們能夠看出DDR1、DDR2和DDR3存儲器分別由2.8,1.8和1.5V的電壓來供電。因此,與使用3.3V電壓的SDRAM標準芯片集相比,這些存儲器在產生更少熱量同時還實現了更高的效率。DDR3通過采用 1.5V的工作電壓,消耗的功率比DDR2(采用1.8V)更少——較DDR2降低了16.3%。DDR2和DDR3存儲器都具有節能的特性,如采用了更小的頁面尺寸和有效的掉電模式。而且,DDR存儲器接口采用新的串聯端接邏輯(SSTL)拓樸,旨在提高抗噪性、增加電源抑制并通過更低的電源電壓來降低功耗(針對可比的速度)。另外值得注意的一點是,DDR3和DDR2 SDRAM支持片內端接,而DDR1 SDRAM不支持。

這些特性和功耗優勢使它們特別適合用于筆記本電腦, 服務器和低功率移動應用。

這里,我們總結了不同的DDR SDRAM的電源管理系統需求。SDRAM和目前正在應用的DDR SDRAM相比的主要差別是:

- 電源電壓;

- 接口;

- 數據傳輸頻率。

對于電源電壓,DDR SDRAM系統要求三個電源,分別為表3所列的VDDQ、VTT和VREF。

我們將深入研究需要這些電壓的原因。

盡管DDR存儲器在無需加倍時鐘頻率的情況下使數據傳輸率加倍,避免了PC板設計和布局的復雜性,但它要求有更嚴格的dc穩壓、更高的電流和對端電源電壓(VTT)和存儲總線電壓(VDD)緊密的跟蹤。新型串聯端接邏輯(SSTL)拓樸的引入是用于提高抗噪性、增加電源抑制并使用更低的電源電壓以降低功耗。

JEDEC標準JESD8-9A(用于SSTL_2)和JESD8-15(用于SSTL_18)定義了VDDQ、VTT和VERF以及驅動器/接收器規格以分別滿足在VDDQ= 2.5 V (用于 DDR1) 和VDDQ = 1.8 V (用于 DDR2)時的噪聲容限。下面,我們看看這種接口以更好的理解VREF和VTT的需要。

SSTL接口

圖3顯示了DDR存儲器的新型串聯端接邏輯(SSTL)拓樸。

SSTL_2的接口具有下述特性:

- DDR存儲器具有推挽式的輸出緩沖,而輸入接收器是一個差分級,要求一個參考偏壓中點,VREF。因此,它需要一個能夠提供電流和吸收電流的輸入電壓端。

- 在驅動芯片集的任何輸出緩沖器和存儲器模塊上相應的輸入接收器之間,我們必須端接一個布線跟蹤或帶有電阻器的插頭。

VTT電源的電流流向隨著總線狀態的變化而變化。因此,VTT電源需要提供電流和吸收電流 (source & sink),如圖4中紅色和藍色箭頭所示。

由于VTT電源必須在 1/2 VDDQ提供和吸收電流,因此如果沒有通過分流來允許電源吸收電流,那么就不能使用一個標準的開關電源。而且,由于連接到VTT的每條數據線都有較低的阻抗,因而電源就必須非常穩定。在這個電源中的任何噪聲都會直接進入數據線。

圖5詳細闡述了信號如何流過SSTL_2接口。

總線信號以VTT電壓為中心上下擺動。當總線信號電壓超過比較器的閥值電壓時,它將輸出一個如圖所示的反向電壓。在這個系統中,比較器的閥值電壓為電源所提供的VREF電壓。

由于在比較器中存在滯回現象,信號的圖片將有一個時間偏移,如圖所示。

因此,在VIHmin 和VIlmax之間,仍保持著先前的VTT狀態。

VTT和VREF的電壓跟蹤

為了保持信號的目標特性,VTT和VREF必須跟蹤VDDQ。它們必須控制在1/2 VDDQ的范圍內。

當VTT和VREF的跟蹤失效時,由于‘High ’和‘ Low ’的周期不同, 信號的目標特性將會惡化,從而引起定時漂移。

DDR1 SDRAM系統

在DDR1 SDRAM應用中,VTT被用來從電源IC中獲取電壓,以給數據總線和地址總線提供電源。

如圖7所示,地址指令和控制線要求系統級端口接到一個等于1/2存儲器電源電壓(VDDQ)的電壓(VTT)。在中點具有端電壓,電源保證轉換時間的對稱。

VTT被用來從電源IC中獲取電壓,以給數據總線和地址總線提供電源。對于DDR1 SDRAM應用中的地址總線控制信號和數據總線信號都有端接電阻。需要一個沒有任何的噪聲或者電壓變化的參考電壓(VREF),用作DDR SDRAM輸入接收器,VREF也等于1/2 VDDQ。VREF的變化將會影響存儲器的設置和保持時間。

為了符合DDR的要求并保證最優的性能,VTT和VREF需要在電壓、溫度和噪聲容限上進行嚴密的控制以便跟蹤1/2 VDDQ。

DDR2 SDRAM系統

我們將會看到兩個特別的例子,說明對于一個典型的DDR2系統,DDR總線如何連接。在下面描述的第一個存儲器應用示例中。用于數據總線的VTT由VDDQ在存儲器內通過ODT來生成。然而,有必要從電源IC中提供VTT來給地址總線控制信號。

注意:對于DDR2存儲器,內置有數據總線的端接電阻,但是在DDR1存儲器的應用中,仍需要用于地址總線控制信號的端接電阻。

現在,讓我們來看一種特殊情況,其中DDR2存儲器的應用連接不需要VTT電源和端電阻,在這種情況下,當控制器和存儲器之間的地址總線控制信號的導線長度足夠短的情況(如小于63.5mm);VTT的電源和端接電組是多余的。

從圖9可見,因為無需VTT,所以也無需源自電源芯片的VTT電源——標示為MC34716。

采用飛思卡爾DDR電源的應用示例

圖10為采用MC34712 & MC34713的DDR電源管理的應用示例。

MC34713器件用作系統的VDDQ電源,其中用于DDR1的為2.5V,用于DDR2的為1.8V,而用于DDR3的為1.5V。MC34713產生了VDDQ然后將其注入MC34712。然后,MC34712跟蹤注入“VDDQ”以生成用于存儲器系統的VTT和VREF。此電壓將用作為用于DDR存儲器和電源和輸入參考電壓,如圖10所示。

引腳“VREFOUT”直接與DDR存儲器的VREF相連接,提供一個等于1/2 VDDQ的穩定的參考電壓。

端口/SHTD,/STBY和PGOOD被用作接口,借助于一個DDR存儲器控制器與MCU相連接來控制DDR芯片集。

圖11是采用飛思卡爾MC34716的DDR存儲器電源管理的另外一個應用示例。

注意MC34716電源不依賴于DDR存儲器電源。在這種情況下,SW1將給DDR存儲器提供電源(VDDQ)。它也與MC34716上終端的VREFIN和PVIN2相連接。MC34716的端口的SW2為存儲器芯片數據總線提供VTT電壓,并跟蹤VDDQ來取得1/2 VDDQ。

引腳VREFOUT直接連接到DDR存儲器的VREF,提供一個穩定的等于1/2 VDDQ的參考電壓。

端口/SHTD,/STBY和PGOOD被用作接口,借助于一個DDR存儲器控制器與MCU相連接來控制DDR芯片集。

電子發燒友App

電子發燒友App

評論