帶隙基準(zhǔn)廣泛應(yīng)用于模擬集成電路中。帶隙基準(zhǔn)電路輸出的基準(zhǔn)電壓可以為模擬集成電路提供穩(wěn)定的參考電壓或參考電流,

2023-07-06 10:42:01 1100

1100

概述:REF191是一款精密帶隙基準(zhǔn)電壓源芯片,它采用專利的溫度漂移曲率校正電路,激光微調(diào)高度穩(wěn)定的薄膜電阻,以實現(xiàn)非常低的溫度系數(shù)和較高的初始精度。REF191采用SOIC、TSSOP及DIP8腳封裝工藝;...

2021-04-13 06:00:16

概述:REF198是一款精密帶隙基準(zhǔn)電壓源芯片,它采用專利的溫度漂移曲率校正電路,激光微調(diào)高度穩(wěn)定的薄膜電阻,以實現(xiàn)非常低的溫度系數(shù)和較高的初始精度。REF198采用SOIC、TSSOP及DIP8腳封裝工藝;...

2021-04-14 07:34:35

帶隙基準(zhǔn)是什么?帶隙基準(zhǔn)的功能工作原理是什么?帶隙基準(zhǔn)的結(jié)構(gòu)是由哪些部分組成的?

2021-06-22 08:14:04

這是帶隙基準(zhǔn)仿真波形。這款帶隙基準(zhǔn)用于RFID芯片中,當(dāng)整流出來為周期性波動電壓時,供給帶隙后,帶隙輸出也會發(fā)生周期性抖動。在單仿帶隙時,DC仿真和瞬態(tài)仿真都沒有問題,可以穩(wěn)定輸出。但是如果瞬態(tài)加

2021-06-25 07:27:47

標(biāo)準(zhǔn)的帶隙基準(zhǔn),輸出電壓約為1.2V,10ppm左右。設(shè)計好,接入電路中,瞬態(tài)仿真,輸出電壓波形為以1.2V為直流,類似100MHz頻率的20mv峰值正弦波做周期等幅振蕩,可能的原因是什么。

2011-12-07 14:43:44

新型MCU怎么實現(xiàn)帶DRM的單芯片數(shù)字音頻解碼器?

2021-06-04 06:52:45

帶隙高于硅半導(dǎo)體的新型材料可縮減芯片尺寸,同時保持相同的隔離電壓。 較小的芯片產(chǎn)生較低的寄生電容,并降低了晶體管柵極電荷 (Qg) 及輸出電容 (Coss)。相比于標(biāo)準(zhǔn)的硅 MOSFET,在給定的頻率

2018-08-30 14:43:17

新型對講機(jī)電路設(shè)計利用F3140的模擬分時選通性質(zhì)組成聲控半雙工對講機(jī)電路,該電路輸出信號失真小、帶載能力強、傳輸速度快。[hide][/hide]

2009-12-17 11:12:39

工作站;適用于各種視頻ramdac;智能工業(yè)發(fā)射機(jī);PCMCIA卡;汽車;3 V/5 V,8位至12位數(shù)據(jù)轉(zhuǎn)換器。 一般說明 AD1580是一個低成本,2端(分路),精密帶隙基準(zhǔn)。它為50μA到10

2020-07-15 10:06:46

AD7674芯片使用外部基準(zhǔn)電壓,在ADC工作的時候基準(zhǔn)電壓對地值會被拉低,ADC不工作的時候恢復(fù)正常。ADC摘掉基準(zhǔn)電壓也恢復(fù)正常。

基準(zhǔn)電壓芯片位REF02,推測它的帶載能力不夠,在后面加了電壓跟隨電路。加入電壓跟隨電路后,基準(zhǔn)電壓正常工作,跟隨電路輸出電壓會被拉低。

請問如何解決?

2023-12-08 07:46:26

請教大家, N76E616 內(nèi)部帶隙電壓的存儲參數(shù)如何讀取?

2023-06-25 11:04:36

1. 看了V1.04的芯片手冊,但是沒看到 芯片內(nèi)部帶隙電壓的出廠校準(zhǔn)值 的存儲地址, 請問如何讀出帶隙電壓值?

2. 我將芯片內(nèi)存存儲器都用作APROM區(qū),請問我將最后1K區(qū)域當(dāng)做EEPROM來存儲參數(shù),要如何操作? 這個內(nèi)部APROM區(qū)域大概可以重復(fù)寫入多少次內(nèi)?

2023-06-27 06:20:00

REF191精密微功耗,低壓差電壓基準(zhǔn)的典型應(yīng)用。 REF19x系列精密帶隙電壓基準(zhǔn)采用獲得專利的溫度漂移曲率校正電路和高穩(wěn)定性薄膜電阻的激光微調(diào),可實現(xiàn)極低的溫度系數(shù)和高初始精度

2019-06-20 14:26:01

嗨,正在查看最新版本的STM8S003F3P6數(shù)據(jù)表,似乎沒有關(guān)于AIN7帶隙的評論。之前的數(shù)據(jù)表中提到過它(我有一個來自2014年)。帶隙是否正式出現(xiàn)在這個uC上?我的代碼顯示它在物理上存在

2019-02-28 16:22:05

最近diy制作一個USB電源電流表,使用的N76E003單片機(jī),液晶屏顯示部分程序,也弄好了,就差adc采樣了,想利用內(nèi)部帶隙電壓計算外部電壓值,不知道怎么計算,讀取UID最后兩個字,值為1663

2023-06-16 07:32:22

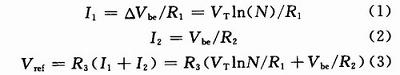

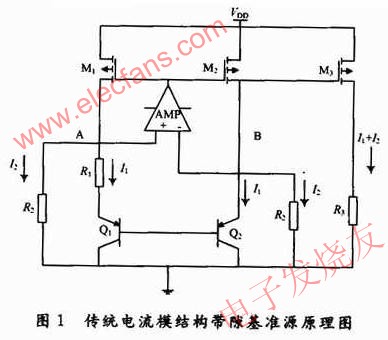

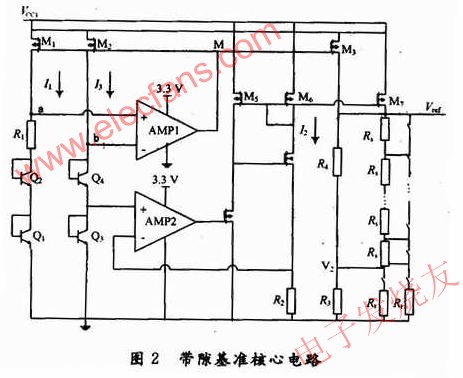

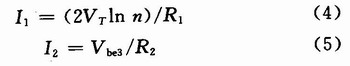

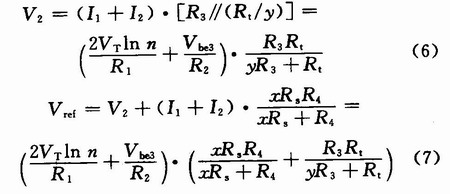

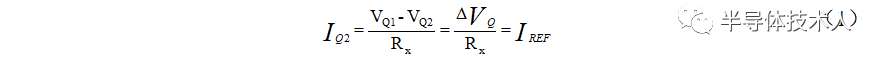

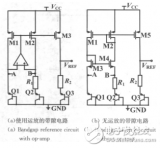

任意大小的基準(zhǔn)電壓。本文提出一種新的電流模帶隙結(jié)構(gòu)并采用一階溫度補償技術(shù)設(shè)計了一種具有良好的溫度特性和高電源抑制比,并且能快速啟動的新型BiCMOS帶隙基準(zhǔn)電路。該電路結(jié)構(gòu)簡單且實現(xiàn)了低輸出電壓的要求。

2019-07-12 07:36:42

傳統(tǒng)帶隙基準(zhǔn)源有哪些基本原理?什么樣的基準(zhǔn)源電壓才能滿足普通應(yīng)用要求?

2021-04-07 06:52:08

溫度系數(shù),而受控晶體管發(fā)射結(jié)具有負(fù)溫度系數(shù),,晶體管的負(fù)溫度系數(shù)是什么意思?而且要求電阻和發(fā)射結(jié)的總電壓達(dá)到硅管的能帶隙電壓此時整個電路不具有溫度系數(shù)?能帶隙電壓是什么?

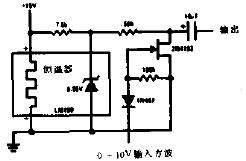

第二張圖,虛線框以內(nèi)是基準(zhǔn)源

2024-01-27 11:56:26

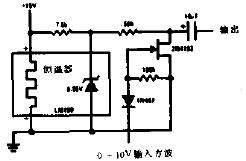

使用具有1.2外部帶隙基準(zhǔn)的TC7116模數(shù)轉(zhuǎn)換器的典型應(yīng)用(VIN- 與通用相連)

2019-07-26 08:35:49

M0518 ADC的內(nèi)部帶隙電壓是指什么?

2018-10-16 09:53:21

大家好,我有一個問題,配置PIC18F85 J94ADC。在第22.3.2頁中,從PIC18F97 J95家庭數(shù)據(jù)表中得知,內(nèi)部帶隙基準(zhǔn)電壓可用于ADC正基準(zhǔn)電壓。然而,在寄存器描述中沒有提到這樣

2019-01-29 06:04:01

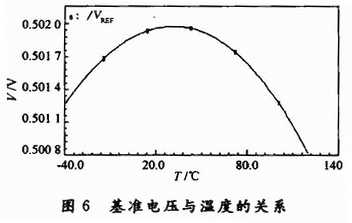

一種結(jié)構(gòu)簡單的基于LDO穩(wěn)壓器的帶隙基準(zhǔn)電壓源,以BrokaW帶隙基準(zhǔn)電壓源結(jié)構(gòu)為基礎(chǔ)來進(jìn)行設(shè)計。采用Cadence的Spectre仿真工具對電路進(jìn)行了完整模擬仿真,-20~125℃溫度范圍內(nèi),基準(zhǔn)

2018-10-09 14:42:54

一個可行的方法實現(xiàn)與溫度無關(guān)的電壓基準(zhǔn)可調(diào)帶隙基準(zhǔn)電壓電路分析及仿真

2021-04-08 06:59:00

帶曲率補償?shù)?b class="flag-6" style="color: red">帶隙基準(zhǔn)源的原理是什么?它與傳統(tǒng)帶隙基準(zhǔn)源相比有何不同?

2021-04-09 06:35:43

如果我們可以確定帶隙電壓和對應(yīng)的ADC原始數(shù)據(jù)那么我們就可以通過比例運算知道VCC,因為滿量程對應(yīng)的就是VCC,也就是0x0FFF對應(yīng)VCC

即VCC:0xFFF=帶隙電壓:帶隙電壓ADC

2023-06-25 08:18:31

為了解決傳統(tǒng)S/H電路失真大和靜態(tài)工作點不穩(wěn)定的問題,采用0.25 μm BiCMOS工藝,設(shè)計了一款高速率、高精度的10位全差分BiCMOS S/H電路。文中改進(jìn)型自舉開關(guān)電路和雙通道開關(guān)電容共模反饋電路(CMFB)設(shè)計具有創(chuàng)新性。

2021-04-21 06:24:21

帶隙高于硅半導(dǎo)體的新型材料可縮減芯片尺寸,同時保持相同的隔離電壓。 較小的芯片產(chǎn)生較低的寄生電容,并降低了晶體管柵極電荷 (Qg) 及輸出電容 (Coss)。相比于標(biāo)準(zhǔn)的硅 MOSFET,在給定的頻率

2022-11-16 06:48:11

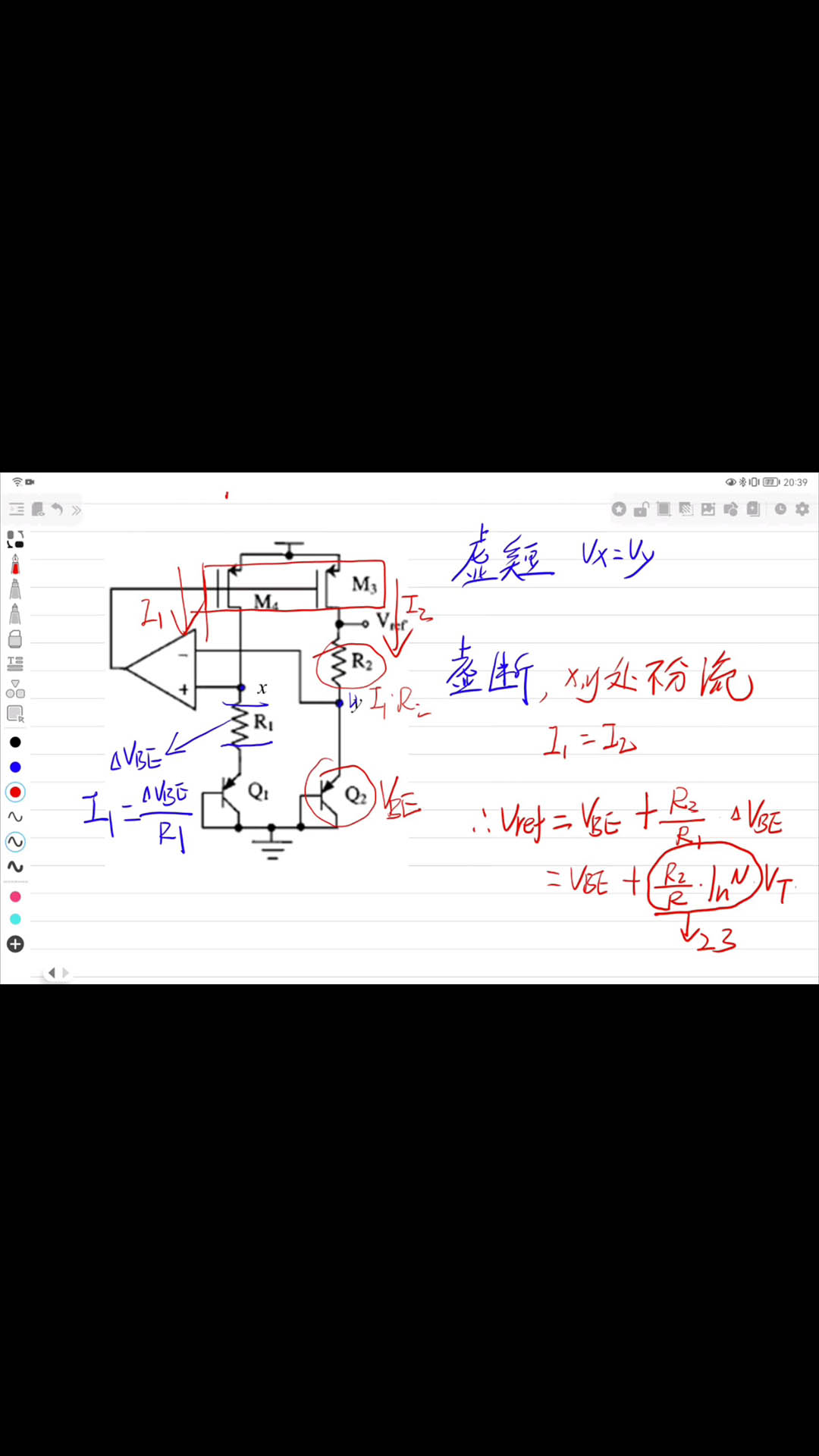

最近在做帶隙基準(zhǔn)源,用到AMP鉗位電壓,使倆點電壓一致,拉雜為沒講用到的AMP要有什么要求?但看到資料的電路基本都是單級AMP,想問下大大們,這個AMP鉗位電壓原理就是虛短虛斷么?(如果是要求增益應(yīng)該很大啊),還有那些要求?第一次發(fā)帖,小弟先謝了。

2022-06-15 10:26:32

。諧振型EBG結(jié)構(gòu)其周期單元本身具有諧振效果,在帶隙形成中起主要作用。新型EBG 結(jié)構(gòu)單元經(jīng)過專門設(shè)計,使該單位可以相當(dāng)于一個諧振效應(yīng)比較強的LC并聯(lián)電路。 由于EBG單元在諧振狀態(tài)下電抗為無窮大,因此

2018-09-28 16:18:59

氣隙的影響電機(jī)的氣隙

2021-01-22 06:15:07

帶隙基準(zhǔn)源原理是什么?雙極帶隙基準(zhǔn)電路的實際電路結(jié)構(gòu)是怎樣構(gòu)成的?怎樣對雙極帶隙基準(zhǔn)電路進(jìn)行仿真測試?

2021-04-21 06:20:19

帶隙基準(zhǔn)電壓源工作原理是什么?一種低溫漂輸出可調(diào)帶隙基準(zhǔn)電壓源的設(shè)計

2021-05-08 06:38:57

1,通過MS51FB9AE帶隙電壓(Band-gap)能反推出電源電壓,2,MS51FB9AE帶隙電壓(Band-gap)比較低,1.17V ~ 1.27內(nèi)3,如果我要偵測比較低的電壓(如50mV

2022-05-11 14:31:55

基準(zhǔn)電壓源是工藝、電源電壓、溫度變化時能夠提供穩(wěn)定輸出電壓的電路。基準(zhǔn)電壓源廣泛應(yīng)用于數(shù)據(jù)轉(zhuǎn)換器、智能傳感器、電源轉(zhuǎn)換器等電路。

基準(zhǔn)電壓源設(shè)計的要點是精度高,溫度漂移小,帶隙基準(zhǔn)電壓源利用硅的帶隙

2023-09-08 17:56:48

本帖最后由 萆嶶锝承鍩じ☆ve 于 2018-4-8 18:13 編輯

電壓基準(zhǔn)芯片的分類 根據(jù)內(nèi)部基準(zhǔn)電壓產(chǎn)生結(jié)構(gòu)不同,電壓基準(zhǔn)分為:帶隙電壓基準(zhǔn)和穩(wěn)壓管電壓基準(zhǔn)兩類。穩(wěn)壓管電壓基準(zhǔn)的基準(zhǔn)

2018-04-08 17:19:22

忽視或錯誤規(guī)定的長期漂移和遲滯能成為系統(tǒng)準(zhǔn)確度的限制。系統(tǒng)校準(zhǔn)雖然能夠消除 TC 和初始準(zhǔn)確度誤差,但只有頻繁的校準(zhǔn)才能消除長期漂移和遲滯。亞表齊納基準(zhǔn) (如 LT1236 ) 具有最好的長期漂移和遲滯特性,但它們不像這些新型帶隙基準(zhǔn)那樣能夠提供低輸出電壓選項、低電源電流和低壓工作電源。

2019-08-02 06:36:09

電源電壓變化時,帶隙基準(zhǔn)的輸出發(fā)生跳變,怎么減小帶隙基準(zhǔn)的過沖?謝謝

2021-06-24 06:46:07

AD7674芯片使用外部基準(zhǔn)電壓,在ADC工作的時候基準(zhǔn)電壓對地值會被拉低,ADC不工作的時候恢復(fù)正常。ADC摘掉基準(zhǔn)電壓也恢復(fù)正常。基準(zhǔn)電壓芯片位REF02,推測它的帶載能力不夠,在后面加了電壓跟隨電路。加入電壓跟隨電路后,基準(zhǔn)電壓正常工作,跟隨電路輸出電壓會被拉低。請問如何解決?

2018-07-24 10:40:58

最近diy制作一個USB電源電流表,使用的N76E003單片機(jī),液晶屏顯示部分程序,也弄好了,就差adc采樣了,想利用內(nèi)部帶隙電壓計算外部電壓值,不知道怎么計算,讀取UID最后兩個字,值為1663

2023-08-30 06:43:07

什么是帶隙電壓?

2020-12-23 07:27:58

請問仿真一個運放的輸入失調(diào)電壓是不是要做MC分析啊用在帶隙基準(zhǔn)中的運放,對于帶隙基準(zhǔn)的性能要求:-40~130溫度掃描,輸出電壓偏離小于3mv,電壓精度小于1mv,這樣的性能要求輸入失調(diào)電壓為多少?幾mv嗎,還是小于1mv?

2021-06-24 06:28:08

如何實現(xiàn)低電壓帶隙基準(zhǔn)電壓源的設(shè)計?傳統(tǒng)帶隙基準(zhǔn)電壓源的工作原理是什么?低電源帶隙基準(zhǔn)電壓源的工作原理是什么?

2021-04-20 06:12:32

如何讀取實際N76E003帶隙電壓?

2020-12-22 06:30:34

我們可以知道帶隙通道是 27 ,但是使用了 ADC0 或 ADC1?我都試過了,模擬總是零。

2023-04-25 09:30:23

帶隙放大器電路作為運放使用,請問該運放的輸出阻抗與跨導(dǎo)怎么分析,有沒有相關(guān)的資料?

2021-06-23 07:51:30

為什么要設(shè)計一種新型電壓基準(zhǔn)電路?怎樣去設(shè)計一種新型電壓基準(zhǔn)電路?

2021-04-22 06:37:20

各位大神,請問有沒有做過cadence的CMOS帶隙基準(zhǔn)電路設(shè)計,或者CMOS四運算放大器設(shè)計(LM324),求各位幫幫忙,我快山窮水盡了

2020-05-17 23:32:07

提高電源管理芯片精度和抗電磁干擾性能,結(jié)合降低電源待機(jī)功耗問題,設(shè)計了兩款電路:一款為高精度CMOS帶隙基準(zhǔn)電壓源電路。該電路能夠為開關(guān)電源芯片提供高精度高穩(wěn)定的基準(zhǔn)電壓,設(shè)計電壓值為1.25V.仿真

2020-07-23 15:04:30

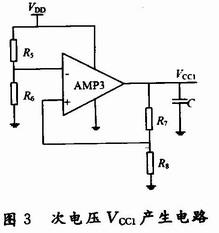

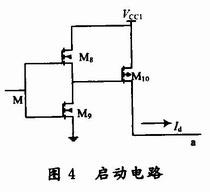

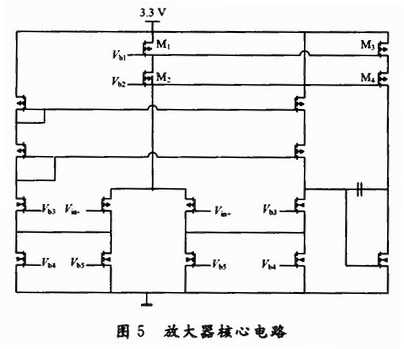

電子鎮(zhèn)流器芯片。本設(shè)計還優(yōu)化了啟動部分,使新的帶隙基準(zhǔn)可以在短時間內(nèi)順利啟動。 1 電路結(jié)構(gòu) 1.1 基準(zhǔn)核心 目前的基準(zhǔn)核心可以有多種實現(xiàn)方案:混合電阻,Buck voltage

2018-10-10 16:52:05

),沒有加電容,就參照上面的電路設(shè)計了。讓我們再進(jìn)一步的看一下REF50XX系列bandgap基準(zhǔn)源的內(nèi)部,如下圖,芯片內(nèi)部有一個1.2V的帶隙基準(zhǔn),和一個用于設(shè)置精確輸出電壓的放大器。這兩個就是基準(zhǔn)

2019-06-11 06:59:08

設(shè)計了一種采用BiCMOS工藝的高精度能隙基準(zhǔn)電壓電路,該基準(zhǔn)電壓源主要用于線性穩(wěn)壓器。在CSMC 0.6um工藝條件下,使用CADAENCE SPECTRE仿真工具進(jìn)行仿真可得溫度在20C~80C變化時,其輸

2009-08-17 10:10:02 17

17 超高速精確度模擬電路SOI上的5V互補SiGe BiCMOS技術(shù):本文介紹了一種新型的互補SiGe BiCMOS 技術(shù)。該技術(shù)帶有完全電介質(zhì)絕緣的 5V 多發(fā)射極 NPN和PNP 晶體管、5V CMOS、高精度 MIM 電容器、高

2009-09-23 09:22:30 21

21 基于0.6μm BiCMOS 工藝設(shè)計了一種無需基準(zhǔn)電壓源和比較器的高性能欠壓封鎖電路(UVLO)。利用帶隙基準(zhǔn)電壓源的原理,實現(xiàn)了欠壓封鎖的閾值點和遲滯量;而且?guī)?b class="flag-6" style="color: red">基準(zhǔn)電壓源結(jié)構(gòu)

2009-12-14 10:22:27 16

16 電壓基準(zhǔn)是模擬集成電路的重要單元模塊,本文在0.35um BiCMOS 工藝下設(shè)計了一個帶隙基準(zhǔn)電壓源。仿真結(jié)果表明,該基準(zhǔn)源電路在典型情況下輸出電壓為1.16302V,在-45℃~105℃范圍

2010-01-11 11:42:05 31

31 帶啟動遲滯的大電流驅(qū)動高壓基準(zhǔn)電路摘要:設(shè)計了一種具有大電流驅(qū)動能力的新型帶啟動遲滯的高壓基準(zhǔn)電路.該電路不僅極大地提高了傳統(tǒng)基準(zhǔn)電路的精度和

2010-04-27 10:53:51 19

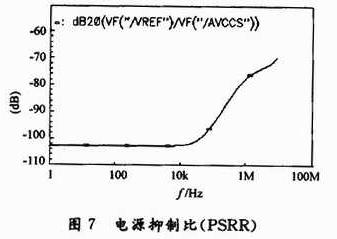

19 摘要:電源電壓的變化是影響帶隙基準(zhǔn)電路穩(wěn)定性的主要因素之一。本文針對該問題,在采用深度負(fù)反饋環(huán)路的基礎(chǔ)上,增加了一種提高電源電壓抑制比的電路結(jié)構(gòu)來降低電源變化

2010-04-28 09:32:30 13

13 一種BICMOS過溫保護(hù)電路

摘 要: 提出了一種用于集成電路內(nèi)部的過溫保護(hù)電路,采用0.8umBICMOS工藝的HSPICE仿真結(jié)果表明,此電路對因工藝參數(shù)或電壓變化而引起

2010-04-29 14:24:15 32

32 摘要:在分析現(xiàn)有過溫保護(hù)電路的基礎(chǔ)上,針對它們電路結(jié)構(gòu)復(fù)雜、功耗較高、工作電壓高等缺點提出了一種用于集成電路內(nèi)部的采用BiCMOS工藝的過溫保護(hù)電路,電路結(jié)構(gòu)簡單、功

2010-05-13 08:47:18 34

34 在對傳統(tǒng)典型CMOS帶隙電壓基準(zhǔn)源電路分析基礎(chǔ)上提出了一種高精度,高電源抑制帶隙電壓基準(zhǔn)源。電路運用帶隙溫度補償技術(shù),采用共源共柵電流鏡,兩級運放輸出用于自身偏置電路

2010-08-03 10:51:34 0

0 BiCMOS反相器

雙極型CMOS或BiCMOS的特點在于,利用了雙極型器件的速度快和MOSFET的功耗低兩方面的優(yōu)勢,因而這種邏輯門電路受到用戶的重視。

2009-04-06 23:31:02 5569

5569

BiCMOS門電路

根據(jù)前述的CMOS門電路的結(jié)構(gòu)和工作原理,同樣可以用BiCMOS技術(shù)實現(xiàn)或非門和與非門。如果要實現(xiàn)或非邏輯關(guān)系,輸入信號用來驅(qū)動并聯(lián)的N溝道MOSFET,而P溝道MO

2009-04-06 23:31:33 1914

1914

精密基準(zhǔn)方波基準(zhǔn)電壓源電路圖

2009-04-15 09:00:27 1216

1216

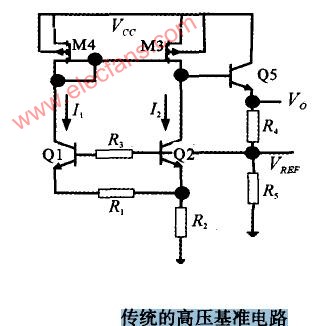

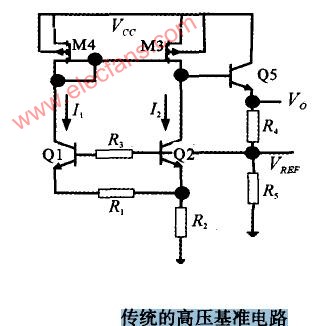

傳統(tǒng)高壓基準(zhǔn)電路原理

傳統(tǒng)的高壓基準(zhǔn)電路由三個NPN 管,兩個PMOS管以及五個電阻組成,如圖1所示

2010-04-27 11:04:19 813

813

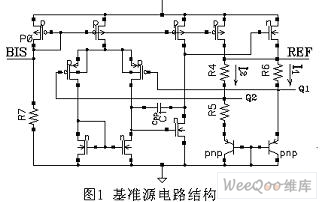

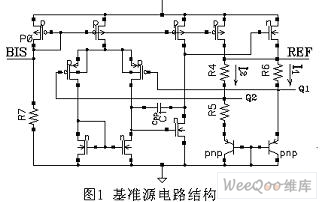

基準(zhǔn)源電路由二級CMOS差分放大電路和晶體管電路構(gòu)成的能隙基準(zhǔn)源組成。其結(jié)構(gòu)如圖1。

2010-08-17 10:59:11 1727

1727

本文設(shè)計了一種應(yīng)用于反熔絲型OTP存儲器的新型BiCMOS靈敏放大器電路。本設(shè)計的電路運用了BiCMOS技術(shù),以運放結(jié)構(gòu)為基礎(chǔ),結(jié)合預(yù)充電和放電控制機(jī)制,能夠?qū)⒕幊毯蟪矢咦杩範(fàn)顟B(tài)的反熔絲成功讀出

2016-06-22 09:58:46 1

1 一種新型的高電源抑制比基準(zhǔn)電流源電路的設(shè)計

2017-05-03 15:02:36 8

8 介紹了一種低溫漂的BiCMOS帶隙基準(zhǔn)電壓源及過溫保護(hù)電路。采用Brokaw帶隙基準(zhǔn)核結(jié)構(gòu),通過二階曲率補償技術(shù),設(shè)計的熱滯回差很好地防止了熱振蕩現(xiàn)象。

2017-09-07 20:15:25 24

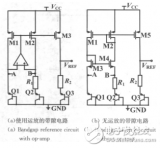

24 本文為大家介紹一個cmos無運放帶隙基準(zhǔn)源電路。

2018-01-11 16:52:50 14756

14756

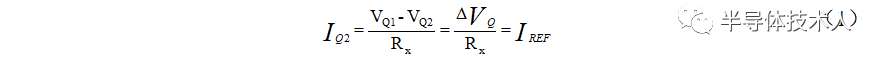

與溫度關(guān)系很小的電壓或者電流基準(zhǔn),在實際電路設(shè)計中具有重要的應(yīng)用,比如在電流鏡結(jié)構(gòu)中,需要對一“理想的”基準(zhǔn)電流進(jìn)行精確復(fù)制,這一“理想的”基準(zhǔn)電流,一般由帶隙基準(zhǔn)電路產(chǎn)生。

2023-07-06 11:32:14 2369

2369

電子發(fā)燒友App

電子發(fā)燒友App

評論