O 引言

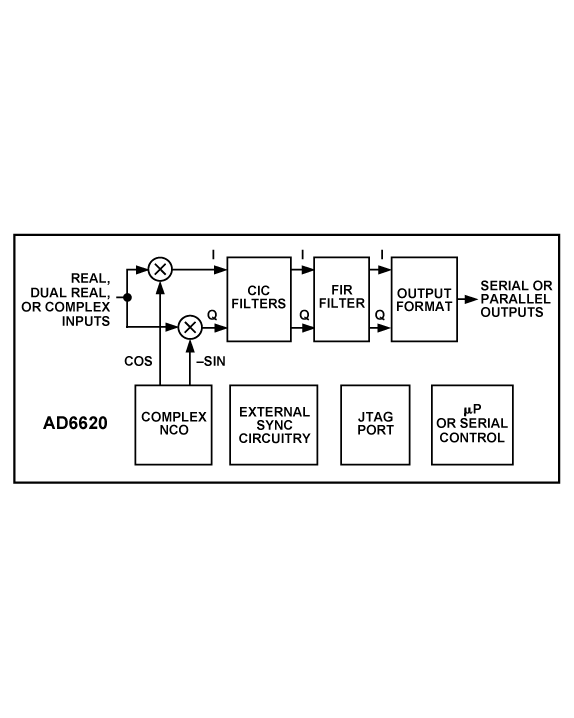

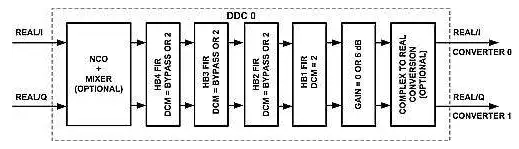

AD6620是一個(gè)寬帶中頻到基帶的解調(diào)器。它的內(nèi)部信號(hào)處理單元由四個(gè)串聯(lián)單元組成。分別為頻率變換單元、二階固定系數(shù)梳狀濾波抽取濾波器(CIC2)單元、五階固定系數(shù)梳狀濾波抽取濾波器(CIC5)單元和一個(gè)系數(shù)可編程的RAM系數(shù)抽取濾波器(RCF)單元。通過串行微處理器接口可以完成對(duì)芯片的編程和控制。

AD6620具有16位線性比特補(bǔ)碼輸入(另加3bit指數(shù)輸入),其單信道實(shí)數(shù)輸入模式的最大輸入數(shù)據(jù)速率可高達(dá)67 Msps,雙信道實(shí)數(shù)輸入模式與單信道復(fù)數(shù)輸入模式的最大輸入數(shù)據(jù)速率高達(dá)33.5 Msps。同時(shí),AD6620還具有可編程抽取FIR濾波器與增益控制功能,抽取率在2~163 84之間可編程;輸出具有并行、串行兩種輸出模式,并行模式為16比特補(bǔ)碼輸出。

1 頻率變換器的原理及配置

實(shí)現(xiàn)數(shù)字下變頻(DDC)的頻率變換器通常由兩個(gè)16 bit乘法器和32 bit的數(shù)控振頻器(NCO)組成。數(shù)控振蕩器產(chǎn)生的本振信號(hào)頻率的分辨率可達(dá)

為了提高NCO的雜散性能,AD6620提供有相位抖動(dòng)與幅度抖動(dòng)選項(xiàng)。另外,NCO的設(shè)置包括設(shè)置NCO頻率、NCO相位補(bǔ)償和NCO的特性以及相應(yīng)寄存器的配置。NCO的頻率可由下式計(jì)算:

將計(jì)算出的NCOFREQ轉(zhuǎn)換成二進(jìn)制后可寫入NCO頻率編程寄存器的0x303。NCO相位補(bǔ)償由16位NCO相位補(bǔ)償寄存器0x304來配置。0x0000表示沒有相位補(bǔ)償:0xFFFF表示補(bǔ)償為2p。相位補(bǔ)償寄存器允許多路NCO的同步來產(chǎn)生固定和已知相位偏移的輸出,一般取Ox0000。NCO的特性可根據(jù)NCO控制寄存器0x302的各個(gè)位的定義來設(shè)置。

2 CIC2抽取濾波器

CIC2濾波器是一個(gè)固定系數(shù)抽取濾波器,其最高輸入數(shù)據(jù)速率為67 MHz。抽取率的取值范圍為2~16的整數(shù)。當(dāng)系統(tǒng)時(shí)鐘fCLK是輸入數(shù)據(jù)速率的兩倍或更多倍時(shí),可以通過設(shè)置來屏蔽此工作模塊,否則,最小只能設(shè)置為2。

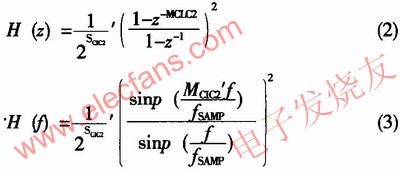

CIC2濾波器的頻率響應(yīng)函數(shù)為:

其中,SCIC2為幅度比例因子,可用來衰減CIC2濾波器的增益,MCIC2是抽取率。

CIC2濾波器的設(shè)置包括抽取率(MrCIC2 12bit),插補(bǔ)率(LrCIC2 8 bit)及比例因子(SrCIC25 bit)的設(shè)置。

設(shè)置時(shí)可首先確定通帶占用的采樣率百分比

根據(jù)采樣頻率為100’0.5625 MHz/25 MHz=2.25的值,可查表得到MrCIC2 12 bit/LrCIC2 9 bit的值。在實(shí)際應(yīng)用中,查到的值一般要大于等于BWfraction,在這里,BWfraction取2.25,查表得到MrCIC2 12 bit/LrCIC2 9 bit最大能取6,故取MrCIC2 12 bit/LrCIC2 9 bit為5。再取LrCIC2 9 bit為1.則MrCIC2 12 bit為5,rCIC2濾波器的輸出頻率frCIC2等于25 MHz/5,即12.5 MHz。這樣,即可將LrCIC2 9 bit 21寫入寄存器0x91,MrCIC2 12bit 21寫入寄存器0x90。

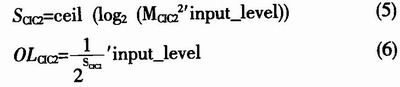

通常幅度比例因子可由式(5)和(6)給出:

因?yàn)镸rCIC2 12bit取5,LrCIC2 9 bit取1,所以,由上式可以計(jì)算出SrCIC2為5,這樣,便可將SrCIC2的值寫入寄存器。

3 CIC5抽取濾波器

CIC5是一個(gè)5階固定參數(shù)抽取濾波器,它的濾波特性曲線比CIC2的更為陡峭,可用來在CIC2后進(jìn)一步降低數(shù)據(jù)速率。CIC5抽取濾波器的抽取率可以取1~32范圍的任何整數(shù)值。當(dāng)抽取率為1時(shí),此時(shí)CIC5被屏蔽。CIC5的輸入頻率即是CIC2的輸出頻率。

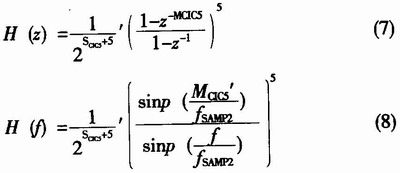

CIC5濾波器的頻響函數(shù)如下:

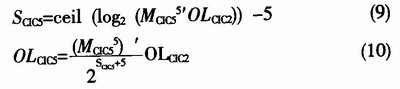

與配置CIC2類似,在配置CIC5時(shí),要確定的參數(shù)有抽取率和比例因子。抽取率的計(jì)算可采用與CIC2同樣的方法查出器件數(shù)據(jù)手冊(cè)中的對(duì)應(yīng)值.而比例因子則可由下式給出:

4 RAM系數(shù)濾波器

RAM系數(shù)濾波器是AD6620中最后一個(gè)信號(hào)處理功能模塊,它是一個(gè)積和形式的、系數(shù)可編程的濾波器。

數(shù)據(jù)存儲(chǔ)器I-RAM、Q-RAM存儲(chǔ)了256個(gè)有CIC5濾波器輸出的最新復(fù)數(shù)位采樣值,數(shù)據(jù)位寬度為20 Bit。在同一個(gè)時(shí)鐘周期,I路和Q路可以使用相同的系數(shù)作為濾波器系數(shù)進(jìn)行計(jì)算,也可以選用不同的系數(shù)進(jìn)行計(jì)算。I、Q路累加器輸出數(shù)據(jù)位寬為23 bit。取抽率可取1~256的整數(shù)值。

5 外部電路配置及內(nèi)部寄存器接入

AD6620工作時(shí)。需要正確搭建外部電路,同時(shí)還要按需配置內(nèi)部寄存器。

在配置AD6620的外部電路時(shí),需要確定它的工作狀態(tài)和輸出方式,其中輸出方式分為串行和并行兩種。每種輸出方式還應(yīng)配置I/Q路輸出指示和數(shù)據(jù)有效信號(hào)DVout。接收機(jī)系統(tǒng)選用并行輸出方式,由于AD9235只提供12位數(shù)字信號(hào),而AD6620可接收16位有效信號(hào)。故應(yīng)將高12位與AD9235相連,其余低位接地補(bǔ)零。

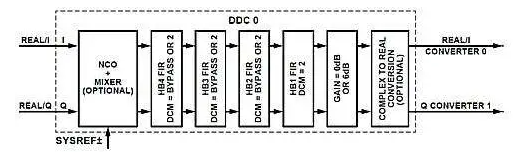

AD6620的工作模式分為主控(模式0)與從控(模式1)兩種,對(duì)于需要并行處理多路下變頻的復(fù)雜系統(tǒng)。只有一片AD6620工作在主控模式。

這兩種模式的區(qū)別在于主控模式。在數(shù)據(jù)處理的每一級(jí)工作完成后,會(huì)發(fā)出一個(gè)同步脈沖,以用于復(fù)雜系統(tǒng)多個(gè)AD6620之間的同步工作。與此對(duì)應(yīng)。從控模式的各級(jí)處理模塊只有在接到這個(gè)脈沖后,才能開始本級(jí)的處理,這樣才能以保證與其他AD6620芯片的工作協(xié)調(diào)。如主控模式二階梳狀濾波器CIC2完成其工作后,會(huì)向其他AD6620的SYNIC CIC2發(fā)出一個(gè)時(shí)鐘周期的脈沖信號(hào)以用于同步。由于接收機(jī)中只使用了一片AD6620,而無需等待其他芯片協(xié)同工作的同步脈沖,故配置為模式0,即主控模式。

AD6620的控制接口分串行輸入和并行輸入兩種。由于使用FPGA做芯片配置邏輯,所以,本文選用較靈活、效率較高的并行數(shù)據(jù)作為配置接口的邏輯輸入。

AD6620內(nèi)部各個(gè)模塊的配置寄存器并不是等位長的。具體各模塊內(nèi)部配置寄存器的位長見表l所列,而內(nèi)部寄存器的訪問則必須通過外部接口寄存器來指定地址,并由高位到低位按字節(jié)寫入。

外部接口寄存器的位長是固定的,按000到lll編址總共八個(gè)。其中低5位的5個(gè)寄存器是數(shù)據(jù)寄存器,可用于放入內(nèi)部某地址的不定長數(shù)據(jù)。而高兩位的兩個(gè)寄存器是地址寄存器,用于存放將要訪問的內(nèi)部寄存器的目標(biāo)地址,其中最高位111寄存器又和模式控制寄存器復(fù)用,且其最高兩位標(biāo)識(shí)為寫增長和讀增長,具體結(jié)構(gòu)如表2所列。

在寫寄存器的過程中,讀信號(hào)要保持高(失效)。RDY信號(hào)是AD6620給出的握手信號(hào),它會(huì)在寫信號(hào)WR有效之后變低,之后,根據(jù)目標(biāo)寄存器的不同,將在寫信號(hào)有效后最早3個(gè)周期內(nèi)再次升高,以表明寫入工作完成。

與寫寄存器過程相似,在讀寄存器過程中,寫信號(hào)也要保持高(失效),RDY信號(hào)是AD6620給出的握手信號(hào),它會(huì)在讀信號(hào)RD有效之后變低,之后再根據(jù)目標(biāo)寄存器的不同,在讀信號(hào)有效后3個(gè)周期到5個(gè)周期內(nèi)再次升高,以表明寫入工作完成。有效數(shù)據(jù)會(huì)在第N+2個(gè)時(shí)鐘周期后穩(wěn)定的保持在數(shù)據(jù)總線上。

為了使用FPGA來實(shí)現(xiàn)對(duì)AD6620的配置,在FPGA配置了一個(gè)FIFO以用于存放需要配置的所有寄存器的值。在RDY信號(hào)重新處于等待狀態(tài)時(shí)讀取該FIFO,可獲得下一個(gè)目標(biāo)寄存器的地址和寄存器內(nèi)的數(shù)據(jù)。

設(shè)計(jì)時(shí)可用QUARTUS II自帶的嵌入式邏輯分析儀SIGNAL-TAP來調(diào)試時(shí)序,以完成配置,圖1所示是一個(gè)完整的寄存器寫周期的各信號(hào)線采樣時(shí)序波形。

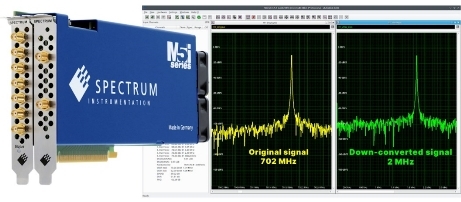

配置成功后的AD6620工作情況如圖2所示,從圖2中可以看到AD6620的輸入數(shù)據(jù)和AD6620的I,Q兩路的數(shù)據(jù)輸出,同時(shí)也可以觀察到各級(jí)同步信號(hào)的脈沖波形。

6 結(jié)束語

本文對(duì)新型ADC器件AD6620使用中的重點(diǎn)和難點(diǎn)問題,也就是AD6620的配置問題,給出了其實(shí)現(xiàn)方法,該方法具有一定的參考價(jià)值。事實(shí)上。該方法中的所有配置均已通過FPGA仿真驗(yàn)證。并在工作過程中按照實(shí)際運(yùn)行情況通過了Signal-TapII測試。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論