引言

轉(zhuǎn)換效率促使FPGA系統(tǒng)設(shè)計(jì)師從線性穩(wěn)壓器轉(zhuǎn)向使用開關(guān)模式直流-直流轉(zhuǎn)換器。雖然開關(guān)模式直流-直流轉(zhuǎn)換器能夠顯著提高效率,但卻需要更復(fù)雜的結(jié)構(gòu)設(shè)計(jì),更多的部件數(shù)量和更大的覆蓋區(qū);更為明顯的是,對(duì)高速輸入/輸出單元來說,開關(guān)模式直流-直流轉(zhuǎn)換器就等于噪聲源。

本文描述了開關(guān)模式直流-直流轉(zhuǎn)換器的各種噪聲分量,同時(shí)說明PowerSoC如何將各分量降至最低。本文也進(jìn)一步用設(shè)計(jì)示例來說明PowerSoC如何令高速輸入/輸出單元具有與線性穩(wěn)壓器媲美,甚至更優(yōu)越的性能。

降壓型直流-直流轉(zhuǎn)換器簡(jiǎn)單模型

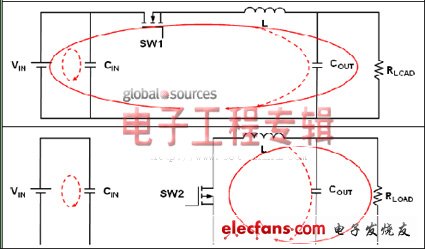

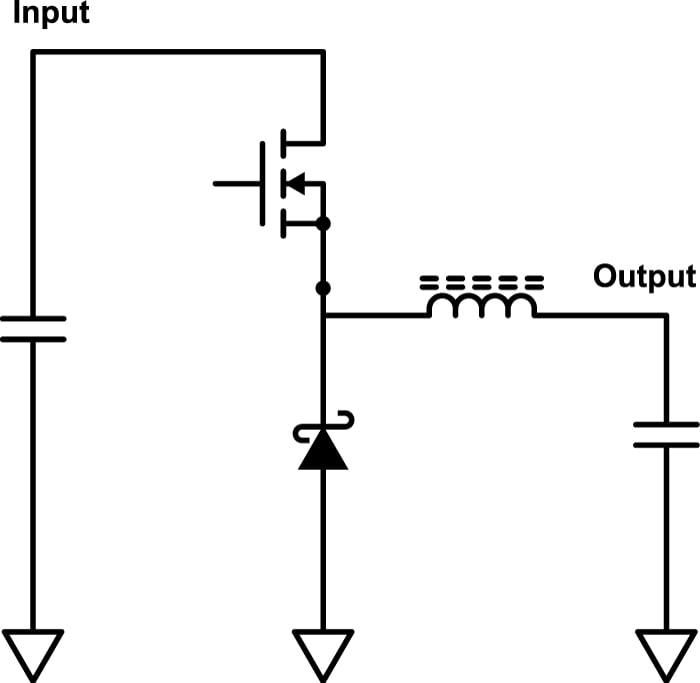

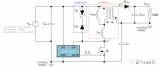

一對(duì)MOSFET開關(guān)、電感器,以及輸入和輸出濾波電容即可組成一個(gè)簡(jiǎn)易的同步開關(guān)模式直流-直流轉(zhuǎn)換器模型。圖1為轉(zhuǎn)換周期中的轉(zhuǎn)換器及其相關(guān)的直流和交流電流通路。當(dāng)SW1 閉合時(shí)(SW2開啟),電流從電源流經(jīng)電感器到達(dá)負(fù)載,輸入和輸出濾波電容實(shí)現(xiàn)高頻交流電流的"分流".當(dāng)SW2閉合時(shí)(SW1開啟),電感器儲(chǔ)存的電能在轉(zhuǎn)換周期的后半段為負(fù)載提供電流。開啟和閉合開關(guān)的動(dòng)作以及高頻交流電流的流動(dòng)都會(huì)產(chǎn)生噪聲。

?

圖1:同步降壓型直流-直流轉(zhuǎn)換器簡(jiǎn)化模型之完整轉(zhuǎn)換周期。紅色實(shí)線表示"直流"電流的流動(dòng)方向,而紅色虛線表示高頻交流電流的流動(dòng)方向。

直流-直流噪聲關(guān)鍵分量和降噪策略

降壓型直流-直流轉(zhuǎn)換器有效地將直流電壓"分成"交流電壓,然后轉(zhuǎn)換回到偽直流電壓。此過程產(chǎn)生了四種不同的噪聲:1) 轉(zhuǎn)換器直流輸出側(cè)的紋波電壓,2) 轉(zhuǎn)換器輸入電源側(cè)的紋波電壓,3) 輻射性電磁干擾,和4)傳導(dǎo)性電磁干擾。

輸出電壓紋波

每個(gè)被動(dòng)元件除了本身的基本功能(電阻、電容、電感)外,還具有另外兩個(gè)寄生元素:如果是電容,即為等效串聯(lián)電阻 (ESR) 和等效串聯(lián)電感 (ESL);如果是電阻,則是等效串聯(lián)電感和等效并聯(lián)電容。

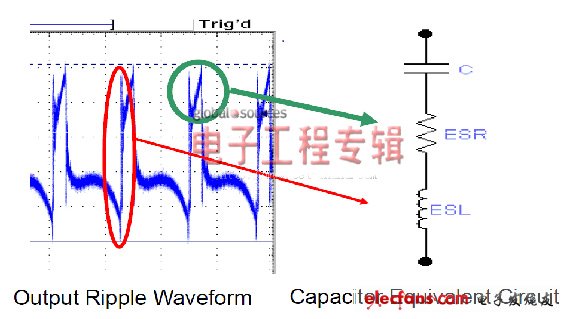

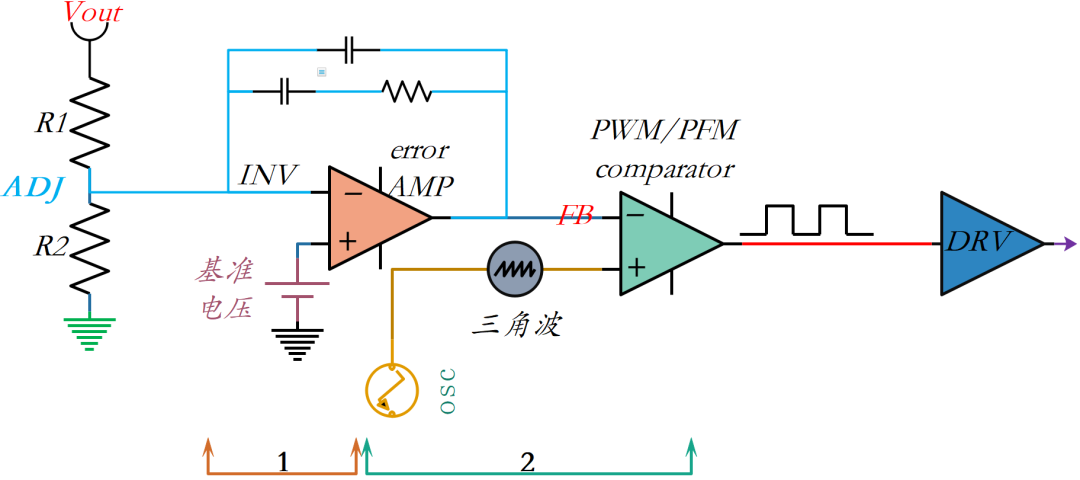

輸出紋波是交流紋波電流分流或流經(jīng)輸出濾波電容時(shí)的副產(chǎn)物。圖2展示了小型的輸出濾波電容信號(hào)模型,和該模型各成分對(duì)輸出紋波波形的作用。請(qǐng)注意輸出濾波電容的ESL是由PCB引線的寄生電感和轉(zhuǎn)換器的內(nèi)部寄生電感結(jié)合形成。ESL通過感應(yīng)"振動(dòng)"產(chǎn)生高頻尖峰信號(hào)。

?

圖2:輸出電壓紋波分量和來源

大多數(shù)直流-直流轉(zhuǎn)換器供應(yīng)商的數(shù)據(jù)表顯示了低通濾波紋波的波形,因此通常無法穩(wěn)定指示給定應(yīng)用情況中PCB上測(cè)量得到的實(shí)際紋波。

降噪策略

基本而言,要降低輸出紋波可通過減小紋波電流和 / 或降低電容器 的ESR和ESL以及PCB引線的ESL.

●在開關(guān)頻率較高的一側(cè)操作將降低給定電感值的紋波電流,從而可以使用較小且ESR/ESL較低的陶瓷電容。但開關(guān)頻率的升高會(huì)增加MOSFET開關(guān)的開關(guān)損耗,并影響效率。

●將多個(gè)電容并聯(lián)可降低ESR/ESL,就如將電阻并聯(lián)以降低其合成電阻一樣。隨著電容個(gè)數(shù)增加,PCB ESL增加,其效果受到限制,并且將增加轉(zhuǎn)換器的消耗。

●使用小尺寸的濾波元件(電感器和電容)可以減少PCB的長(zhǎng)度,從而降低PCB ESL.可惜小尺寸的電感器通常會(huì)導(dǎo)致紋波電流較大,但不增加開關(guān)頻率。

●使用兩級(jí)濾波,例如在直流-直流輸出濾波段和目標(biāo)負(fù)載之間使用鐵氧體磁珠和電容。這種方法的缺點(diǎn)在于額外的致?lián)p耗元件將影響調(diào)壓效果,并可能降低效率。

輸入電壓紋波

隨著SW1 MOSFET打開和閉合,電流從電源(VIN)流出,形成近似矩形的脈沖波形。上升和下降時(shí)間非常快,大約幾毫微秒。

與由輸出濾波電容和PCB引線ESL產(chǎn)生的輸出紋波相似,輸入濾波電容ESR和ESL,以及電源PCB引線ESL產(chǎn)生輸入紋波。然而,隨著電流時(shí)間比(di/dt)的變化增大,輸入電流紋波幅度要大的多。因此,PCB電感的影響更為重要,而輸入濾波電容必須耐受更高的RMS電流。又大又快的開關(guān)電流也是傳導(dǎo)性和輻射性EMI(稍后將探討)的主要來源。

降噪策略

●與輸出濾波電容一樣,在開關(guān)頻率較高的一側(cè)操作將可以使用較小且ESR/ESL較低的陶瓷輸入濾波電容。同樣應(yīng)注意開關(guān)損耗將變大。

●將輸入濾波回路中的寄生電感降至最低。這主要通過將濾波電容盡可能靠近直流-直流轉(zhuǎn)換器,以及盡可能短且寬的PCB引線來實(shí)現(xiàn)。通常不得將輸入濾波電容安裝在PCB的對(duì)邊且通過vias與直流-直流轉(zhuǎn)換器連接,否則會(huì)將大量電感引入電流回路中。

輻射性EMI

●又大又快的開關(guān)電流流經(jīng)輸入交流電流回路會(huì)產(chǎn)生輻射性EMI.如電磁場(chǎng)課程所述,環(huán)形天線的輻射效率是回路半徑相對(duì)于輻射波長(zhǎng)的函數(shù)。

?

●公式1列出了環(huán)形天線輻射產(chǎn)生的功率與半徑r和波長(zhǎng)λ的關(guān)系;h是自由空間常數(shù)。請(qǐng)注意回路半徑存在r8關(guān)系,而波長(zhǎng)存在λ4的關(guān)系。因此,在頻率較高的一側(cè)操作的顯著優(yōu)點(diǎn)是可使用較小尺寸的元件,以縮小輸入電流回路半徑。

降噪策略

減少輸入交流電流回路的半徑。通過在較高頻率一側(cè)開關(guān)以使用較小尺寸的陶瓷濾波電容,即可達(dá)到此目的。同樣應(yīng)注意,如上文所述,開關(guān)頻率越高,開關(guān)損耗也越大。

傳導(dǎo)性EMI

傳導(dǎo)性EMI有兩個(gè)主要來源:首先是輸入電壓干線產(chǎn)生的快速開關(guān)輸入電流,它會(huì)造成電源紋波(差模)和接地彈跳(共模)EMI;其次則是在電路板PCB引線上的電感器磁通泄漏耦合。

降噪策略

●使用大小合適的輸入濾波電容供應(yīng)或過濾高頻交流電源,以便盡可能降低電源干線上的電流。

●將輸入交流電流回路中的寄生電感和 ESL 降至最低。這可以通過在開關(guān)頻率較高的一側(cè)操作實(shí)現(xiàn),這樣就可以使用低 ESL 的陶瓷電容器,從而縮小回路半徑。需要再次強(qiáng)調(diào)的是開關(guān)頻率越高,開關(guān)損耗也越高。

●讓輸入濾波電容的 PCB 引線盡可能短且寬以降低引線電感。

●使用屏蔽式電感器以降低磁漏。

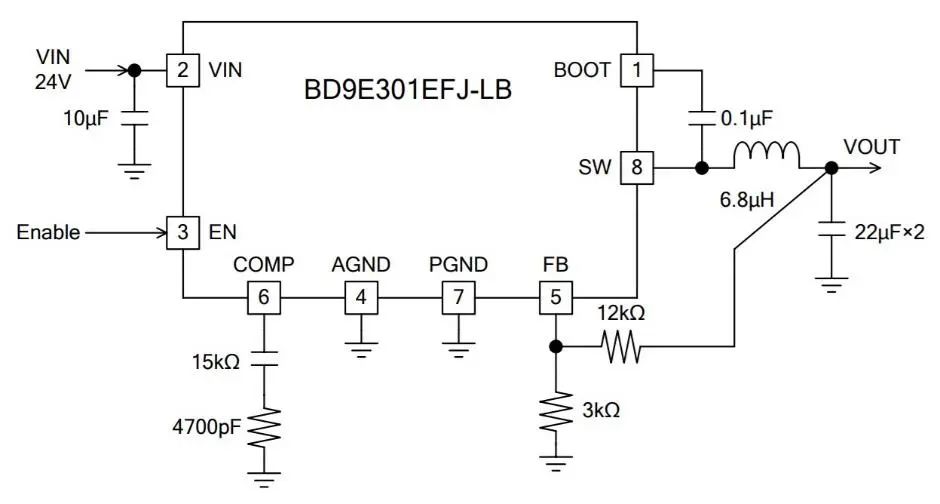

PowerSoC作為降噪策略

Enpirion于2004年推出全球第一個(gè)PowerSoC .PowerSoC在單個(gè)IC套件中集成了完整的直流 - 直流轉(zhuǎn)換器,包括控制器、柵極驅(qū)動(dòng)器、MOSFET開關(guān)、高頻去耦,以及最重要的電感器。大多數(shù) PowerSoC 只需要輸入和輸出濾波電容,因此整個(gè)解決方案既簡(jiǎn)單又輕巧。

●使用專用的深亞微米高頻 LDMOS 既可實(shí)現(xiàn)低開關(guān)損耗,又能集成整套的控制、驅(qū)動(dòng)和開關(guān)元件。低開關(guān)損耗可以實(shí)現(xiàn)高開關(guān)頻率,例如 5MHz.

●高密度、高磁導(dǎo)率、小體積的磁性元件可以實(shí)現(xiàn)最低的交流損耗和低直流電阻。小體積的磁性元件和磁結(jié)構(gòu)具有自屏蔽特性,可以降低磁漏。高開關(guān)頻率則允許使用尺寸非常小的電感器。

●高開關(guān)頻率還允許使用小型的輸入和輸出濾波電容,這樣一來,可以縮小輸入和輸出交流回路的尺寸,從而降低紋波和 EMI.

●套件布線經(jīng)過設(shè)計(jì)可進(jìn)一步縮小輸入和輸出交流濾波回路的半徑,從而盡可能降低輻射性和傳導(dǎo)性 EMI 以及紋波。

●套件設(shè)計(jì)包括射頻技術(shù),旨在盡可能降低內(nèi)部電路元件內(nèi)的寄生阻抗以保持套件內(nèi)的高頻交流電源。

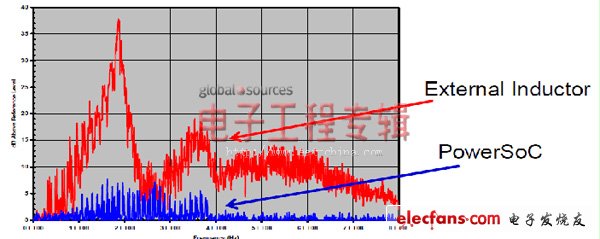

PowerSoC結(jié)果與離散實(shí)現(xiàn)方案

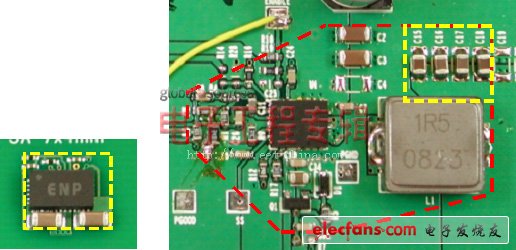

圖3–6展示了 PowerSoC 與離散式直流 - 直流轉(zhuǎn)換器實(shí)現(xiàn)方案的對(duì)比結(jié)果。

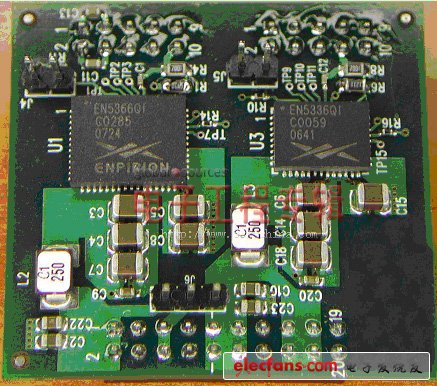

?

圖3:典型4A大小的轉(zhuǎn)換器解決方案區(qū)域?qū)Ρ取owerSoC(左圖)的輸入和輸出交流電流回路非常小,相當(dāng)于典型離散式實(shí)現(xiàn)方案尺寸的1/7.

黃色虛線方框表示PowerSoC尺寸和離散式直流-直流轉(zhuǎn)換器的對(duì)比結(jié)果。

?

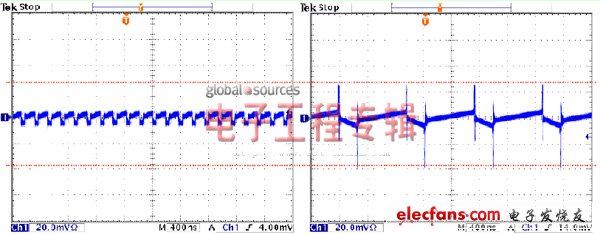

圖4:PowerSoC(左圖)與離散式直流-直流轉(zhuǎn)換器實(shí)現(xiàn)方案(右圖)的輸出紋波電壓對(duì)比。二者使用相同的設(shè)備和技術(shù)在供應(yīng)商評(píng)估板上測(cè)量紋波。測(cè)量帶寬為500MHz.

?

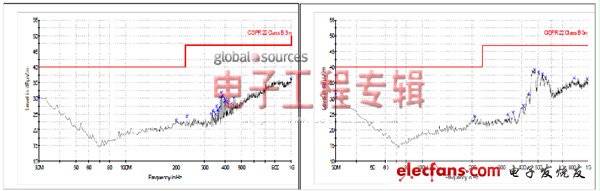

圖5:輻射性EMI測(cè)量結(jié)果;CISPR22 B等級(jí)3m.左圖為PowerSoC,右圖為離散式實(shí)現(xiàn)方案,均在供應(yīng)商評(píng)估板上測(cè)量得出。

?

圖6:輸入接地端子上測(cè)量的傳導(dǎo)性干擾

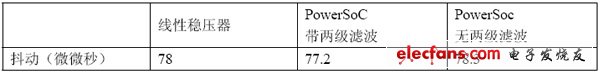

采用Enpirion PowerSoC的供電Rocket IO應(yīng)用實(shí)例

設(shè)計(jì)制造的子板插到Virtex 5開發(fā)板上(圖7)。對(duì)采用Enpirion裝置驅(qū)動(dòng)的開發(fā)板和線性穩(wěn)壓器執(zhí)行同樣的抖動(dòng)測(cè)量。分別測(cè)量Enpirion PowerSoC有兩級(jí)濾波和無兩級(jí)濾波的效果。抖動(dòng)測(cè)量結(jié)果如表1所示。

表1. Rocket IO的抖動(dòng)測(cè)量結(jié)果

?

?

圖7:帶Enpirion PowerSoC的子板

結(jié)論

對(duì)FPGA設(shè)計(jì)師而言PowerSoC代表強(qiáng)效的新型工具。這種裝置能夠有效減少從基于線性穩(wěn)壓器的電壓轉(zhuǎn)換器向更高效的開關(guān)模式轉(zhuǎn)換器轉(zhuǎn)變過程中面臨的諸多問題。 PowerSoC具有和線性穩(wěn)壓器相似的覆蓋區(qū)域,易于設(shè)計(jì),同時(shí)也擁有開關(guān)模式轉(zhuǎn)換器的高效率,卻可免去離散式轉(zhuǎn)換器實(shí)現(xiàn)方案的噪聲和復(fù)雜度。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論