因為電容器的基本功能是儲存電荷,所以理想的去耦電容器可以提供邏輯裝置進(jìn)行狀態(tài)變換時所需的所有電流。 其中,ΔI為轉(zhuǎn)換電流;ΔV為允許供電電壓的改變(波動);ΔT為切換時間。 例:如果設(shè)計中允

2018-11-23 16:00:55

對于CYD36S72V18,對于電源去耦和處理未使用的引腳,您有什么建議?謝謝,豐富的

2019-10-22 06:31:35

何謂正確去耦?有何必要性? 如果電源引腳上存在紋波和/或噪聲,大多數(shù)IC都會有某種類型的性能下降。數(shù)字IC的噪聲裕量會降低,時鐘抖動則可能增加。對于高性能數(shù)字IC,例如微處理器和FPGA,電源額定容

2018-12-05 09:21:51

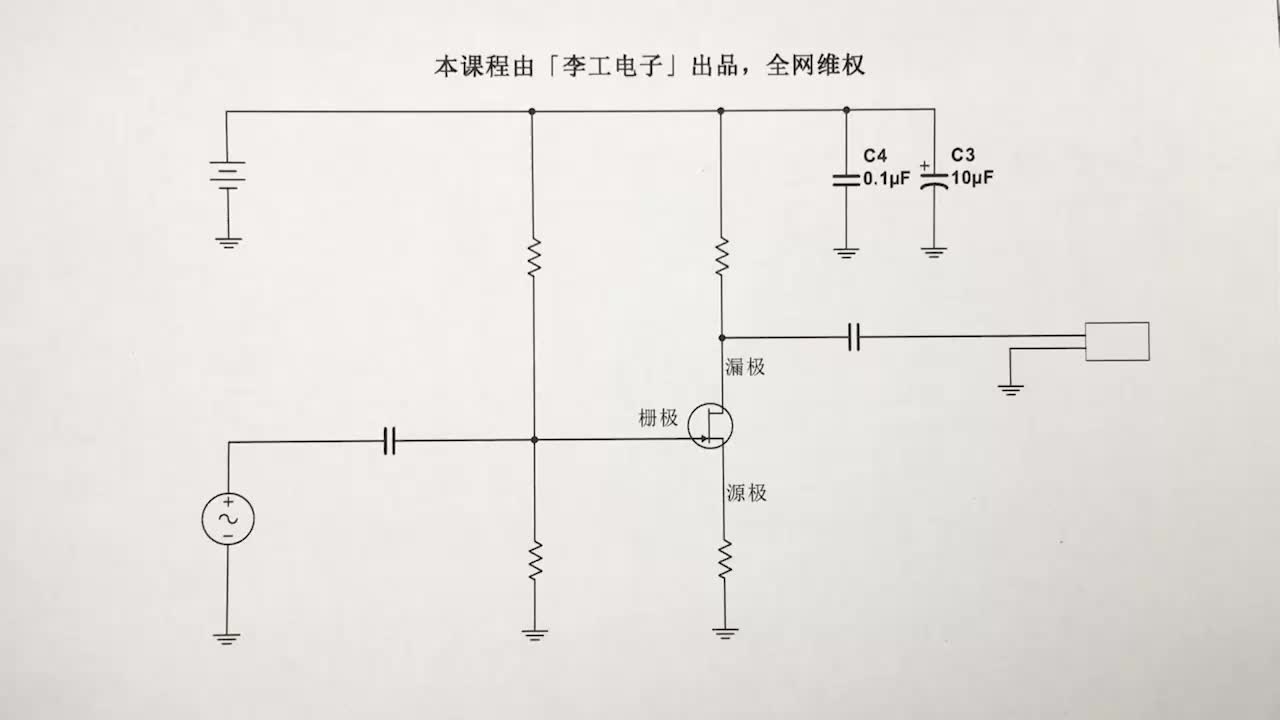

旁路電容是把電源或者輸入信號中的交流分量的干擾作為濾除對象;去耦電容是芯片的電源管腳,兩者有啥區(qū)別了?詳細(xì)請看附件(內(nèi)有福利哦~~)

2021-09-08 10:02:18

` 本帖最后由 eehome 于 2013-1-5 10:08 編輯

去耦電容和旁路電容的區(qū)別`

2012-08-14 11:49:42

去耦電容分為哪幾種?如何去放置去耦電容呢?在設(shè)計中如何防止上電及正常工作時出現(xiàn)總線沖突呢?

2021-11-03 07:17:04

“自偏”,但是對(交流)信號而言,這同時又是一個負(fù)反饋,為了消除這個影響,就在這個電阻上并聯(lián)一個足夠大的點容,這就叫旁路電容。后來也有的資料把它引申使用于類似情況。 去耦電容在集成電路電源和地之間

2012-03-08 23:42:09

下一級電路來說,它又是旁路電容。我們經(jīng)常可以看到,在電源和地之間連接著去耦電容,它有三個方面的作用:一是作為本集成電路的蓄能電容;二是濾除該器件產(chǎn)生的高頻噪聲,切斷其通過供電回路進(jìn)行傳播的通路;三是防止電源攜帶的噪聲對電路構(gòu)成干擾。(520101)

2021-05-25 06:14:19

差、啟動出現(xiàn)故障以及其它多種異常問題。圖1:采用去耦和不采用去耦的緩沖電路(測量結(jié)果)圖 2 闡述了為什么去耦非常重要。需要注意的是,電源線跡的電感將限制暫態(tài)電流。去耦電容與器件非常接近,因此電流路徑

2018-09-20 15:44:35

在擔(dān)任應(yīng)用工程師之前,我是 IC 測試開發(fā)工程師。我的項目之一是對 I2C 溫度傳感器進(jìn)行特性描述。在編寫一些軟件之后,我手工焊接了一個原型設(shè)計電路板。由于時間倉促,我省去了比較麻煩的去耦電容器

2018-12-26 14:19:56

旁路是把輸入信號中的干擾作為濾除對象,去耦是把輸出信號的干擾作為濾除對象。旁路電容要盡量靠近負(fù)載器件的供電電源引腳和地引腳,這樣能夠很好的防止輸入值過大而導(dǎo)致的地電位抬高和噪聲。去耦電容起到一個電池

2019-05-22 08:22:54

去耦電容的有效使用方法之一是用多個(而非1個)電容進(jìn)行去耦。使用多個電容時,使用相同容值的電容時和交織使用不同容值的電容時,效果是不同的。

2019-08-02 06:56:29

情況就是一種噪聲,會影響前級的正常工作。這就是耦合。去耦電容就是起到一個電池的作用,滿足驅(qū)動電路電流的變化,避免相互間的耦合干擾。 去耦電容布線:退耦電容主要是用來抑制IC內(nèi)部的雜訊如振蕩器的多次諧波等

2015-08-26 21:56:00

何為去耦技術(shù)?正確去耦有何必要性?去耦電容有哪些類型?不良去耦技術(shù)對性能的影響是什么

2021-03-11 08:14:14

作者: TI專家 Bruce Trump翻譯: TI信號鏈工程師 Michael Huang (黃翔) 以前談到電源去耦,我警告過糟糕的去耦會增加放大器的失真。一位讀者問了一個有趣的問題,去耦電容

2018-09-20 16:31:25

1.電源附近去耦電容的選擇很多IC管腳的VCC會增加一個0.1uf的去耦電容,因為電容的濾波曲線在谷底最低的位置濾波效果最好。當(dāng)IC內(nèi)部的邏輯門頻率是是10MHz-50MHz的時候,0.1uf電容

2021-12-31 07:29:16

用于高頻去耦,主要用于電源或電力系統(tǒng)的濾波。 由實際經(jīng)驗可知,選擇不同去耦電容的依據(jù),通常是根據(jù)時鐘或處理器的第一諧波來選擇。但是,町電流是由3次或5次諧波產(chǎn)生的,此時就應(yīng)該考慮這些諧波,采用較大

2018-11-27 15:19:23

供電電源與IC之間的去耦電容的額定電壓有什么要求啊?哪位大師幫忙指點下啊?

2013-01-25 20:04:29

在做高速電路設(shè)計的時候,為什么要有那么多去耦電容?到底什么是去耦?到底需要多大的去耦電容呢?為什么是很多個小電容并聯(lián)而不是用一個大電容(值是一樣大的啊)?為什么說小電容要靠近電源管腳而大電容可以

2019-05-07 06:22:23

去耦陶瓷電容在電源和地引腳的作用是什么?

2023-04-21 18:07:13

電源去耦電容為何要接近IC電源引腳?是什么原因呢?

2023-04-21 17:36:30

電源去耦的原因是什么實際電路常用的電源器件實際電源與理想電源的差距是什么

2021-03-17 07:22:40

2019.7.6 電源去耦設(shè)計原因:在直流電源回路中,負(fù)載的變化會引起電源噪聲。例如在數(shù)字電路中,當(dāng)電路從一個狀態(tài)轉(zhuǎn)變?yōu)榱硪环N狀態(tài)時,就會在電源線上產(chǎn)生一個很大的尖峰電流,形成瞬變的噪聲電壓。配置去

2021-12-31 08:05:14

為什么要重視電源噪聲問題?電源噪聲是如何產(chǎn)生的?電源系統(tǒng)去耦如何設(shè)計?

2021-03-11 07:01:30

電容器位置的重要性。被測電源是一個12V輸入,5V輸出,5W降壓轉(zhuǎn)換器。將輸入電壓去耦電容放置在遠(yuǎn)離MOSFET的位置(如圖2所示)而不是靠近IC(如圖3所示)會產(chǎn)生較大的環(huán)路電感。因此,開關(guān)節(jié)點振鈴

2018-09-26 10:43:37

瓷片電容、鉭電容、電解電容區(qū)別---電源設(shè)計中的去耦電容應(yīng)用實例轉(zhuǎn)自:張飛實戰(zhàn)電子電源往往是我們在電路設(shè)計過程中最容易忽略的環(huán)節(jié)。其實,作為一款優(yōu)秀的設(shè)計,電源設(shè)計應(yīng)當(dāng)是很重要的,它很大程度影響了

2021-11-11 08:12:14

什么是電源退耦?電源退耦是如何去完成的?

2021-07-19 06:28:32

4片,每一片各10個管腳,四片共40個電源管腳,單片如圖 Demo給出的去耦電容一共十幾個,貌似容值還有規(guī)律0.1u 0.1p 1p的各四組等 去耦電容如圖 我的第一個問題是去耦電容 為什么要這么選擇

2016-12-13 09:34:14

`各位大神,請問FPGA去耦電容如何布局、布線?1.根據(jù)文檔,一般去耦電容的數(shù)量都少于電源引腳,那么去耦電容要放到哪些管腳旁邊呢?2.以下三種方案哪種好?2.1電容放在PCB top層FPGA外圍

2017-08-22 14:57:10

想為cyclone V 系列的5CEFA7F27這款FPGA設(shè)計去耦電容電路,但是不知道該如何下手。參考了altera公司的一塊開發(fā)板,給出的FPGA的去耦電容電路如下所示,但是感覺這個去耦電容電路

2016-07-09 10:11:21

1.耦合機(jī)理及去耦需求集成電路芯片都有電源引腳,有的甚至有多個電源電壓和模擬數(shù)字混合電源。無論電源引腳數(shù)量如何,每路電源都有其允許范圍,包括推薦工作范圍和最大絕對值。為防止芯片損壞、保持正常工作

2021-11-17 07:42:53

的電容必須具有較低的引線和PC走線電感,因此,各電源電容必須非常靠近它去耦的IC的兩個引腳。選擇內(nèi)部電感較低的電容也很重要,通常使用陶瓷電容。許多IC中的電路會在電源端產(chǎn)生高頻噪聲,這種噪聲也必須通過跨接

2019-05-15 04:24:21

PCB PDN design guidelines (PCB電源完整性設(shè)計指導(dǎo)) ------PCB平面圖指南一、 不帶電源平面1.為每個有源設(shè)備至少提供一個“本地”去耦電容器,并為板上分布的每個

2021-12-28 06:07:45

上的傳播速度為166ps/inch,則波長為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約等于2.4厘米。 本例中的電容只能對它周圍2.4厘米范圍內(nèi)的電源噪聲進(jìn)行補(bǔ)償,即它的去耦半徑

2018-09-17 17:40:22

PCB抗干擾設(shè)計,電源線、地線、去耦電容如何配置?

2021-03-17 07:04:11

什么是PCB中的板級去耦呢?如何設(shè)計板級去耦。

2021-01-22 06:28:39

7.95ps。假設(shè)信號在電路板上的傳播速度為166ps/inch,則波長為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約等于2.4厘米。 本例中的電容只能對它周圍2.4厘米范圍內(nèi)的電源噪聲

2023-04-11 16:26:00

VCAP_1/VCAP_2外接電容是去耦電容嗎?(當(dāng)使用 2.2 uF 電源調(diào)節(jié)器打開時)

2023-02-08 07:45:17

/PCB-decoupling-capacitors-for-Virtex-6/mp/87968#M7230后,我仍有一些關(guān)于Virtex-6電源去耦的擔(dān)憂。UG373(v1.2)提到的ONLY電容是VCCINT的330μF電容

2020-06-15 16:27:01

概念層次,而旁路則只是一種途徑,一種手段,一種方法。二、如何判斷電路中的電容是去耦還是旁路?比如以下電路圖中的電容C1、C2、C3,你分得出誰是去耦電容,誰是旁路電容嗎?我們可以分別從電源模塊、IC1

2022-11-04 22:29:20

如何通過電源去耦來保持電源進(jìn)入集成電路(IC)的各點的低阻抗?諸如放大器和轉(zhuǎn)換器等模擬集成電路具有至少兩個或兩個以上電源引腳。對于單電源器件,其中一個引腳通常連接到地。如ADC和DAC等混合信號器

2018-10-31 22:37:48

如何通過電源去耦來保持電源進(jìn)入集成電路(IC)的各點的低阻抗? 諸如放大器和轉(zhuǎn)換器等模擬集成電路具有至少兩個或兩個以上電源引腳。對于單電源器件,其中一個引腳通常連接到地。如ADC和DAC等混合信號器

2022-05-11 10:26:35

如何通過電源去耦來保持電源進(jìn)入集成電路(IC)的各點的低阻抗?諸如放大器和轉(zhuǎn)換器等模擬集成電路具有至少兩個或兩個以上電源引腳。對于單電源器件,其中一個引腳通常連接到地。如ADC和DAC等混合信號器

2019-08-23 10:48:34

現(xiàn)在考察正確及錯誤去耦對14位、105/125MSPS高性能數(shù)據(jù)轉(zhuǎn)換器ADC AD9445的影響。雖然轉(zhuǎn)換器通常無PSRR規(guī)格,但正確去耦仍非常重要。圖4顯示正確設(shè)計電路的FFT輸出。這種情況下

2018-12-27 11:31:51

什么是PCB中的板級去耦呢?如何設(shè)計板級去耦?

2021-01-25 06:33:18

SOIC 的去耦局部的高頻濾波器可以優(yōu)化小小效果,去耦電容 可以減小回路電感經(jīng)驗法則–Via resistance ≈ 1mΩ, Via inductance ≈ 1nHLQFP/LFCSP 去耦

2020-10-13 09:04:13

一開始就要防止此高頻能量進(jìn)入芯片。一般通過組合電解電容(用于低頻去耦)、陶瓷 電容(用于高頻去耦)來完成,也有可能使用鐵氧體磁珠。數(shù)據(jù)轉(zhuǎn)換器以及其他模擬和混合信號電路的電源抑制可能在數(shù)據(jù)手冊中都

2018-08-22 13:56:55

TDA2030,單接每級電路都是正常工作,可是連一起就失真了,請問這是這個原因嗎?還有一個問題,去耦電容是加在每塊芯片的輸入端還是電源上啊,比如LM324,是加在3腳還是4腳啊?請原諒我的無知,謝謝!

2013-05-09 19:41:13

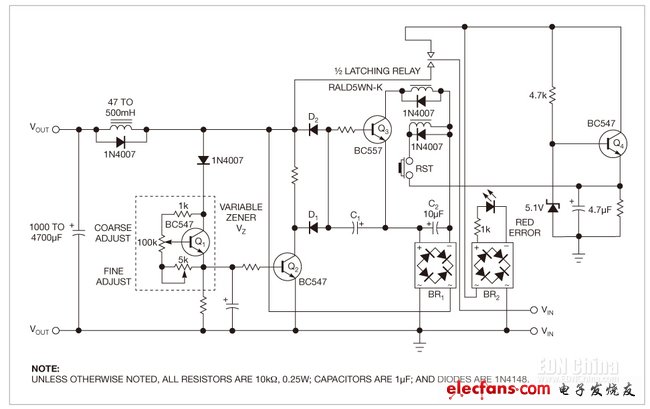

電壓是給信號光耦接通,加大占空比,使得輸出電壓升高;反之則關(guān)斷光耦減小占空比,使得輸出電壓降低。旦高頻變壓器次級負(fù)載超載或開關(guān)電路有故障,就沒有光耦電源提供,光耦就控制著開關(guān)電路不能起振,從而保護(hù)開關(guān)管

2012-12-07 13:59:26

我知道在電源設(shè)計中,電源輸入與輸出都要濾波和去耦合,請問下怎么叫去耦電容?什么叫旁路電容啊??我知道概念,它們兩者區(qū)別在于:旁路電容是把輸入信號中的干擾信號去掉,而去耦電容是把輸出信號中的干擾信號去掉;但是我不知道具體怎么區(qū)分?難道左邊的是旁路電容,右邊的是去耦電容嗎?

2024-01-08 11:30:57

單電源供電運算放大器的偏置方法偏置電路的去耦問題單電源運算放大器的偏置與去耦電路設(shè)計

2021-04-22 06:52:40

如何通過電源去耦來保持電源進(jìn)入集成電路(IC)的各點的低阻抗? 諸如放大器和轉(zhuǎn)換器等模擬集成電路具有至少兩個或兩個以上電源引腳。對于單電源器件,其中一個引腳通常連接到地。如ADC和DAC等混合

2023-04-21 17:27:59

IC還可以具有多個電源電壓,例如內(nèi)核電壓、存儲器電壓和I/O電壓。如何通過電源去耦來保持電源進(jìn)入集成電路(IC)的低阻抗?

2019-01-26 16:03:39

如何通過電源去耦來保持電源進(jìn)入集成電路(IC)的各點的低阻抗?諸如放大器和轉(zhuǎn)換器等模擬集成電路具有至少兩個或兩個以上電源引腳。對于單電源器件,其中一個引腳通常連接到地。如ADC和DAC等混合信號器

2019-06-17 15:52:31

開關(guān)IC控制器的去耦旁路設(shè)計

2021-02-19 06:17:19

本帖最后由 eehome 于 2013-1-5 09:43 編輯

濾波電容用在電源整流電路中,用來濾除交流成分。使輸出的直流更平滑。去耦電容用在放大電路中不需要交流的地方,用來消除自激,使

2012-02-10 17:10:05

數(shù)字IC電源靜噪和去耦應(yīng)用手冊數(shù)字IC電源靜噪和去耦應(yīng)用手冊,各類電容器和EMI 靜噪濾波器用于電源與數(shù)字IC 的連接。通過形成去耦電路充當(dāng)濾波器,在連接IC 電源端子和配電網(wǎng)(PDN)的連接處

2020-07-06 14:26:49

手冊中可能沒有給出實際的PSRR,數(shù)據(jù)轉(zhuǎn)換器和其他混合信號IC的性能也會隨著電源上的噪聲而降低。電源噪聲也會以多種方式影響數(shù)字電路,包括降低邏輯電平噪聲容限,由于時鐘抖動而產(chǎn)生時序錯誤。適當(dāng)?shù)木植?b class="flag-6" style="color: red">去耦

2018-10-19 10:49:11

自諧振頻率高于最高目標(biāo)頻率的電容,可確保有用值符合需要。薄膜型電容一般使用繞線,增加了電感,因此不適合電源去耦應(yīng)用。此類型更常用于音頻應(yīng)用,此時需要極低電容和電壓系數(shù)。圖3. 去耦對AD8000

2018-10-19 10:58:00

本文將討論如何通過電源去耦來保持電源進(jìn)入集成電路(IC)的各點的低阻抗。諸如放大器和轉(zhuǎn)換器等模擬集成電路具有至少兩個或兩個以上電源引腳。對于單電源器件,其中一個引腳通常連接到地。諸如ADC和DAC等

2019-02-23 06:00:00

數(shù)字IC電源靜噪與去耦應(yīng)用手冊

2012-08-18 11:18:19

數(shù)字IC電源靜噪和去耦應(yīng)用手冊

2012-08-20 14:23:53

沿著電源線傳播。去耦電容的主要功能就是提供一個局部的直流電源給有源器件,以減少開關(guān)噪聲在板上的傳播和將噪聲引導(dǎo)到地。 從電路來說,總是存在驅(qū)動的源和被驅(qū)動的負(fù)載。如果負(fù)載電容比較大,驅(qū)動電路要把電容充電

2018-12-07 09:39:59

村田-數(shù)字IC電源靜噪和去耦應(yīng)用手冊資料來自網(wǎng)絡(luò)

2019-09-10 22:40:31

去耦電容的容值計算和布局布線 有源器件在開關(guān)時產(chǎn)生的高頻開關(guān)噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個局部的直流電源給有源器件,以減少開關(guān)噪聲在板上的傳播,和將噪聲引導(dǎo)到地。

2019-07-22 07:37:46

淺談電源去耦系列第一篇,希望從定性的角度談?wù)勛约簩?b class="flag-6" style="color: red">電源去耦的理解。希望大家支持,不足之處也請各位多多指正。淺談電源去耦——電源去耦的原因理想的電源:“理想的電源”的電壓是穩(wěn)定不變的,沒有任何噪聲

2019-02-28 06:30:00

`經(jīng)常有朋友搞不清這幾種電容的作用,看到一篇不錯的文章,特意和大家分享濾波電容、去耦電容、旁路電容作用濾波電容用在電源整流電路中,用來濾除交流成分。使輸出的直流更平滑。 去耦電容用在放大電路中不需要

2013-03-08 16:33:18

我們都知道小電容濾高頻,大電容濾低頻,為了更好的濾波效果,一般輸入電源或者輸出電源都是采用一個大容值電容加一個小容值電容進(jìn)行濾波,比如1uF+0.1uF; 我們先來了解一下去耦和旁路的區(qū)別

2021-01-11 16:31:51

對于已經(jīng)知道了電容的具體特性和適用范圍,以及去耦原理,那么就知道了去耦的具體方法了嗎?不是的,下面我們將講解一下,具體安裝到電路板上之后的去耦原理以及具體如何防止電容的準(zhǔn)則!

2021-03-04 08:11:41

請問電源去耦和電源濾波是一回事嗎?

2023-04-21 17:42:23

,跟Layout攻城獅說了很多好話,他加的也很辛苦,大家都了解,可是板級電容的PDN阻抗隨頻率增加的變化趨勢就是這樣的,因為高頻段的電源去耦不歸你加的這些電容管。 結(jié)論確實很殘酷,讓你出離了憤怒,你

2020-03-18 18:35:40

什么是去耦和旁路?去耦和旁路可以防止能量從一個電路傳播到另一個電路上去,進(jìn)而提高電源分配系統(tǒng)的質(zhì)量。 回顧前面章節(jié)的介紹,可知數(shù)字邏輯電路通常涉及兩個可能的狀態(tài),“0”和“I”(參考圖3-1

2018-11-23 15:59:57

面向UUT問題域的測試需求分析方法研究 Research on Analysis Method for UUT Problem Domain一oriented Test Demand

摘要:針對當(dāng)前UUT測試需求分析過程中存在的問題,提出了面向UUT問題域的測

2009-01-10 12:43:26 10

10 IntroductionManufacturing test engineersoften face the challenge of testingmultiple UUT’s (Units

2010-07-22 14:57:43 6

6

電子發(fā)燒友App

電子發(fā)燒友App

評論