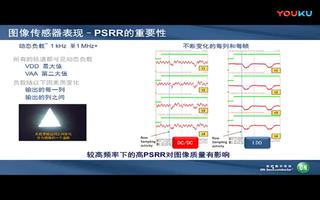

VDD網絡上的電壓下降(IR)和VSS網絡上的地線反彈會影響設計的整個時序和功能,如果忽視它們的存在,很可能導致芯片設計的失敗。電源網格中的大電流也會引起電遷移(EMI)效應,在芯片的正常壽命時間內會引起電源網格的金屬線性能劣化。這些不良效應最終將造成代價不菲的現場故障和嚴重的產品可靠性問題。

電源網格的IR壓降和地線反彈

引起VDD網絡上IR壓降的原因是,晶體管或門的工作電流從VDD I/O引腳流出后要經過電源網格的RC網絡,從而使到達器件的VDD電壓有所下降。地線反彈現象與此類似,電流流回VSS引腳時也要經過RC網絡,從而導致到達器件的VSS電壓有所上升。更加精細的設計工藝和下一代設計技術使新的設計在IR壓降或地線反彈方面要承受更大的風險。電源網格上的IR壓降主要影響時序,它會降低門的驅動能力,增加整個路徑的時延。一般情況下,供電電壓下降5%會使時延增加15%以上。時鐘緩沖器的時延會由于IR壓降增加1倍以上。當時鐘偏移范圍在100ps內時,這樣的時延增幅將是非常危險的。可以想象一下集中配置的關鍵路徑上發生這種未期而至的延時會出現什么樣的情景,顯然,設計的性能或功能將變得不可預測。理想情況下,要想提高設計精度,其時序計算必須考慮最壞情況下的IR壓降。

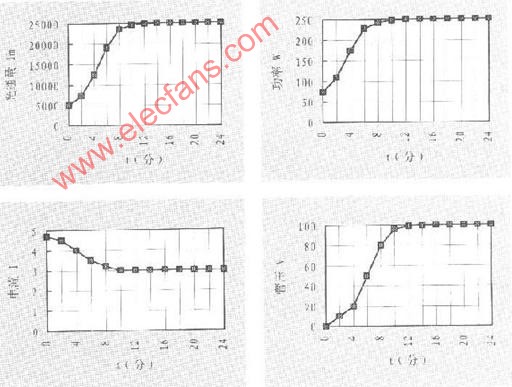

電源網格分析方法主要有靜態和動態兩種方法。

靜態電源網格分析

靜態電源網格分析法無需額外的電路仿真即能提供全面的覆蓋。大多數靜態分析法都基于以下一些基本概念:

1.提取電源網格的寄生電阻;

2.建立電源網格的電阻矩陣;

3.計算與電源網格相連的每個電阻或門的平均電流;

4.根據晶體管或門的物理位置,將平均電流分配到電阻矩陣中;

5.在每個VDD I/O引腳上將VDD源應用到矩陣;

6.利用靜態矩陣解決方案計算流經電阻矩陣的電流和IR壓降。

由于靜態分析法假設VDD和VSS之間的去耦電容足夠濾除IR壓降或地線反彈的動態峰值,因此其結果非常接近電源網格上動態轉換的效果。

靜態分析法的主要價值體現在簡單和全面覆蓋。由于只需要電源網格的寄生電阻,因此提取的工作量非常小。而且每個晶體管或門都提供對電源網格的平均負載,因此該方法能夠全面覆蓋電源網格,但它的主要挑戰在于精度。靜態分析法沒有考慮本地動態效應和封裝傳導效應(Ldi/dt),如果電源網格上沒有足夠的去耦電容,那么這二者都會導致進一步的IR壓降和地線反彈。

動態電源網格分析

動態電源網格分析法不僅要求提取電源網格的寄生電阻,還要求提取寄生電容,并要完成電阻RC矩陣的動態電路仿真。動態電源網格分析法的典型步驟是:

1.提取電源網格的寄生電阻和電容;

2.提取信號網絡的寄生電阻和電容;

3.提取設計網表;

4.根據提取的寄生電阻、電容值和網表生成電路網表;

5.依據仿真向量集執行電路仿真,主要仿真晶體管或門的動態轉換以及該轉換對電源網格的影響。

動態分析法的主要價值體現在它的精度。由于分析的依據是電路仿真,IR壓降和地線反彈結果將是非常精確的,并考慮了本地動態效應和封裝傳導效應。

但動態分析法面臨的挑戰也是十分艱巨的,原因在于:

1. 寄生提取要求非常高,因為需要提取電源網格的電阻和電容以及(至少)信號網絡的電容。

2. 電路仿真的對象非常多,會使電路仿真引擎滿負荷工作。

3. 用作激勵信號的向量集在決定輸出質量時起著重要的作用。如果沒有采用完整的測試向量集,那么結果將是令人懷疑的,因為電源網格的某些部分可能沒有被仿真到。

4. 最后,由于單個電源網格就有如此多的考慮因素,基于全面動態仿真的電源網格分析法將難以適應設計規模的進一步增加。

許多追求動態效應的電源網格分析法必須求助于RC壓縮技術才能管理大量的仿真數據,然而這樣做與動態分析法的主要價值-高精度是互相矛盾的。電源網格的RC壓縮化會導致分析結果的精度下降,甚至會掩蓋真正的EMI問題。

電遷移和全芯片EMI分析

電源網格的電遷移是由流經金屬線與通孔的平均電流引起的一種直流現象。這是深亞微米電源網格設計中出現的另外一種重要問題。大電流密度與窄線寬會引起EMI,而由EMI造成的故障可能是災難性的。這些故障一般都發生在用戶那兒,此時芯片早已安裝在系統中的基板上了,如果真的出問題,就可能會導致設計被召回。

雖然EMI可能會造成電源網格中的電路開路或短路,但最常見的影響還是電源網格路徑中電阻值的增加,由此引起IR壓降或地線反彈,從而影響到芯片的時序。這也是一個設計為什么最初工作正常且符合規范,但后來發生故障的原因所在。EMI設計的指導性依據是平均電流水平,其實最終還是取決于信號線電容。

因此精確的EMI預測需要正確的電容信息。此外,由于設計中的金屬線會有高度變化,金屬有不同級別的材料屬性,因此每個金屬層都會有不同的故障標準,所以確定整個芯片上有潛在EMI問題的所有區域的唯一方法是進行全芯片分析。

業界常用Black定律預測金屬線的平均無故障時間,主要參數是金屬線旁邊所示的平均電流密度J。平均數據越精確,MTTF的估測效果就越好。為了得到最精確的數據信息,往往需要在設計中使用大量的向量。同時必須測得每根金屬線的平均電流,然后除以線的寬度和厚度。這對構造芯片來說顯然是不可能做到的,也無法用電路仿真實現。

替代昂貴的晶體管級仿真的另外一種方法是利用門級或更高層工具從活動信息中獲取以觸發數據形式出現的平均電流。觸發數據其實只是一個門在上千個時鐘的仿真周期內完成高低電平切換的次數。將這些觸發數據除以時鐘周期數就可以得到活動信息。例如,一個存儲器電路的內核的活動性可能是0.02%,而一個數據路徑可能接近5%。對與電源網格相連的晶體管來說,這些因子可以轉換成平均電流信息。

當然,設計師必須判斷整個電源網格上流動的平均電流,以便評估給定設計的可靠性風險。只是判斷被隔離了的模塊平均行為是不夠的,因為模塊在全芯片流程中可能只是周期性的工作。此外,即使對電源網格中的一部分作改動也會對全局有影響。數據壓縮也是不能使用的,因為數據壓縮本身可能會掩蓋某些真正的EMI問題。因此除非整個芯片作為一個實體得到了全面的驗證,否則仍然存在EMI預測精度不足的風險。任何用作該用途的工具必須具備分析百萬個電阻網絡的能力。

電源網格分析現已成為出帶之前一個關鍵的設計驗證部分。由于IR壓降、地線反彈和EMI的存在,IC電源分配系統的設計變得異常復雜。在較早以前,對電源網格進行DRC、LVS和手工計算即可確保得到一個完美的電源網格設計,花較多的精力設計電源網格在當時被認為是一種可以接受的解決方案。而在當今激烈競爭的市場上,過多地考慮電源網格會導致良品率下降,設計缺乏競爭性,而考慮欠妥也會導致出帶失敗、流片反復和代價高昂的現場故障-終究無法兩全其美。

電子發燒友App

電子發燒友App

評論