在做硬件系統(tǒng)設計時,需要選擇正確的電源供電芯片,無論是設計消費數碼電子還是無線傳感設備,需要權衡好產品的各個功能需求。在對噪聲抑制、耗電量、壓降、和電源電壓電流等指標做出評估和劃定優(yōu)先級后,才可以進行電源IC的選擇。

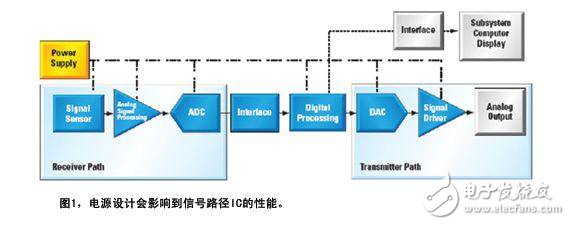

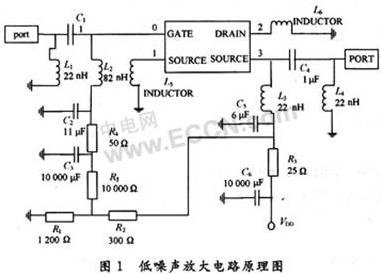

每個信號路徑需要“干凈”的電源。電源管理是系統(tǒng)設計的最后部分。圖1顯示了如何為信號路徑供電的實例系統(tǒng)。

設計一個需要超低功耗的無線產品,一個3AH的電池要能工作5-6年,這個需要整個通信機制需要有省電的功能,也需要產品本身需要有超低功耗的能力,一個無線產品需要具有超低功耗需要從產品的幾個構成部分來分析:

1)電源部分

2)RF部分

3)CPU部分

4)其他部分

這里結合我的工作做對電源部分的分析:

選擇電源芯片原則:

1)選擇工藝成熟,產品質量好,性價比好的廠家產品。

2)選擇工作頻率高的產品,降低周圍器件,降低成本。

3)用封裝小的,但要考慮輸出電流的大小,一般都是小封裝小電流,大封裝大電流

4)選擇技術支持好的廠家,特別是小公司選擇電源器件時要注意,小公司別人不理睬你

5)選擇資料齊全的,最好有中文的,樣品可以申請的,最好有免費的,供貨周期短的,最好不 要老停產

以上是從大的層面來做分析,包括設計和采購等方面來考慮。

從技術要求的層面來分析:

LDO 器件選擇

LDO選擇4個要素:壓差、噪聲、靜態(tài)電流、共模抑制比。

僅僅從省電來說,主要看靜態(tài)電流,有的LDO靜態(tài)電流很小,1UA左右,就是LDO工作時,自身的耗電,這個參數在省電中很關鍵,越小肯定越好,但不可能為0,LDO的耗電有兩個指標:一個為靜態(tài)電流,一個為SET_OFF電流,要區(qū)分哦!!還有壓差,這個好理解,壓差為0就是很理想的LDO。

我現在用的是S-1206系列,日本的,用日貨,沒有辦法,SOT23,路過的朋友介紹一個國貨給我,質量要好的,還有R1180X系列,好像也是日本的。以上都是5ua以下的IQ值。

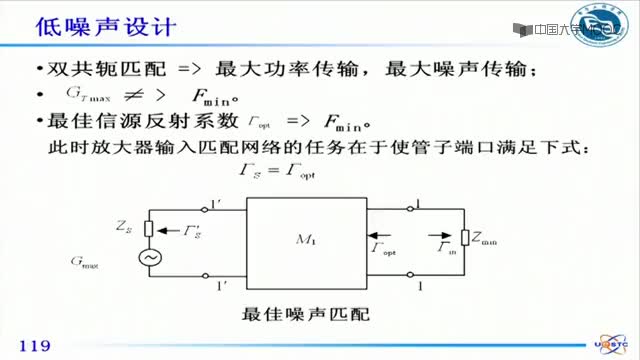

但是做RF的LDO,就需要考慮:噪聲抑制了,因為RF這玩意對噪聲的敏感度太高了。

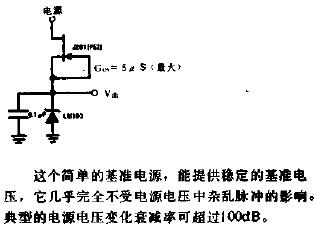

電源抑制比PSRR (Power supply ripple rejection ratio))是反映輸出和輸入頻率相同的條件下,LDO輸出對輸入紋波抑制能力的交流參數。和噪聲(Noise)不同,噪聲通常是指在10Hz至 100kHz頻率范圍內,LDO在一定輸入電壓下其輸出電壓噪聲的均方值(RMS),PSRR的單位是dB,公式如下:PSRR=20 log(△vin/△vout)

電源影響信號路徑性能

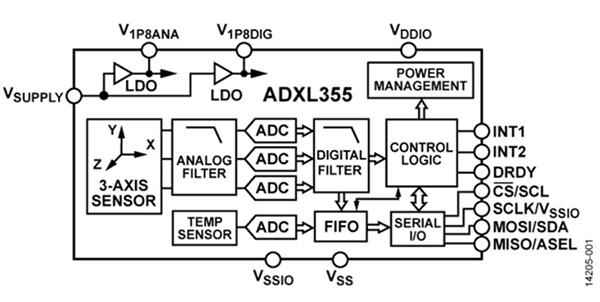

圖2,電源抑制比(PSRR)是對從輸入到輸出紋波/噪聲的衰減度量

?

并不意外的是,電源影響模擬信號完整性,這最終會影響整體的系統(tǒng)性能。提高信號路徑性能的一種簡單方法是選擇正確的電源。在選擇電源時,影響模擬信號路徑性能的一個關鍵參數是電源線上的噪聲或紋波。電源線上的噪聲或紋波可以耦合到運算放大器的輸出中,增加鎖相環(huán) (PLL)或壓控振蕩器(VCO)的抖動,或者降低ADC的SNR。低噪聲和低紋波的電源還能改善信號路徑性能。

電源線上的噪聲或紋波的來源具有多樣性。在系統(tǒng)內的高速數據和高頻信號本身會產生噪聲,PCB的印制線和連接線如果設計不當,可以形成發(fā)射天線的效應。數字IC,例如微控制器和現場可編程門陣列(FPGA)以及復雜可編程邏輯器件(CPLD)具有很快的邊沿跳變速度,電流的大小變化很大,將產生電磁干擾輻射到系統(tǒng)中。IC硅片在內部產生熱噪聲,這是由于在溫度高于絕對0攝氏度時分子的隨機運動和碰撞產生的。

有三種常用的方法來使信號路徑中的噪聲和紋波最小:非常仔細的系統(tǒng)PCB布局、恰當的電源旁路處理以及正確的電源選擇。盡管PCB的具體設計取決于系統(tǒng),但就一般而言,PCB的布局需要考慮包括正確的器件布局、使信號路徑連接線的長度最小以及采用實體的地等。

對電源軌進行旁路處理是一種常用的方法,這種方法通常在模擬IC產品手冊中被推薦用于濾出噪聲。信號路徑IC可以具有分離的模擬、數字和PLL電源輸入,建議每個采用自己獨立的旁路處理。PLL電源和模擬電源對噪聲和紋波最敏感。旁路電容、阻容(RC)濾波器以及EMI抑制濾波器使進入信號路徑的電源噪聲最小化。

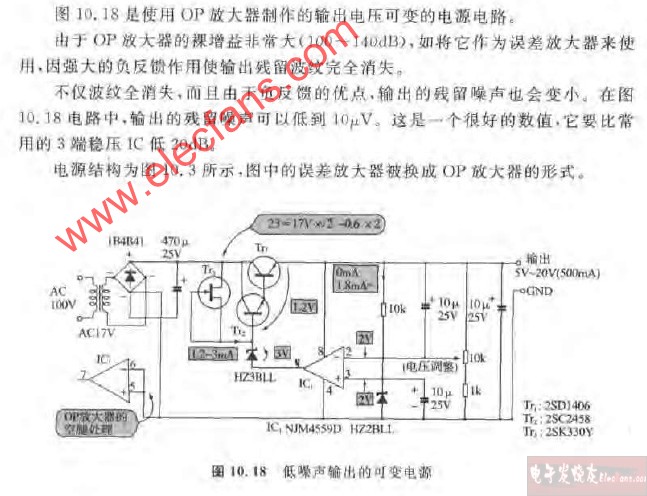

正確的電源選擇可以降低對信號路徑IC的噪聲和紋波影響。在選擇一種電源時,設計師首先在開關變換器和線性穩(wěn)壓器之間作一個基本選擇。開關轉換器提供較高的頻率,更高的頻率意味著較低的整體系統(tǒng)功耗。線性穩(wěn)壓器提供一種易于使用的解決方案,同時降低電源軌的噪聲/紋波。使用線性穩(wěn)壓器降低噪聲和紋波可以改善信號路徑性能。

毫無疑問,在便攜式無線產品里,即需要自身工作耗電電流小的,又需要PSRR大的LDO,但是目前市面上的LDO產品,能兼顧到這兩個指標的產品很少,本人找到一個S1167的LDO,工作自身耗電為9UA,PSRR為70dB,應該說是比較兼顧這兩個指標的,但是是日本貨。

單單是考慮到PSRR,而IQ在45左右都無所謂的話,用AS1361是不錯的,PSRR可到90dB以上。

DC-DC電源選擇

對于DC-DC來說,主要考慮轉換的效率,紋波,輸入輸出電壓等。

在選擇DC/DC變換器時,電路設計要注意輸出電流、高效率、小型化,輸出電壓要求:

1. 如需求的輸出電流較小,可選擇FET內置型;輸出電流需要較大時,選擇外接FET類型。

2. 關于效率有以下考慮:如果需優(yōu)先考慮重負荷時的紋波電壓及消除噪音,可選擇PWM控制型;如果同時亦需重視低負荷時的效率,則可選擇PFM/PWM切換控制型。

3. 如要求小型化,則可選擇能使用小型線圈的高頻產品。

4. 在輸出電壓方面,如果輸出電壓需要達到固定電壓以上,或需要不固定的輸出電壓時,剛可選擇輸出可變的VDD/VOUT分離型產品。

DC-DC工作方式PFM與PWM比較:

PWM控制、PFM控制和PWM/PFM切換控制模式這三種控制方式各有各的優(yōu)點與缺點: DC/DC變換器是通過與內部頻率同步開關進行升壓或降壓,通過變化開關次數進行控制,從而得到與設定電壓相同的輸出電壓。

PFM控制時,當輸出電壓達到在設定電壓以上時即會停止開關,在下降到設定電壓前,DC/DC變換器不會進行任何操作。但如果輸出電壓下降到設定電壓以下,DC/DC變換器會再次開始開關,使輸出電壓達到設定電壓。PWM控制也是與頻率同步進行開關,但是它會在達到升壓設定值時,盡量減少流入線圈的電流,調整升壓使其與設定電壓保持一致。

與PWM相比,PFM的輸出電流小,但是因PFM控制的DC/DC變換器在達到設定電壓以上時就會停止動作,所以消耗的電流就會變得很小。因此,消耗電流的減少可改進低負荷時的效率。PWM在低負荷時雖然效率較遜色,但是因其紋波電壓小,且開關頻率固定,所以噪聲濾波器設計比較容易,消除噪聲也較簡單。

若需同時具備PFM與PWM的優(yōu)點的話,可選擇PWM/PFM切換控制式DC/DC變換器。此功能是在重負荷時由PWM控制,低負荷時自動切換到 PFM控制,即在一款產品中同時具備PWM的優(yōu)點與PFM的優(yōu)點。在備有待機模式的系統(tǒng)中,采用PFM/PWM切換控制的產品能得到較高效率。

高頻的優(yōu)點 :

通過實際測試PWM與PFM/PWM的效率,可以發(fā)現PWM/PFM切換的產品在低負荷時的效率較高。至于高頻方面,通過提高DC/DC變換器的頻率,可以實現大電流化、小型化和高效率化。但是,必須注意的是只有通過線圈的特性配合才可以提高效率。因為當DC/DC變換器高頻化后,由于開關次數隨之增加的原因,開關損失也會增大,從而導致效率會有所降低。因此,效率是由線圈性能提升與開關損失增加兩方面折衷決定的。通過使用高效率的產品,相對可使用較低電感值的線圈,可以使用小型線圈,即使使用的是小型線圈也可得到相同的效率及輸出電流。

外接器件選擇:

除了需要關注DC/DC變換器本身的特性外,外接組件的選擇也不能忽視。外接組件中的線圈、電容器和FET對于開關電源特性有著很大影響。這里所謂的特性是指輸出電流、輸出紋波電壓及效率。

線圈:如果需要追求高效率,最好選擇直流電阻和電感值較小的線圈。但是,如果電感值較小的線圈用于頻率較低的DC/DC,就會超過線圈的額定電流,線圈會產生磁飽和現象,引起效率惡化或損壞線圈。而且如果電感值太小,也會引起紋波電壓變大。所以在選擇線圈時,請注意流向線圈的電流不要超過線圈的額定電流。在選擇線圈時,需要根據輸出電流、DC/DC的頻率、線圈的電感值、線圈的額定電流和紋波電壓等條件綜合決定。

電容:輸出電容的容量越大,紋波電壓就越小。但是較大的容量也意味著較大的電容體積,所以請選擇最適合的容量。

三極管:作為外接的三極管,與雙極晶體管相比,因FET的開關速度比較快,所以開關損耗會較小,效率會更高一些。

電子發(fā)燒友App

電子發(fā)燒友App

評論