DC/DC轉換器的設計頻率越來越快,目的是減小輸出電容和電感的尺寸,以節省電路板空間。正因如此,現在市場上出現越來越多工作在高輸入電壓下的DC/DC轉換器,其可提供線壓瞬態保護

2012-05-09 09:40:15 1402

1402 DCM ChiP(Converter housed in Package)是一款可從未穩壓的寬范圍輸入生成隔離穩壓 DC 輸出的DC-DC 轉換器模塊。DCM 轉換器采用高頻率零電壓開關 (ZVS) 拓撲,可在整個輸入電壓范圍內始終如一地提供高效率。

2018-07-10 14:54:17 6339

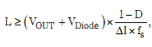

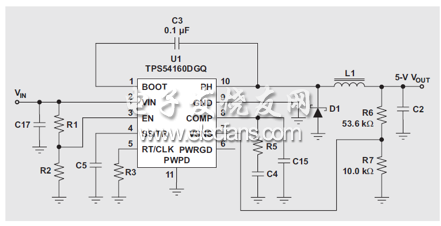

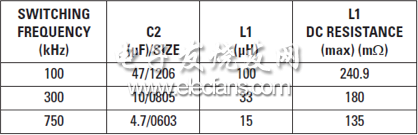

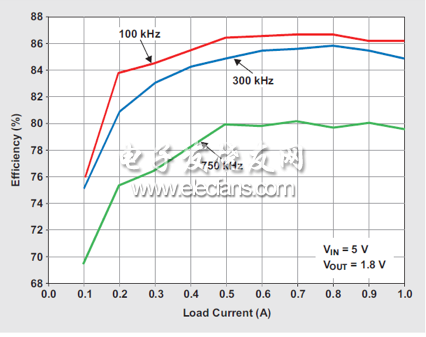

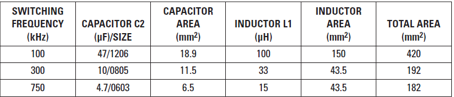

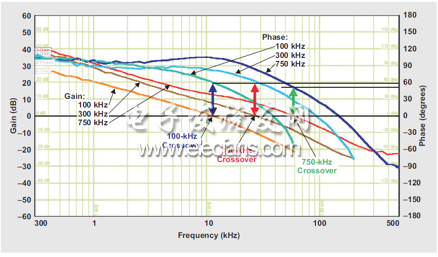

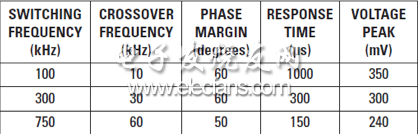

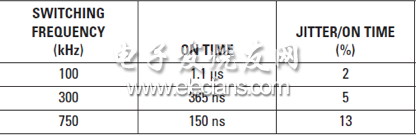

6339 為了解釋這些權衡,德州儀器工程師建造了三個獨立的電源,每個電源的開關頻率分別為100,300和750 kHz。如應用筆記“設計高頻,高輸入電壓DC/DC轉換器的挑戰”所述,1所有三個DC/DC轉換器

2019-01-28 08:59:00 3835

3835

高開關頻率通常可以提高DC-DC轉換器的效率。這是因為高頻率開關可以減小開關器件的尺寸,降低開關過程中的能量損耗,從而提高整體轉換效率。

2024-03-11 15:46:01 576

576

PAM2310 2A低噪聲降壓DC-DC轉換器的典型應用。 PAM2310是一款2A降壓DC-DC轉換器。在高負載時,恒定頻率PWM控制可實現出色的穩定性和瞬態響應。無需外部補償組件

2019-03-07 09:51:34

PAM2320 3A低噪聲降壓DC-DC轉換器的典型應用。 PAM2320是3A降壓DC-DC轉換器。在高負載時,恒定頻率PWM控制可實現出色的穩定性和瞬態響應。無需外部補償組件

2019-03-07 06:13:36

DC-DC 轉換器 控制環路如何使用模擬或數字技術實現?如何使用典型的波特圖來顯示隨頻率變化的相移和環路增益?

2021-03-11 07:34:21

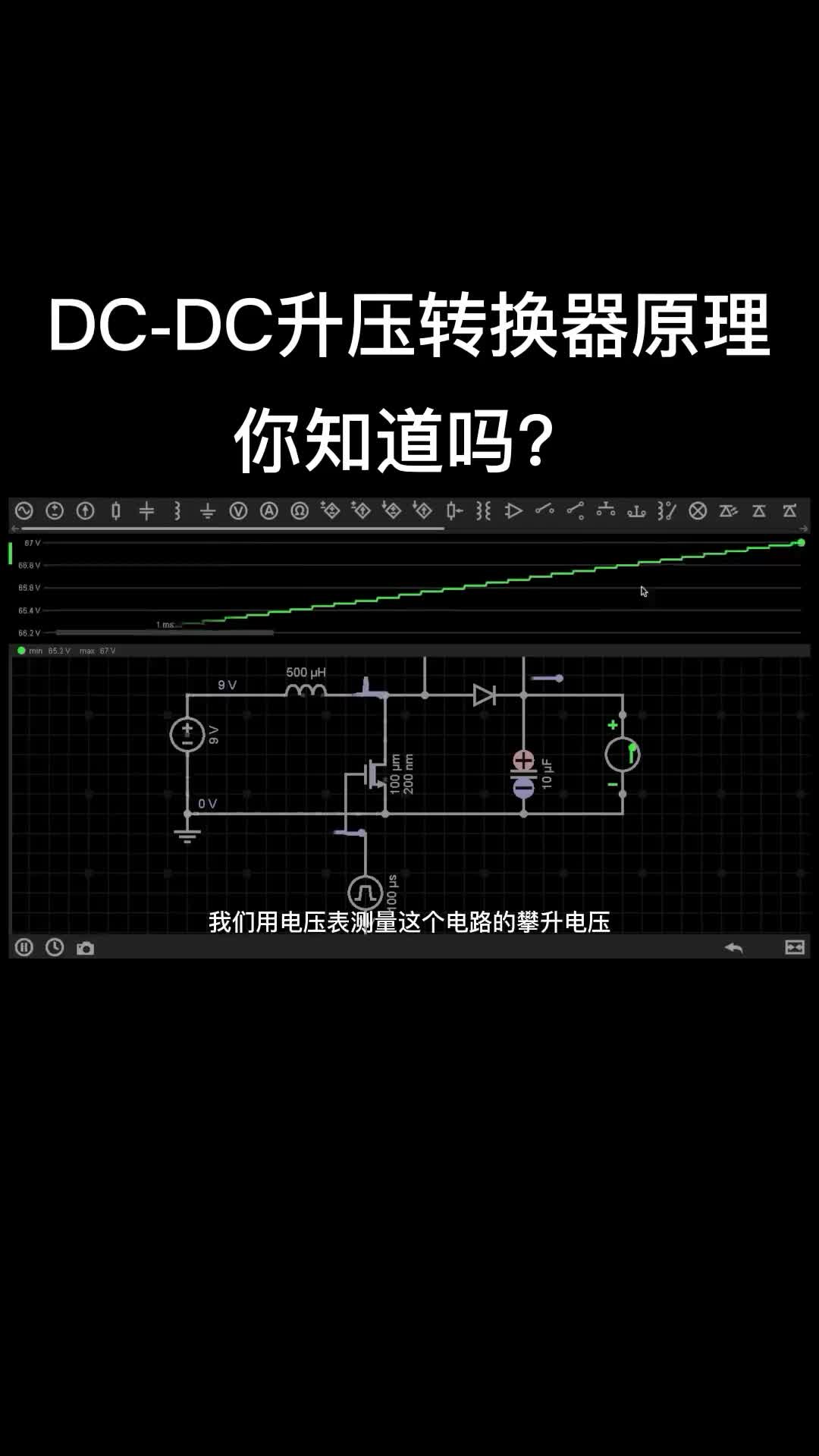

DC-DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換器。DC/DC轉換器分為三類:升壓型DC/DC轉換器、降壓型DC/DC轉換器以及升降壓型DC/DC轉換器。根據需求

2010-04-19 11:43:53

DC-DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換器。DC/DC轉換器分為三類:升壓型DC/DC轉換器、降壓型DC/DC轉換器以及升降壓型DC/DC轉換器。根據需求

2010-03-09 14:20:40

* DC-DC轉換器包括升壓、降壓、升/降壓和反相等電路。DC-DC轉換器的優點是效率高、可以輸出大電流、靜態電流小。隨著集成度的提高,許多新型DC-DC轉換器僅需要幾只外接電感器和濾波電容器。但是

2021-10-28 06:41:15

最近有網友問:什么是DC-DC轉換器?DC-DC轉換器是如何命名的?泰德蘭電子小編在這里和大家分享一下關于什么是DC-DC轉換器,首先我們先簡單了解下DC-DC轉換器,本文也將在下方附上一張關于

2021-11-17 06:24:47

DC-DC轉換器是什么及其參數DC/DC 轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換器。DC/DC 轉換器分為三類:升壓型DC/DC 轉換器、降壓型DC/DC 轉換器以及升降壓型DC/DC

2009-11-14 11:11:14

由字面意思可以得到直流轉直流,可以直接按照下圖的線性電源模型進行轉換:缺點:只能由高電壓轉換到低電壓;由于存在上面的1Ω的電阻,效率低,所以人們制造了非線性的電源模型:直流—>交流—>直流,且可以有效的克服上述的缺點。這就是DC-DC轉換器的模型。...

2021-11-17 08:18:03

順源新研制的GRE/GRF系列低成本小體積、寬電壓輸入隔離穩壓回路輸出高壓模塊電源,是一款業界技術領先的DC-DC高電壓轉換器。該產品可在寬范圍波動的不穩定電源電壓輸入環境中安全運行,通過模塊的內部

2021-12-29 07:38:00

什么是DC-DC轉換器?線性及開關式穩壓器的性能有什么區別呢?

2021-11-04 08:01:50

DN234低成本多相? DC / DC轉換器提供高電流

2019-06-26 07:29:20

DC/DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換器。DC/DC轉換器分為三類:升壓型DC/DC轉換器、降壓型DC/DC轉換器以及升降壓型DC/DC轉換器。根據需求可采用三類控制。PWM控制

2021-11-16 07:05:30

高頻率、高輸入電壓DC/DC轉換器設計挑戰

2021-04-06 08:57:04

“DC/DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換器。在IoT硬件設計中應用的也比較廣泛”01—電荷泵式DC/DC在IoT硬件設計中有兩類DC/DC應用比較廣泛,一種是電荷泵,...

2021-11-16 06:43:07

本詞條缺少概述圖,補充相關內容使詞條更完整,還能快速升級,趕緊來編輯吧!DC/DC轉換器是開關電源芯片,指利用電容、電感的儲能的特性,通過可控開關(MOSFET等)進行高頻開關的動作,將輸入的電能

2021-11-16 08:28:48

一、正確理解DC/DC轉換器 DC/DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換 器。DC/DC轉換器分為三類:升壓型DC/DC轉換器、降壓型DC/DC轉換器以及升降壓型DC/DC轉換器

2018-09-29 15:30:43

一、正確理解DC/DC轉換器

DC/DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換 器。DC/DC轉換器分為三類:升壓型DC/DC轉換器、降壓型DC/DC轉換器以及升降壓型DC/DC轉換器

2023-12-19 07:09:16

密歇根州南菲爾德--(美國商業資訊)--動力管理公司伊頓(Eaton)今天宣布,其eMobility事業部已獲得一份合同,將為商用重型電池電動車(BEV)提供24至12伏的DC/DC轉換器,此類

2021-11-17 08:05:50

演示電路DC1619A是一款100kHz至500kHz可編程頻率,高電壓,電流模式DC / DC降壓轉換器,采用LT3845A。工作頻率可以同步到600kHz。該演示板設計用于從16V至60V輸入的12V至10A(120W)輸出

2019-07-11 14:10:32

時的 SNR 性能比較。各奈奎斯特區使用數據手冊推薦的設置。圖3:圖1和圖2所示PDN的性能比較僅使用 DC-DC 轉換器為 GSPS ADC 的 1.25 V 域供電的 PDN 在各種輸入頻率下顯示出了良好

2018-05-28 10:31:11

的性能比較僅使用 DC-DC 轉換器為 GSPS ADC 的 1.25 V 域供電的 PDN 在各種輸入頻率下顯示出了良好的性能。這證明了可以組合域,并在不損失大量 ADC 性能的情況下以高效率

2018-10-29 16:53:14

轉換器.具體是指通過自激振蕩電路把輸入的直流電轉變為交流電,再通過變壓器改變電壓之后再轉換為直流電輸出,或者通過倍壓整流電路將交流電轉換為高壓直流電輸出。dc/dc轉換器是一種新研制的小型化電源開關模塊

2018-07-28 14:21:01

DN218- 高電流雙路DC / DC轉換器,工作電壓為3.3V

2019-06-26 08:09:41

的尺寸,以節省電路板空間。正因如此,現在市場上出現越來越多工作在高輸入電壓下的DC/DC轉換器,其可提供線壓瞬態保護,更低的占空比使更快頻率下難以達到更低的電壓。許多電源集成電路制造廠商(IC)正在

2011-10-14 12:49:33

轉換器時存在折衷。本文探討了一些設計實例,這些實例證明了在較高頻率下切換高輸入電壓降壓DC/DC轉換器的好處和缺陷。為了解釋這些權衡,德州儀器工程師建造了三個獨立的電源,每個電源的開關頻率分別為

2019-07-16 23:54:06

高頻率升壓轉換器TPS61040資料下載內容包括:TPS61040引腳功能TPS61040內部方框圖TPS61040典型應用電路

2021-03-29 07:49:45

,因此脈沖寬度無法保持恒定。總而言的,AC/DC轉換是直接將輸入的AC電壓整流-平滑后,轉換成DC,再將該DC轉換成高頻率的AC,接著重復整流-平滑步驟,轉換成想要的DC電壓。和前述的變壓器方式相比

2018-11-28 14:26:27

ROHM開發出以2MHz開關頻率實現業界最高降壓比的DC/DC轉換器IC“BD9V100MUF-C”,并已于2017年6月開始出售樣品,于2017年12月投入量產。從2016年的CEATEC起

2019-04-04 06:20:41

請問,CC1310片內DC-DC轉換器輸出的電壓電流參數在哪可以查到,片內DC/DC轉換器可以關閉嗎?芯片進入休眠或SHUTDOWN后,DCDC_SW的輸出是什么狀況?

2016-12-08 12:17:12

使用 DC-DC 轉換器為 GSPS ADC 的 1.25 V 域供電的 PDN 在各種輸入頻率下顯示出了良好的性能。這證明了可以組合域,并在不損失大量 ADC 性能的情況下以高效率、高性價比的方式為它們供電

2018-10-30 11:52:25

高電壓LTC3892系列控制器縮減了 DC/DC 轉換器成本和尺寸

2021-02-03 06:46:11

NCP3063 1.5A升壓型開關穩壓器的典型升壓應用原理圖。 NCP3063系列是對流行的MC34063A和MC33063A單片DC-DC轉換器的更高頻率升級。這些器件由內部溫度補償基準電壓源,比較器,帶有源電流限制電路的受控占空比振蕩器,驅動器和高電流輸出開關組成。

2019-09-27 06:50:04

NCV3063 1.5A降壓開關穩壓器的典型降壓應用原理圖。 NCP3063系列是對流行的MC34063A和MC33063A單片DC-DC轉換器的更高頻率升級。這些器件由內部溫度補償基準電壓源,比較器,帶有源電流限制電路的受控占空比振蕩器,驅動器和高電流輸出開關組成。

2019-09-25 08:40:48

具有RC緩沖器和脈沖反饋的降壓轉換器的典型原理圖NCV3063 1.5A降壓開關穩壓器。 NCP3063系列是對流行的MC34063A和MC33063A單片DC-DC轉換器的更高頻率升級。這些器件由內部溫度補償基準電壓源,比較器,帶有源電流限制電路的受控占空比振蕩器,驅動器和高電流輸出開關組成。

2019-09-25 06:08:09

具有外部低VCE(sat)PNP晶體管的典型降壓應用原理圖,用于NCV3063 1.5A降壓開關穩壓器。 NCP3063系列是對流行的MC34063A和MC33063A單片DC-DC轉換器的更高頻率

2019-09-26 08:33:48

采用外部NMOS晶體管的典型升壓應用原理圖,適用于NCV3063 1.5A升壓型開關穩壓器。 NCP3063系列是對流行的MC34063A和MC33063A單片DC-DC轉換器的更高頻率升級。這些

2019-09-25 08:21:31

具有ON / OFF功能的NCP3064B 1.5A升壓型開關穩壓器的典型升壓應用。 NCP3064系列是對流行的MC33063A和MC34063A單片DC-DC轉換器的更高頻率升級。這些器件由內部溫度補償基準電壓源,比較器,帶有源電流限制電路的受控占空比振蕩器,驅動器和高電流輸出開關組成

2019-09-26 08:33:18

PAM2305D 1A降壓型DC-DC轉換器的典型應用。 PAM2305D是一款降壓型電流模式DC-DC轉換器。在高負載時,恒定頻率PWM控制可形成出色的穩定性和瞬態響應

2019-03-15 10:35:10

PW2051是一顆DC-DC同步降壓轉換器芯片,輸入電壓范圍2.5V-5.5V,,最大負載電流1.5A,可調輸出電壓,頻率1.5MHZ高頻率,可采用貼片電感,節省空間,采用SOT23-5封裝形式

2021-11-16 09:35:57

` 本帖最后由 OneyacSimon 于 2019-6-24 16:39 編輯

Torex XCL微型DC / DC轉換器將電感器和控制IC組合在一個超小型封裝中。XCL微型DC / DC

2019-06-24 16:37:21

半磚大小150 W DC—DC轉換器,提供超寬8∶1輸入范圍

2020-12-03 07:49:21

Vicor DCM3623是一種隔離穩壓DC-DC轉換器,可從寬泛的未穩壓輸入生成隔離式穩壓輸出。憑借其高頻零電壓開關 (ZVS) 拓撲結構,DCM3623轉換器可在整個輸入電壓范圍內始終提供高效率

2018-08-06 10:33:03

很多硬件設計者,都沒有正確的理解和使用DC/DC轉換器,下面小編整理了一些特別有用的文章作為福利送給大家!一、正確理解DC/DC轉換器DC/DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換器

2022-05-27 10:50:28

功率電感器的嘯叫現象是什么?為什么DC-DC轉換器的功率電感器會發出“嘰”的嘯叫呢?如何去解決呢?

2021-07-12 06:33:09

什么是DC-DC轉換器?線性及開關式穩壓器性能有什么區別?快跟隨英飛凌工程師一起來了解吧~本文作者 英飛凌汽車電子工程師 顏榮宏DC-DC直流電源轉換器從字面上來看便可大致得知其主要作用是要作為

2021-07-30 06:00:49

什么是DC/DC轉換器?本資料為DC/DC轉換器電路的設計提供一些提示,盡量用具體事例說明在各種制約條件下,怎樣才能設計出最接近要求規格的DC/DC轉換器電路。DC/DC轉換器電路的各種特性(效率

2021-10-28 09:08:03

摘要 本文介紹了碳化硅(SiC)器件在高頻率 LLC 諧振 DC/DC 轉換器中的應用。此類轉換器可用于母線轉換器、電動汽車充電機、服務器電源和儲能系統。在開關頻率較高的情況下,LLC 變壓器

2023-02-27 14:02:43

由于其高功率效率而成為大多數(如果不是全部)供電方案的一部分。DC / DC轉換器的效率可以達到90%左右,為需要提供電源的解決方案提供最節能的解決方案。DC-DC轉換器的內部功耗有兩個主要組成部分

2018-07-24 17:34:16

使用DC/DC轉換器的主要目的是將負載電壓和電源電壓相匹配(例如從24V供電給3.3V微處理器板)、輸出與輸入端之間相互隔離(例如一個電氣隔離的轉換器可以保護患者免受危險電壓的傷害),同時增加故障

2021-11-16 08:39:57

DC751A-G,演示板使用LTC2232IUK 10位,105 Msps,高速,高動態范圍模數轉換器。根據所需的分辨率,采樣率和輸入頻率,DC751提供相應的A / D和優化的輸入電路。模擬輸入上的電路針對低于100 MHz或100 MHz至250 MHz的模擬輸入頻率進行了優化。用于更高的工作頻率

2019-05-10 09:38:47

來源 網絡一、正確理解DC/DC轉換器DC/DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換 器。DC/DC轉換器分為三類:升壓型DC/DC轉換器、降壓型DC/DC轉換器以及升降壓型DC/DC

2018-03-27 17:17:04

請問dc to dc 轉換器,用micro controller 控制, 用什么軟件可以做仿真實驗呢?謝謝

2014-01-15 00:38:16

LTC3526LEDC-2 1節至3.3V升壓轉換器的典型應用電路。 LTC3526是一款具有輸出斷接功能的同步固定頻率升壓型DC / DC轉換器。同步整流可在低剖面2mm + 2mm DFN封裝中實現高效率

2020-07-16 09:51:37

轉換器產品陣容中也是最高耐壓的機型。高耐壓的DC/DC轉換器在以電信相關和工業設備為首的應用中、最近在使用電池組的應用中使用量增加,因此其需求日益高漲。然而,現狀是可供應具有60V以上耐壓的DC/DC

2018-10-19 16:47:06

產品陣容中也是最高耐壓的機型。高耐壓的DC/DC轉換器在以電信相關和工業設備為首的應用中、最近在使用電池組的應用中使用量增加,因此其需求日益高漲。然而,現狀是可供應具有60V以上耐壓的DC/DC轉換器

2018-12-04 10:10:43

系統,成為能夠滿足這種要求的最高能效解決方案。人們早已認識到模塊化DC-DC轉換器具有更高的能效和可靠性,但因其高成本,制造商并未在設計中使用這種轉換器,尤其是在需要大量轉換器時。盡管開發成本仍在增加

2019-03-29 12:00:22

DC-DC轉換器中能實現電池充電和母線接口功能,就能獲得極大的成本及尺寸優勢。圖1:現有的隔離式雙向DC-DC轉換器拓撲圖1是廣泛使用的現有隔離式雙向DC-DC轉換器拓撲。可首先將輸入DC電壓逆變成AC電壓

2021-11-20 08:00:00

DC-DC轉換器中能實現電池充電和母線接口功能,就能獲得極大的成本及尺寸優勢。圖1:現有的隔離式雙向DC-DC轉換器拓撲圖1是廣泛使用的現有隔離式雙向DC-DC轉換器拓撲。可首先將輸入DC電壓逆變成AC電壓

2021-11-23 06:30:00

如何為DC/DC直流電源轉換器選擇最佳的開關頻率呢?有哪幾種設計方案?

2021-11-01 07:58:03

輔助轉換器等各種應用中都是必不可少的。 對于電流絕緣,DC/DC轉換器通常使用在相對較高頻率下工作的變壓器。變壓器電壓和電流的基頻通常與所用功率半導體的開關頻率相同或相似。功率半導體的較高開關頻率

2023-02-20 15:32:06

假設您有一個 SiC 晶體管應用,它需要大約 +15V 的正柵極驅動電壓和大約 -4V 的負柵極驅動電壓,以獲得最佳性能和最低開關損耗(圖 1)。您查看制造商的數據表,發現具有這種特殊非對稱輸出電壓組合的隔離式 DC/DC 轉換器不作為標準產品存在。你能做什么?

2022-04-12 17:23:13

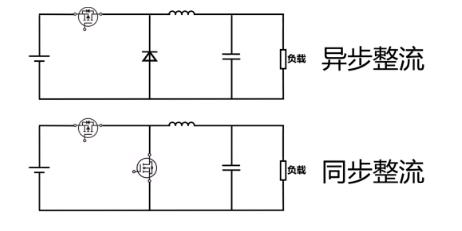

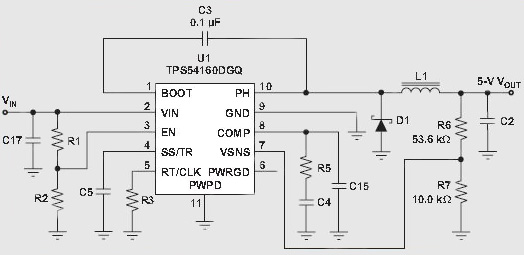

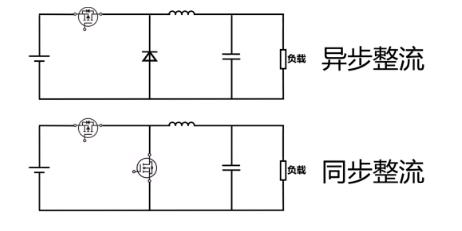

本文主要探討了DC-DC應用中轉換器功率級選擇的影響。

2019-08-16 07:20:56

一、正確理解DC/DC轉換器 DC/DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換器。DC/DC轉換器分為三類:升壓型DC/DC轉換器、降壓型DC/DC轉換器以及升降壓型DC/DC轉換器

2018-10-09 14:24:39

曲線。您經常會發現在 DC 電源上疊加的高頻率噪聲信號。這種高頻率噪聲可能會是開關電源的紋波。低頻率 PSRR 非常好,其可提高低頻率電源變化的抑制效果。另一方面,由于高頻率時 PSRR 較低,因此

2018-09-19 11:28:26

來從正電源產生負dc電壓(圖1a))。這種類型的電壓轉換器會從5V輸入產生一個低功率的負偏置電壓。該電路模擬電荷泵dc / dc轉換器,該轉換器適用于產生極性與輸入電壓相反的輸出電壓。與常規轉換器一樣

2020-06-03 13:57:17

轉換器的電路結構 圖5顯示的是反激式DC-DC轉換器的電路結構,其廣泛應用于低功率,高輸入電壓的應用場合,調節能力比正激式轉換器弱,通常工作于非連續傳導模式。 3.正激式與反擊式的區別 從結構

2020-12-09 15:25:24

一、正確理解DC/DC轉換器: DC/DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換器。DC/DC轉換器分為三類:升壓型DC/DC轉換器、降壓型DC/DC轉換器以及升降壓型DC/DC轉換器

2021-11-16 06:32:19

“已經差不多快接近極限了”,就是說AC/DC轉換器不同對嗎?確實DC/DC轉換器非常高效且小巧。但是DC/DC轉換器的輸入電壓最高也就數十伏,而AC/DC轉換器的輸入為AC,例如作為設備電源的商用電源電壓

2018-12-03 14:40:31

全球知名的半導體廠商羅姆(ROHM)公司推出了一款用于DC-DC轉換器的高電壓檢測器IC——BM67290FV-C。該芯片具有內置磁隔離器,隔離電壓最高可達2,500Vrms。它能夠將將輸入電壓轉換

2019-04-09 05:01:17

很多硬件設計者,都沒有正確的理解和使用DC/DC轉換器,下面小編整理了一些特別有用的文章作為福利送給大家!一、正確理解DC/DC轉換器DC/DC轉換器為轉變輸入電壓后有效輸出固定電壓的電壓轉換器

2019-11-24 08:00:00

)配置的多個DC/DC降壓穩壓器進行同步。對多個轉換器進行相移可防止ON時間重疊和減小RMS電流、紋波和輸入電容要求,這可改善系統電磁干擾并提高功率效率。該方法還可消除對高輸入濾波電路的需要,并解決與拍頻

2018-12-03 11:26:43

后,如果DC輸出電壓設定值為12V,則就轉換成12VDC。圖片中省略了高頻率AC電壓的整流波形,但它是使用1個二極管的半波整流。整理AC轉換至DC的過程和工作狀況,一次側會直接整流-平滑100VAC

2018-11-30 11:36:01

備用模式時的功耗方面取得了很大進步。就用于節能型 DC/DC 轉換器的電源管理集成電路而言,必須具有兩個主要特點。首先,必須在寬負載電流范圍內具有非常高的轉換效率。其次,在備用和停機模式時必須有低靜態

2019-05-13 14:11:41

Buck轉換器是一種開關模式的降壓型轉換器,它能提供在高壓降比 (VIN/VOUT) 和高負載電流下的高效率與高彈性。在本論壇能否介紹幾種Buck架構DC-DC轉換器?

2019-09-18 16:21:14

/DC轉換器IC的耐壓劃分與典型的輸入電源的關系示意圖。輸入電源的順序不單是標稱電壓、還加進了假設需要的余量。另外,如前所述,隨著朝高耐壓方向的發展,供應商越來越少,產品數和變化也越來越少。不管怎么說,現狀是“80V耐壓”處于頂級位置。< 相關產品信息 >DC/DC轉換器

2018-12-03 14:44:01

尺寸、小的靜態電流、較小的工作電壓、低噪聲高功能集成度、足夠的輸出電壓調節能力、低安裝成本。一、DC/DC轉換器工作效率①電感式DC/DC轉換器:電池供電的電感式DC/DC轉換器的轉換效率為80

2019-03-25 16:31:54

模式:突發模式和強制連續工作(固定頻率PWM)。還有一個精確的可編程RUN引腳,用于啟用轉換器。 DC2119A的輸入電壓范圍為2.7V至40V。演示板的輸出電壓設置為5.0V。 LTC3115-2采用專有的低噪聲開關算法,可在高于,低于或等于輸出電壓的輸入電壓下優化效率,并確保工作模式之間的無縫轉換

2019-04-17 15:13:31

PAM2304 3Mhz,1A降壓DC-DC轉換器的典型應用。 PAM2304是一款降壓型電流模式DC-DC轉換器。在高負載時,恒定頻率PWM控制可實現出色的穩定性和瞬態響應

2019-03-14 14:17:05

集成式DC/DC轉換器結構是怎樣的?如何去分析它的工作原理?

2021-04-07 07:03:09

結構,輸出電壓均低于輸入電壓,從而稱之為降壓型DC-DC轉換器。 2.升壓型DC-DC轉換器 升壓型DC-DC轉換器中所用的電路元件與降壓型結構相同,有著相似的結構,只是將開關和電感的位置進行互換

2020-12-09 15:28:06

DN53- 高性能頻率補償使DC-DC轉換器具有75μs的高穩定性響應

2019-07-16 16:10:11

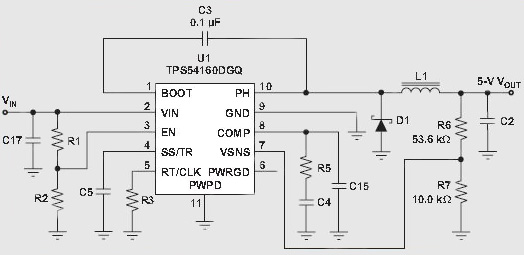

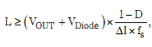

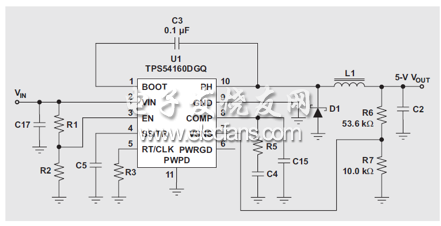

DC/DC 轉換器的設計頻率越來越快,目的是減小輸出電容和電感的尺寸,以節省電路板空間。正因如此,現在市場上出現越來越多工作在高輸入電壓下的DC/DC 轉換器,其可提供線壓瞬態保護,從而使更快頻率

2017-06-16 16:26:21 16

16 因此,頻率超過1 MHz的轉換器對電源系統的影響不僅僅局限于它的尺寸和效率。因此,在設計高輸入電壓和低輸出電壓的高開關頻率的DC/DC轉換器時,存在著權衡取舍。本文探討了一些設計實例,證明了在高頻率下切換高輸入電壓降壓型DC/DC轉換器的優點和缺點。

2017-06-24 09:57:34 21

21

電子發燒友App

電子發燒友App

評論