摘要

相位噪聲是時鐘、射頻頻綜最為關注的技術指標之一。影響鎖相環相噪的因素有很多,比如電源、參考源相噪、VCO 自身的相噪、環路濾波器的設置等。其中,電源引入的低頻噪聲往往對鎖相環的近端相噪有著很大的影響。對于高性能的時鐘和射頻頻綜產品,為了獲得極低的相噪性能,往往采用低噪聲的LDO 供電。然而,采用不同的LDO 給頻綜供電,取得的相噪性能往往會有很大差別,同時,LDO 外圍電路設計也會影響到頻綜的相噪性能。

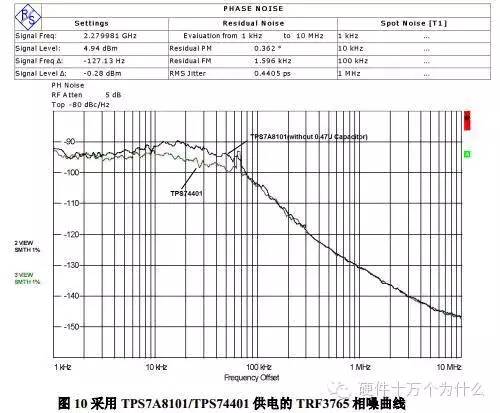

本文首先簡要地介紹了LDO 的噪聲來源及環路穩定性對輸出噪聲的影響;其次,根據調頻理論推導出VCO 的相位噪聲與LDO 的噪聲頻譜密度的理論計算關系。在此基礎上,為了驗證LDO 噪聲對射頻頻綜輸出相噪的影響,分別采用TPS7A8101 和TPS74401 LDO 評估板給TRF3765 射頻頻綜評估板供電,對比測試這兩種情況下的TRF3765 相噪曲線;同時,為了驗證LDO 環路穩定性對頻綜相噪的影響,針對TPS7A8101 評估板的參考電路做出部分修改,并對比測試了電路修改前后的TRF3765 輸出相噪。

1、LDO?噪聲來源及環路穩定性對輸出噪聲影響

1.1 LDO?噪聲來源

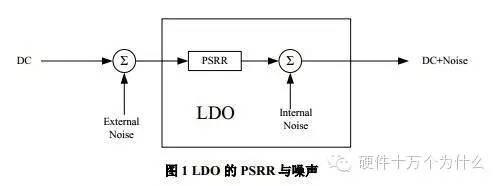

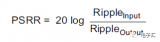

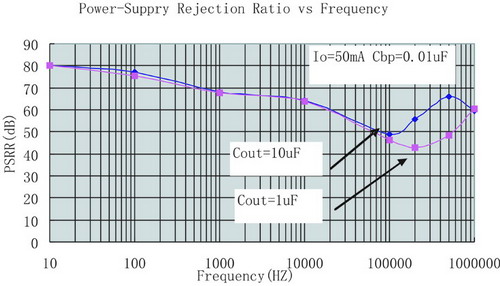

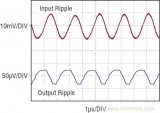

LDO 的噪聲分為LDO 內部的噪聲和LDO 外部的噪聲。LDO 內部的噪聲來自于內部電路的帶隙基準源,放大器以及晶體管。LDO 外部的噪聲來自于輸入。在LDO 的手冊中,PSRR 是表征LDO抑制外部噪聲的能力,但PSRR 高并不代表LDO 內部噪聲小。LDO 的總輸出噪聲才是表征LDO內部噪聲抑制的參數,一般在電氣特性表里用單位μVRMS 表示,或者在噪聲頻譜密度圖上表示。

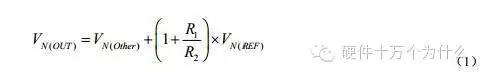

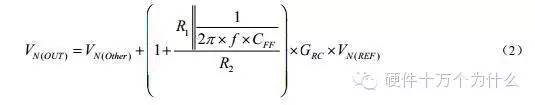

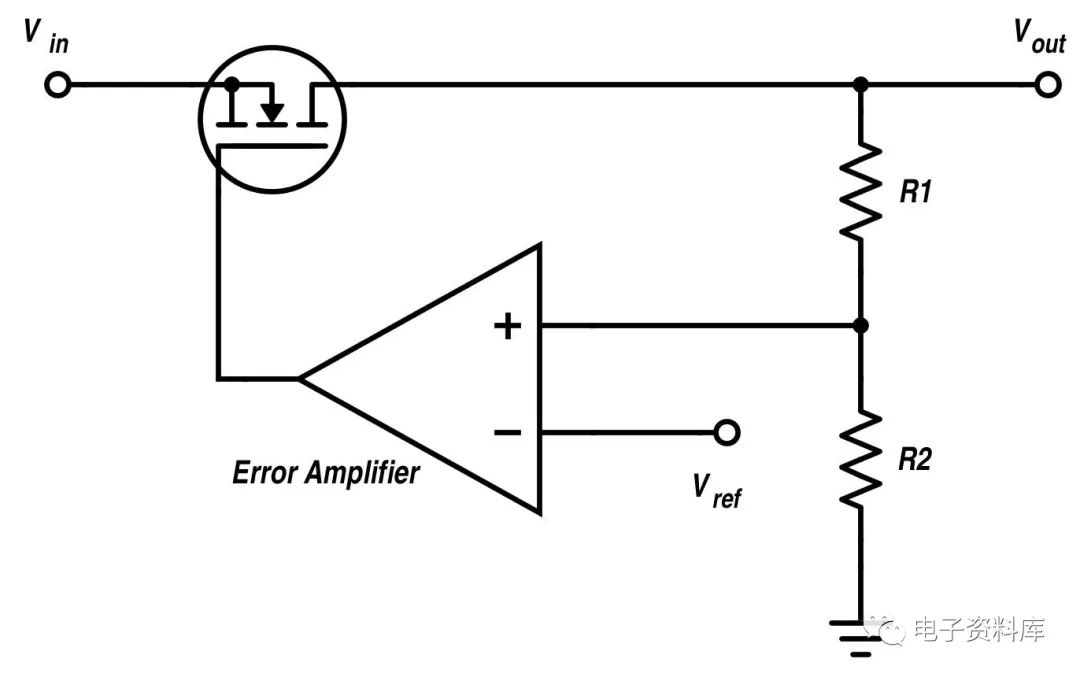

圖2 是LDO 內部結構框圖,VN 代表等效噪聲源。噪聲源包括帶隙基準源產生的噪聲VN (REF) ,誤差放大器產生的噪聲VN (AMP) ,FET 產生的噪聲VN (FET) 以及反饋電阻產生的噪聲VN ( R1) 和VN ( R2) 。在大多數情況下,由于帶隙基準源電路是由很多不同的電阻、晶體管和電容組成,它所產生的噪聲會遠遠大于反饋電阻產生的噪聲。而且帶隙基準源是誤差放大器的輸入,它所產生的噪聲也會經由誤差放大器放大來控制FET,所以誤差放大器本身以及FET 所產生的噪聲也會比帶隙基準源的噪聲要低。可以說,LDO 內部最大的噪聲源就是帶隙基準源。我們把LDO 輸出噪聲VN (OUT) 表示為

VN ( Other) 是VN ( AMP) 以及VN (FET) 的和。由公式1 可以得出,輸出噪聲最小值出現在R1 短接到FB,誤差放大器的增益近似為1 的時候。

1.2 LDO?噪聲抑制方法

為了抑制帶隙基準源產生的噪聲,有三種辦法。

一是降低誤差放大器的帶寬,抑制了帶隙基準源的高頻噪聲。但是降低帶寬會使LDO 的動態性能降低。

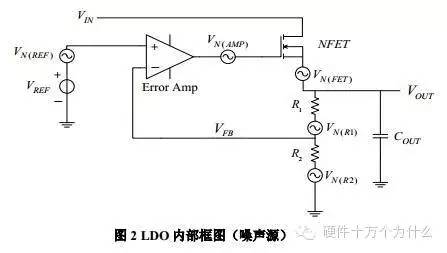

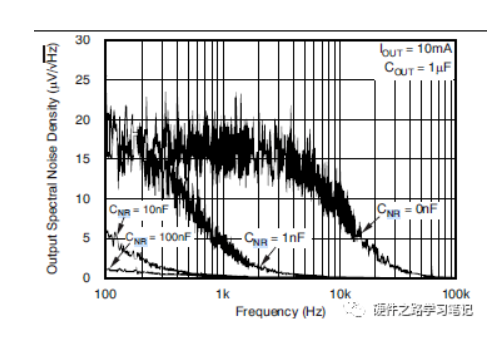

二是在帶隙基準源和誤差放大器之間加低通濾波。高性能的LDO 都會有一個噪聲抑制NR 管腳,CNR 并聯在帶隙基準源和GND 之間,起到低通濾波的作用。如圖3 所示。

三是在反饋電阻R1 上增加前饋電容CFF 。在增加了CFF 和CNR 后,輸出噪聲可以表示為

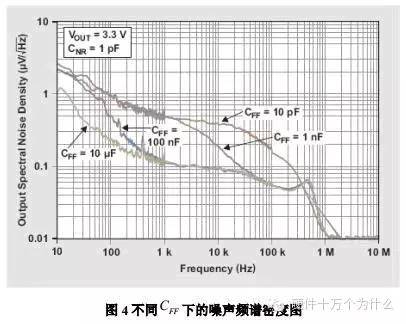

從式2 可以得出,CFF 越大,輸出噪聲就越小。頻率越高,輸出噪聲越小。

圖4 是不同CFF 下的噪聲頻譜密度圖。可以看出,CFF 越大,噪聲從低頻開始都能被很好的抑制。CFF 太小的時候,抑制噪聲的作用就不太明顯。當頻率很高的時候,不管用多大的CFF ,噪聲頻譜密度相差不會太大。所以,增加合適的前饋電容CFF ,對改善LDO 低頻噪聲有非常好的效果。

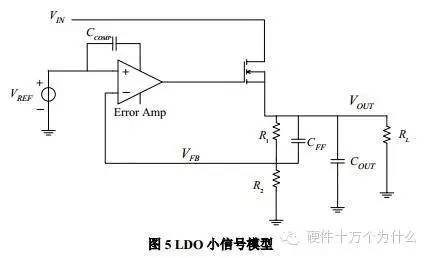

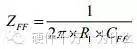

1.3 LDO?環路穩定性與輸出噪聲的關系

從LDO 的小信號分析可以看出,LDO 有兩個低頻極點,如果沒有合適的零點補償,LDO 的穩定裕度不夠,就有可能產生震蕩。穩定裕度不夠的LDO 產生的內部噪聲會更大。上節中提到第三種噪聲抑制方法,即增加前饋電容CFF 是實際上為了改善系統穩定裕度。由CFF 與R1組成一個低頻零點, 。

。

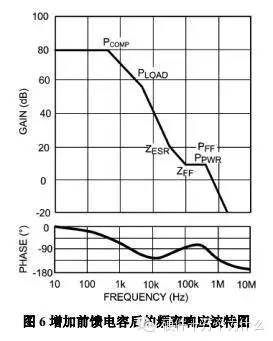

由下圖的頻率響應可以看出,零點是相位裕度有了很大的提升,增加了系統穩定性,從而減小了系統低頻噪聲。

2、LDO?噪聲與VCO?輸出相噪的關系

電源引入噪聲對鎖相環中各個有源器件都可能造成影響,其中最為敏感的部分是VCO,本文將著重討論LDO 輸出噪聲對VCO 相噪的影響。

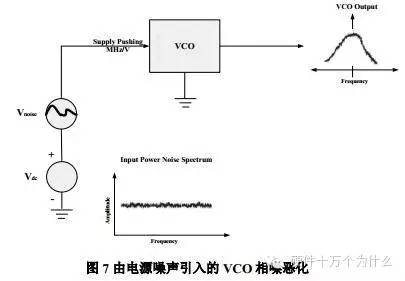

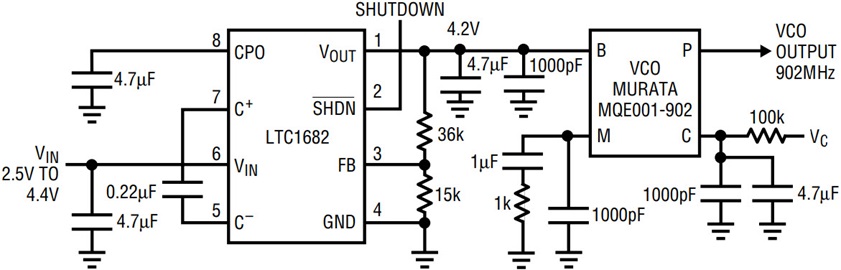

一個典型的LDO 供電的頻綜系統框圖如圖7 所示:加載在電源上的噪聲信號通過頻率調制過程調制到VCO 的輸出,造成VCO 輸出相噪惡化。

根據經典調頻系統理論,調制指數β由式(3)來表示

對于電源噪聲調制,式中的頻率背離(Frequency Deviation)可由下式得到

式中,Kpush 是VCO 的電源推壓指數,它表征的是VCO 對電源噪聲波動的靈敏度,單位用MHz/V 來表示;A 是電源噪聲信號幅度。

對于采用LDO 供電的射頻頻綜來說,通常用LDO 的指定頻率偏移的頻譜噪聲密度Sldo(f)(Noise Spectrum Density)來表征電源噪聲,由于它是一個RMS 電壓值,所以式(4)可以表示為

將式(5)帶入式(3),可以得到

式中,f 是相應的頻率偏移。

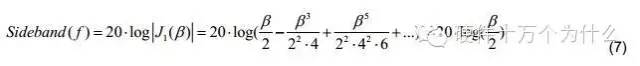

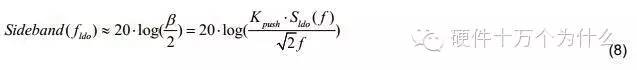

由不同頻率成分噪聲調制到載波輸出引起的單邊帶噪聲,由下式表示

將式(6)帶入式(7)有

由式(8)可見,對于給定的VCO,由于Kpush 是一個確定的值,因此由LDO 噪聲引起的VCO 輸出相噪是由LDO 的噪聲頻譜密度(Noise Spectrum Density)決定的。

3、采用不同LDO?進行射頻頻綜供電對比測試

3.1 TPS7A8101/TPS74401?頻綜供電對比測試

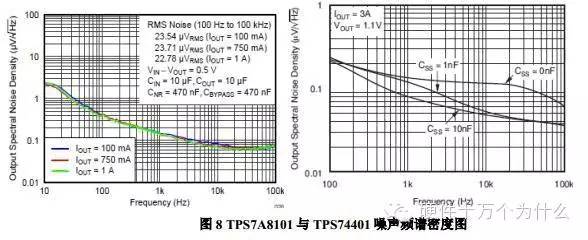

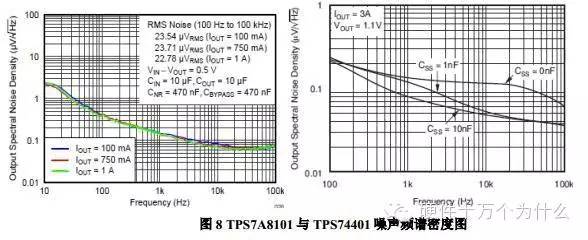

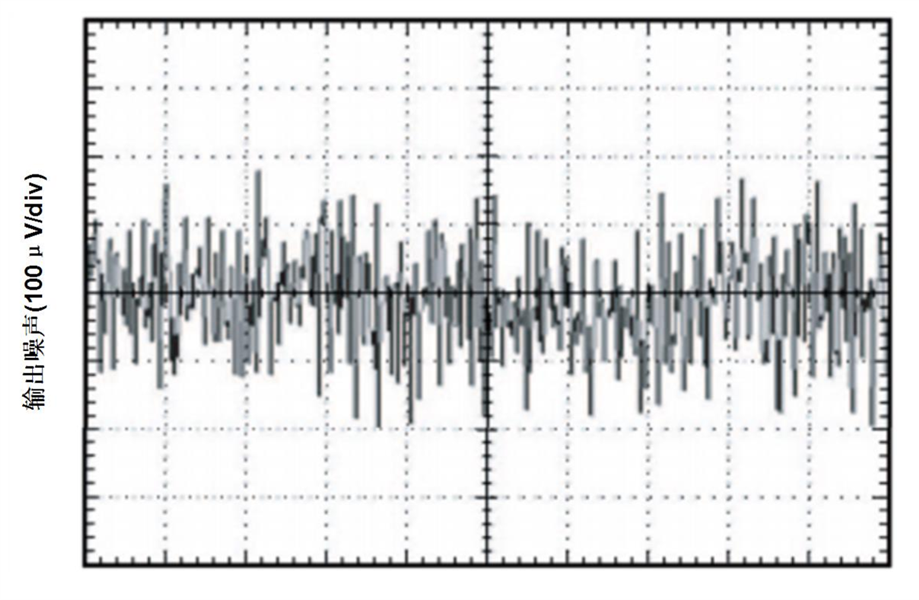

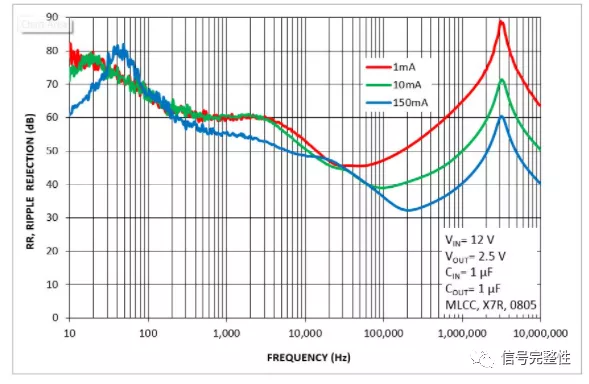

TPS7A8101 和TPS74401 是TI 推出的兩款高性能LDO 芯片。與TPS74401 相比, 由于具有更高的環路增益和帶寬,TPS7A8101 具有更高的電源噪聲抑制比(PSRR);然而,由于具有更好的系統穩定性,TPS74401 擁有更低的噪聲頻譜密度(NSD),如下圖8 所示。

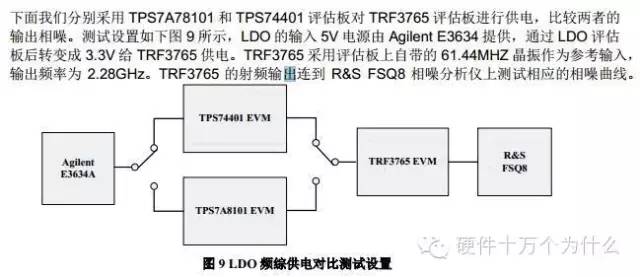

下面我們分別采用TPS7A78101 和TPS74401 評估板對TRF3765 評估板進行供電,比較兩者的輸出相噪。測試設置如下圖9 所示,LDO 的輸入5V 電源由Agilent E3634 提供,通過LDO 評估板后轉變成3.3V 給TRF3765 供電。TRF3765 采用評估板上自帶的61.44MHZ 晶振作為參考輸入,輸出頻率為2.28GHz。TRF3765 的射頻輸出連到R&S FSQ8 相噪分析儀上測試相應的相噪曲線。

兩者對比測試結果如下圖10 所示,

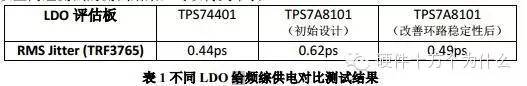

由上圖看見,采用TPS7A8101 供電,TRF3765 在整個積分區間內(1KHz~10MHz)的RMS 抖動為0.62ps;而TPS74401 的RMS 抖動僅為0.44ps。

3.2 TPS7A8101?輸出電路優化及其對頻綜相噪的影響

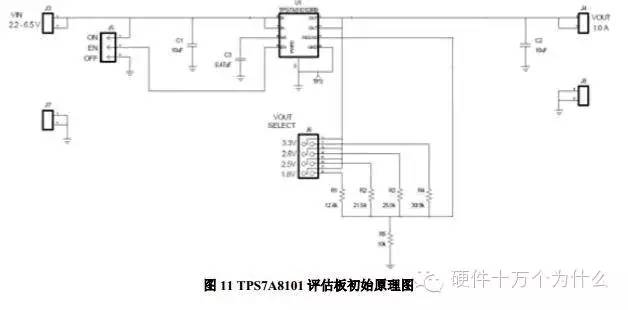

TPS7A8101 評估板初始原理圖如圖11 所示,由上節的測試結果可知,采用該電路給TRF3765供電,RMS 抖動為0.62ps。

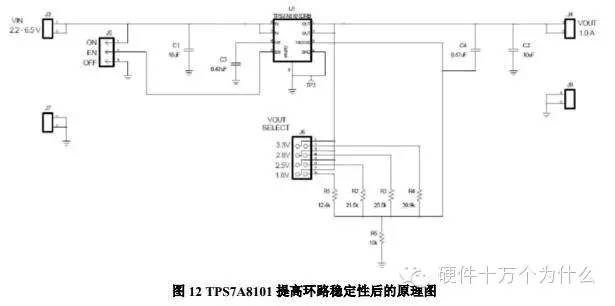

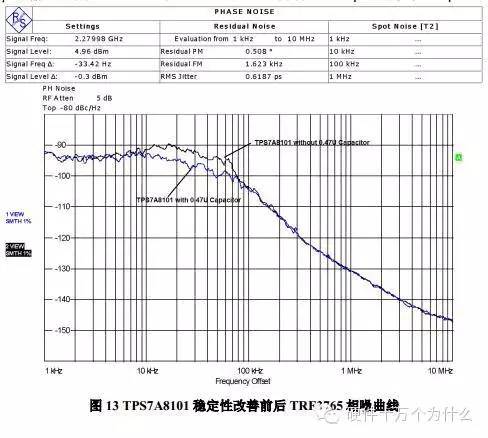

第一章中我們已經討論了LDO 加一個前饋電容可以有效的提高電源的環路穩定性,從而降低LDO 的輸出噪聲頻譜密度。基于此,我們在TPS7A8101 輸出加一個0.47 μF 的前饋電容,修改后的原理圖如下圖12 所示。

針對修改前后的設計,我們對比測試了相應的TRF3765 相噪曲線,如圖13 所示,由圖可見,增加0.47 μF 輸出電容后,1KHz 到10MHz 的RMS 抖動由0.62ps 提高到0.49ps。

4?結論

綜合以上兩組測試的測試結果,可以得到下表

由表1 可以看到,由于TPS74401 的噪聲頻譜密度最小,在給頻綜供電的時候可以取得最好的相噪性能;TPS7A8101 噪聲頻譜密度相對較大,在給頻綜供電的時候取得的相噪性能相對較差;但是通過優化TPS7A8101 的輸出電路設計,頻綜的相位噪聲得到了明顯的改善。

實測結果很好的驗證了前文的理論分析,即:LDO 的噪聲頻譜密度參數(NSD)決定了由電源噪聲引起的VCO 相噪惡化;通過提高LDO 的環路穩定性可以達到降低噪聲頻譜密度的目的,從而改善頻綜的輸出相噪。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論