開關電源輸入用共模濾波器中包括電容器、電感、鐵氧體磁珠和電阻等部件。接下來將對其中使用電容和電感降噪的對策進行介紹,這也可以稱為“噪聲對策的基礎”。在這里使用簡單的四元件模型。如果要進一步表達高頻諧振時,可能需要更多的元件模型。

? ? 電容的頻率特性

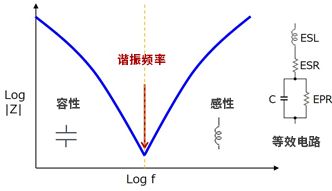

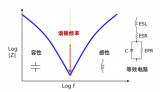

? 探討利用電容器來降低噪聲時,充分了解電容器的特性是非常重要的。右下圖為電容器的阻抗和頻率之間的關系示意圖,是電容器最基礎的特性之一。

? 電容器中不僅存在電容量C,還存在電阻分量ESR(等效串聯電阻)、電感分量ESL(等效串聯電感)、與電容并聯存在的EPR(等效并聯電阻)。EPR與電極間的絕緣電阻IR或電極間有漏電流的具有相同的意義。可能一般多使用“IR”。

?

? C和ESL形成串聯諧振電路,電容器的阻抗原則上呈上圖所示的V字型頻率特性。到諧振頻率之前呈容性特性,阻抗下降。諧振頻率的阻抗取決于ESR。過了諧振頻率之后,阻抗特性變為感性,阻抗隨著頻率升高而升高。感性阻抗特性取決于ESL。

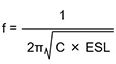

? 諧振頻率可通過以下公式計算。 從該公式可以看出,容值越小、ESL越低的電容器,諧振頻率越高。如果將其應用于噪聲消除,則容值越小、ESL越低的電容器,頻率越高,阻抗越低,因此可以很好地消除高頻噪聲。

從該公式可以看出,容值越小、ESL越低的電容器,諧振頻率越高。如果將其應用于噪聲消除,則容值越小、ESL越低的電容器,頻率越高,阻抗越低,因此可以很好地消除高頻噪聲。

? 雖然這里說明的順序有些前后顛倒,不過使用電容器降低噪聲的對策,是利用了電容器“交流通過時頻率越高越容易通過”這個基本特性,將不需要的噪聲(交流分量)經由信號、電源線旁路到GND等。

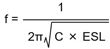

? 下圖為不同容值的電容器的阻抗頻率特性。在容性區域,容值越大,阻抗越低。另外,容值越小,諧振頻率越高,在感性區域阻抗越低。

?

下面總結一下電容器阻抗的頻率特性。

?

容值和ESL越小,諧振頻率越高,高頻區域的阻抗越低。

容值越大,容性區域的阻抗越低。

ESR越小,諧振頻率的阻抗越低。

ESL越小,感性區域的阻抗越低。

簡單來說,阻抗低的電容器具有出色的噪聲消除能力,不同的電容器其阻抗的頻率特性也不同,所以這一特性是非常重要的確認要點。選擇降噪用電容器時,請根據阻抗的頻率特性來選型(而非容值)。

? 選擇降噪用電容器時,確認頻率特性需要意識到連接的是LC的串聯諧振電路(而非電容)。

? 關鍵要點:

? ?降噪用電容器的選型需要根據阻抗的頻率特性進行(而非容值)。

? ?容值和ESL越小,諧振頻率越高,高頻區域的阻抗越低。

? ?容值越大,容性區域的阻抗越低。

? ?ESR越小,諧振頻率的阻抗越低。

? ?ESL越小,感性區域的阻抗越低。

?

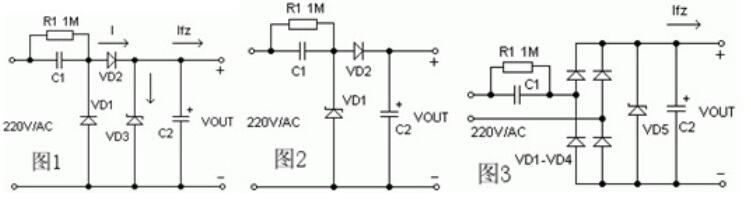

下面將介紹采用電容器來降低噪聲時的概要和示意圖。

? ? 使用電容器降低噪聲

? 噪聲分很多種,性質也是多種多樣的。所以,噪聲對策(即降低噪聲的方法)也多種多樣。在這里主要談開關電源相關的噪聲,因此,請理解為DC電壓中電壓電平較低、頻率較高的噪聲。另外,除電容外,還有齊納二極管和噪聲/浪涌/ESD抑制器等降噪部件。不同的噪聲性質,所需要的降噪部件也各不相同。如果是DC/DC轉換器,多數會根據其電路和電壓電平,用LCR來降低噪聲。

? 使用電容器降低噪聲的示意圖

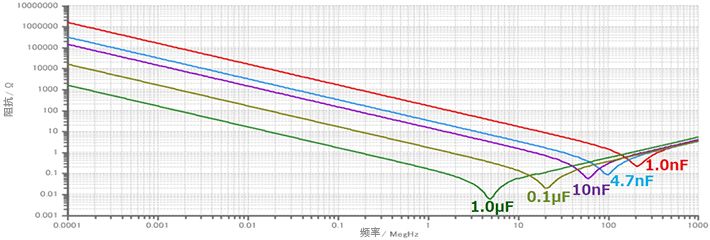

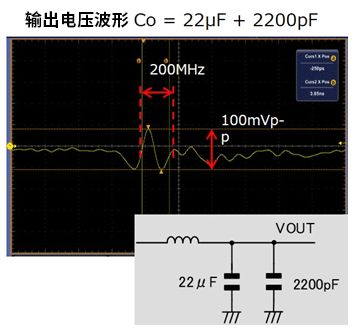

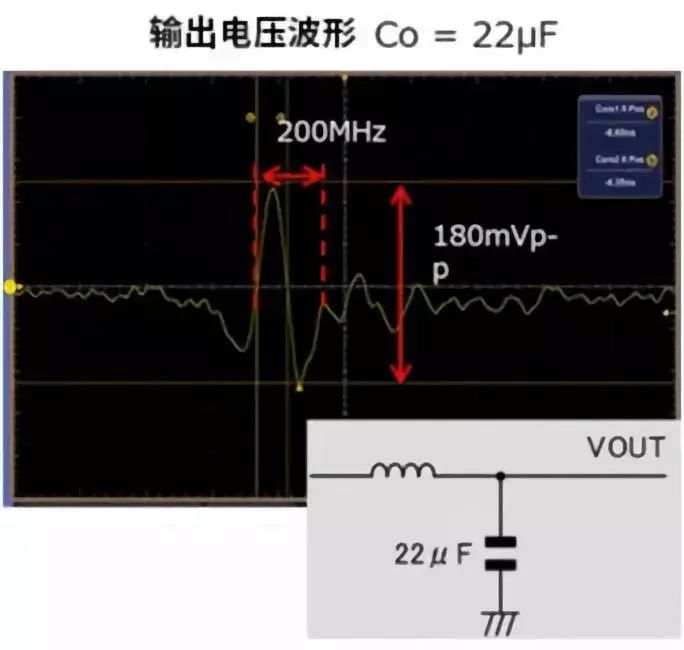

? 下面是通過添加電容器來降低DC/DC轉換器輸出電壓噪聲的示例。

?

左側的波形是輸出端LC濾波器的電容為22μF時,在約200MHz的頻率范圍存在180mVp-p左右的噪聲(振鈴、反射)。右側波形是為了降低這種噪聲而添加了2200pF電容后的結果。從波形圖可以看出,添加2200pF的電容使噪聲降低了100mV左右。

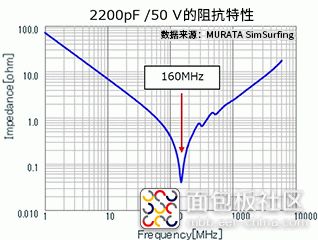

? 這里應該思考的是“為什么是2200pF”。右下圖為所添加電容器的阻抗頻率特性。

? 之所以選擇2200pF的電容,是因為阻抗在160MHz附近最低,利用這種阻抗特性,可降低噪聲幅度約2MHz。這是通過添加電容器來降低目標噪聲頻率的阻抗,從而降低噪聲幅度的手法。像這樣通過添加電容器來降低噪聲時,需要把握噪聲(振鈴、反射)的頻率,并選擇具有相應阻抗的頻率特性的電容器。

?

本文簡單介紹了利用電容器來降低噪聲的對策。下一篇文章將介紹去耦電容的有效使用方法。

? 關鍵要點:

? ?通過降低目標噪聲頻率的阻抗來降低噪聲幅度。

? ?降噪用電容器的選型需要根據阻抗的頻率特性進行(而非容值)。

去耦電容的有效使用方法

? 去耦電容有效使用方法的要點大致可以分為以下兩種。另外,還有其他幾點需要注意。本文就以下三點中的“要點1”進行介紹。

?

?要點1:使用多個去耦電容

?要點2:降低電容的ESL(等效串聯電感)

?其他注意事項

要點1:使用多個去耦電容

? 去耦電容的有效使用方法之一是用多個(而非1個)電容進行去耦。使用多個電容時,使用相同容值的電容時和交織使用不同容值的電容時,效果是不同的。

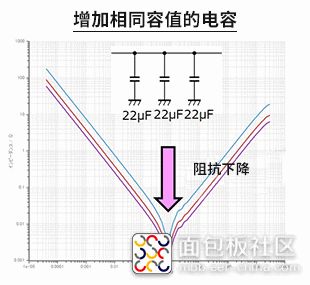

? ?使用多個容值相同的電容時

?

右圖是使用1個22μF的電容時(藍色)、增加1個變為2個時(紅色)、再增加1個變為3個(紫色)時的頻率特性。如圖所示,當增加容值相同的電容后,阻抗在整個頻率范圍均向低的方向轉變,也就是說阻抗越來越低。這一點可通過思考并聯連接容值相同的電容時,到諧振點的容性特性、取決于ESR(等效串聯電阻)的諧振點阻抗、諧振點以后的ESL(等效串聯電感)影響的感性特性來理解。并聯的電容容值是相加的,所以3個電容為66μF,容性區域的阻抗下降。

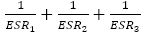

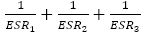

? 諧振點的阻抗是3個電容的ESR并聯,因此為 ,假設這些電容的ESR全部相同,則ESR減少至1/3,阻抗也下降。

,假設這些電容的ESR全部相同,則ESR減少至1/3,阻抗也下降。

? 諧振點以后的感性區域的ESL也是并聯,因此為 ,假設3個電容的ESL全部相同,則ESL減少至1/3,阻抗也下降。

,假設3個電容的ESL全部相同,則ESL減少至1/3,阻抗也下降。

? 由此可知,通過使用多個相同容值的電容,可在整個頻率范圍降低阻抗,因此可進一步降低噪聲。

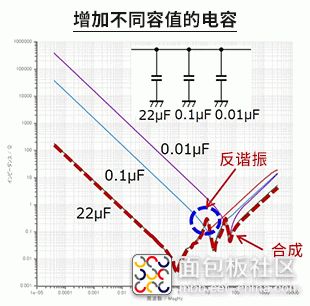

? ?使用多個容值不同的電容時

這些曲線是在22μF的電容基礎上并聯增加0.1μF、以及0.01μF的電容后的頻率特性。通過增加容值更小的電容,可降低高頻段的阻抗。相對于一個22μF電容的頻率特性來說,0.1μF和0.01μF的特性是合成后的特性(紅色虛線)。這里必須注意的是,有些頻率點產生反諧振,阻抗反而增高,EMI惡化。反諧振發生于容性特性和感性特性的交叉點。

? 所增加電容的電容量,一般需要根據目標降噪頻率進行選型。

? 另外,在這里給出的頻率特性波形圖是理想的波形圖,并未考慮PCB板的布局布線等引起的寄生分量。在實際的噪聲對策中,需要考慮寄生分量的影響。下一篇文章將介紹第2個要點。

? 關鍵要點:

? ?去耦電容的有效使用方法有兩個要點:①使用多個電容,②降低電容的ESL。

? ?使用多個電容時,容值相同時和不同時的效果不同。

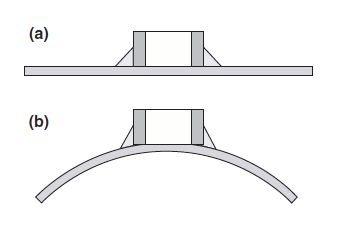

要點2:降低電容的ESL

? 去耦電容的有效使用方法的第二個要點是降低電容的ESL(即等效串聯電感)。雖說是“降低ESL”,但由于無法改變單個產品的ESL本身,因此這里是指“即使容值相同,也要使用ESL小的電容”。通過降低ESL,可改善高頻特性,并可更有效地降低高頻噪聲。

? ?即使容值相同也要使用尺寸較小的電容

? 對于積層陶瓷電容(MLCC),有時會準備容值相同但尺寸不同的幾個封裝。ESL取決于引腳部位的結構。尺寸較小的電容基本上引腳部位也較小,通常ESL較小。

?

右圖是容值相同、大小不同的電容的頻率特性示例。如圖所示,更小的1005尺寸的諧振頻率更高,在之后感性區域的頻率范圍阻抗較低。這正如在“電容的頻率特性”中所介紹的,電容的諧振頻率是基于以下公式的,從公式中可見,只要容值相同,ESL越低諧振頻率越高。另外,感性區域的阻抗特性取決于ESL,這一點也曾介紹過。

?  關于噪聲對策,當需要降低更高頻段的噪聲時,可以選擇尺寸小的電容。

關于噪聲對策,當需要降低更高頻段的噪聲時,可以選擇尺寸小的電容。

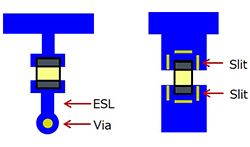

? ?使用旨在降低ESL的電容

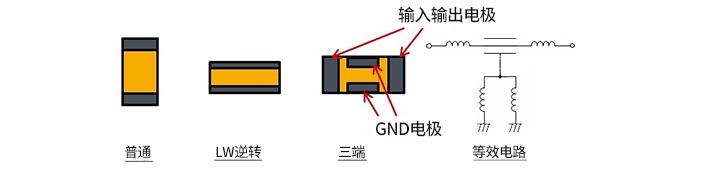

? 積層陶瓷電容中,有些型號采用的是旨在降低ESL的形狀和結構。

?

如圖所示,普通電容的電極在短邊側,而LW逆轉型的電極則相反,在長邊側。由于L(長度)和W(寬度)相反,故稱“LW逆轉型”。是通過增加電極的寬度來降低ESL的類型。

? 三端電容是為了改善普通電容(兩個引腳)的頻率特性而優化了結構的電容。三端電容是將雙引腳電容的一個引腳(電極)的另一端向外伸出作為直通引腳,將另一個引腳作為GND引腳。在上圖中,輸入輸出電極相當于兩端伸出的直通引腳,左右的電極當然是導通的。這種輸入輸出電極(直通引腳)和GND電極間存在電介質,起到電容的作用。

? 將輸入輸出電極串聯插入電源或信號線(將輸入輸出電極的一端連接輸入端,另一端連接輸出端),GND電極接地。這樣,由于輸入輸出電極的ESL不包括在接地端,因此接地的阻抗變得非常低。另外,輸入輸出電極的ESL通過在噪聲路徑直接插入,有利于降低噪聲(增加插入損耗)。

? 通過在長邊側成對配置GND電極,可抑制ESL;再采用并聯的方式,可使ESL減半。

? 基于這樣的結構,三端電容不僅具有非常低的ESL,而且可保持低ESR,與相同容值相同尺寸的雙引腳型電容相比,可顯著改善高頻特性。

? 下一章計劃對相關的幾點注意事項進行介紹。

? 關鍵要點:

? ?去耦電容的有效使用方法有兩個要點:①使用多個電容,②降低電容的ESL。

? ?通過降低電容的ESL,可改善高頻特性,并可更有效地降低高頻噪聲。

? ?有的電容雖然容值相同,但因尺寸和結構不同而ESL更小。

去耦電容的有效使用方法:其他注意事項

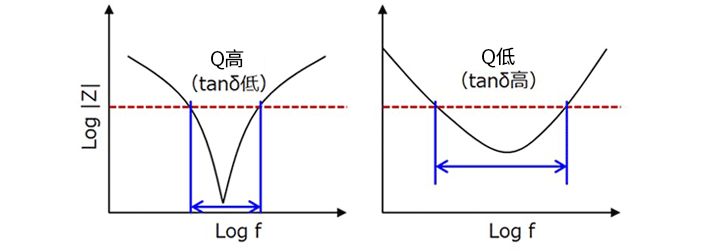

? ①Q較高的陶瓷電容

? 電容具有被稱為“Q”的特性。下圖即表示Q和頻率-阻抗特性之間的關系。

?

當Q值高時,阻抗在特定的窄帶會變得非常低。當Q值低時,阻抗雖然不會極度下降,但可以在很寬的頻段內降低。這種特性可能有助于符合某些EMC標準。例如,使用電容量變化較大的電容時,如果Q值很高,則可能存在無法消除目標頻率噪聲的個體。在這種情況下,還有一種通過使用具有低Q的電容來抑制波動影響的手法。

? ②熱風焊盤等的PCB圖形

?

旨在提高散熱性的熱風焊盤等的PCB圖形,圖形的電感分量會增加。電感分量的增加會使諧振頻率向低頻端移動,所以有時可能無法獲得理想的噪聲消除效果。

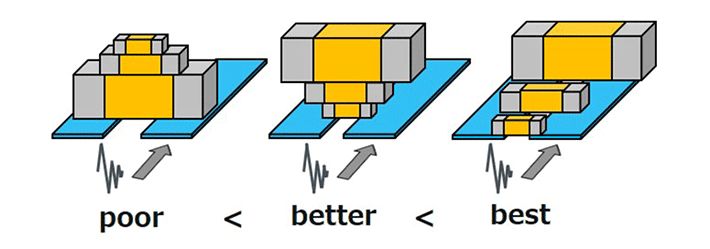

? ③探討對策時的電容試裝

? 試制后需要對高頻噪聲采取對策,可以考慮增加小容量的電容器。此時,如下圖所示,如果在大容量電容器上安裝要增加的電容器(左例),則縱向會增加額外的電感分量,因此不能充分發揮增加電容器的效果。在中間的例子中,雖然未違背“盡可能使小容量電容靠近噪聲源”的理論,但阻抗會與實際修改的PCB布局不同。最好的方法是以盡量接近實際修改的配置進行探討(右例)。

?

在探討對策時,也可能會發生雖然噪聲試驗OK,但安裝到修改后的PCB時NG的現象,因此需要在探討時就有意識地按照實際來安裝。

? ④電容的電容量變化率

? 噪聲對策用的電容的電容量變化率較大時,諧振頻率的波動會變大,目標消減頻段會產生變化或波動,有時很難找到理想的噪聲對策。尤其是需要在窄頻段大幅消除噪聲時,需要格外注意。下表表示電容量變化率和實際的電容量和諧振頻率之間的關系。仔細看這個表的話可以看出,雖然視條件而定,不過很多情況是無法接受的。

? 電容量變化率(%)

? 電容量(pF)

? 諧振頻率(MHz)

| +20 | 1,200 | 145 |

| +10 | 1,100 | 152 |

| +5 | 1,050 | 155 |

| ±0 | 1,000 | 159 |

| -5 | 950 | 163 |

| -10 | 900 | 168 |

| -20 | 800 | 178 |

| ? | ? | ? |

※ ?按L=1nH計算

? ⑤電容器的溫度特性

? 眾所眾知,電容的特性會受溫度影響。目前,EMC測試的溫度特性尚未標準化,但在某些應用中,不得不在明顯的高溫或低溫條件/環境下工作、或在會產生較大溫度變化的條件/環境下使用。

? 在這類情況下,非常有可能發生“④電容量變化率”中提到的問題,所以,用于噪聲對策的電容,需要盡量使用具有CH、C0G特性的溫度特性優異的產品。

關鍵要點: ?理解Q與頻率-阻抗特性之間的關系,并根據目的區分Q的差異。

? ?高Q電容窄帶阻抗急劇下降。低Q電容在較寬頻段相對平緩下降。

? ?PCB圖形的熱風焊盤等會增加電感分量,使諧振頻率向低頻端移動。

? ?探討對策時的試裝,如果不按照現實的修改實際安裝,很可能在修改后的PCB板上無法獲得探討時的效果。

? ?電容量變化率大時,諧振頻率會變化,無法獲得目標頻率理想的噪聲消除效果。

? ?在溫度條件和變動較大的嚴苛應用中,可以探討使用具有CH、C0G特性的溫度特性優異的電容。

總結

? 要點1:使用多個去耦電容

? 使用多個電容去耦時,使用多個相同容值的電容和交織使用不同容值的電容時,效果是不同的。

? ■使用多個相同容值的電容時

在整個頻率范圍內阻抗下降,可有效降低整體噪聲。

? ■使用多個不同容值的電容時

可降低更高頻段的阻抗,可有效降低高頻噪聲。但是需要注意的是,有些頻率會產生反諧振,阻抗反而增高,噪聲反而惡化。

? 要點2:降低電容的ESL

? 如果容量相同,則ESL越低諧振頻率越高,因此通過降低ESL可改善高頻特性,從而可更有效地降低高頻噪聲。

? ■即使容值相同也要使用尺寸較小的電容

ESL取決于電容引腳部位的結構,因此尺寸較小的電容基本上引腳部位也較小,通常ESL較小。當需要降低更高頻段的噪聲時,方法之一是選擇尺寸小的電容。但是,要注意DC偏置特性。

? ■使用旨在降低ESL的電容

積層陶瓷電容中,有些型號采用的是旨在降低ESL的形狀和結構,比如LW逆轉型電容、三端電容。

? 去耦電容的有效使用方法:其他注意事項

? ■Q較高的陶瓷電容

當Q值高時,阻抗在特定的窄帶會變得非常低。當Q值低時,阻抗雖然不會極度下降,但可以在較寬的頻段內降低。

? ■熱風焊盤等的PCB圖形

旨在提高散熱性的熱風焊盤等的PCB圖形,圖形的電感分量會增加,會使諧振頻率向低頻端移動,所以有時可能無法獲得理想的噪聲消除效果。

? ■探討對策時的電容試裝

增加小容量電容以降低高頻噪聲時,要基于“盡可能使小容量電容靠近噪聲源”的理論,以盡量接近實際修改的配置進行探討。探討時如果和修改后的配置不同,阻抗也會不同,很可能無法獲得評估時的效果。

? ■電容的電容量變化率

噪聲對策用的電容的電容量變化率較大時,諧振頻率的波動會變大,目標消減頻段會產生變化或波動,有時很難找到理想的噪聲對策。尤其是需要在窄頻段大幅消除噪聲時,需要格外注意。

? ■電容的溫度特性

電容的特性會受溫度影響,因此,在明顯的高溫、低溫、較大溫度變化的條件/環境下使用的應用,需要采用溫度特性優異的電容。

? 編輯:黃飛

?

電子發燒友App

電子發燒友App

評論