今天的內(nèi)容僅為設(shè)計模擬LDO的一些考慮。數(shù)字LDO和混合型LDO的內(nèi)容下次再更新。

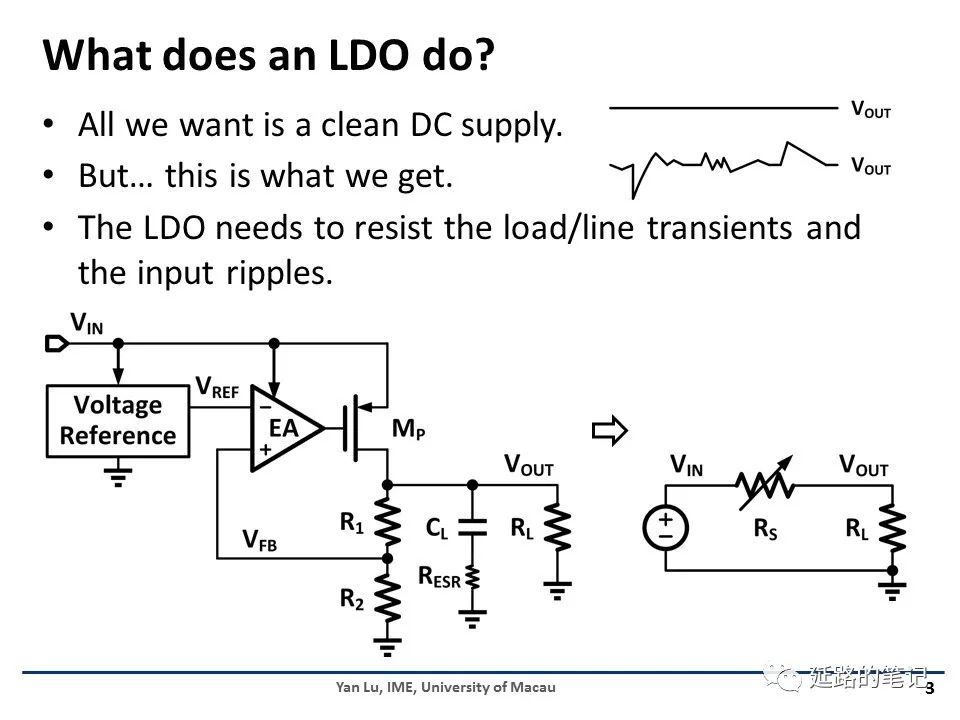

首先,讓我們了解一些基本概念。LDO是用來做什么的?對于一個電源來說,我們希望得到一個非常干凈的DC電壓,但是,負載的瞬態(tài)變化以及輸入紋波都是LDO需要考慮的干擾因素。

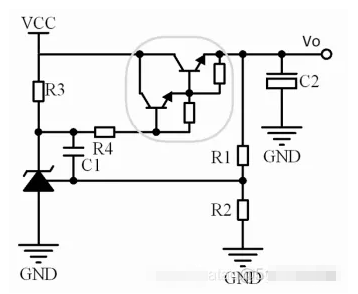

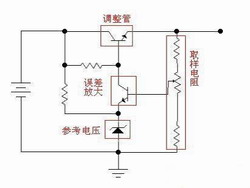

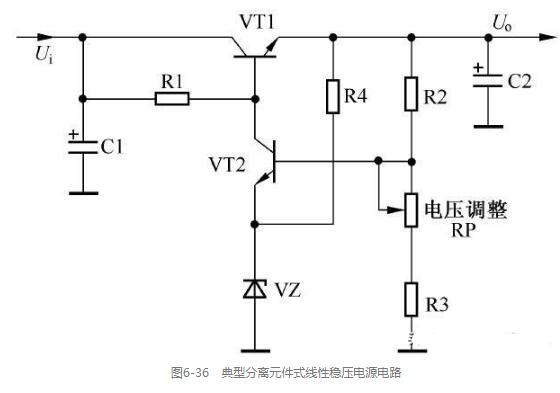

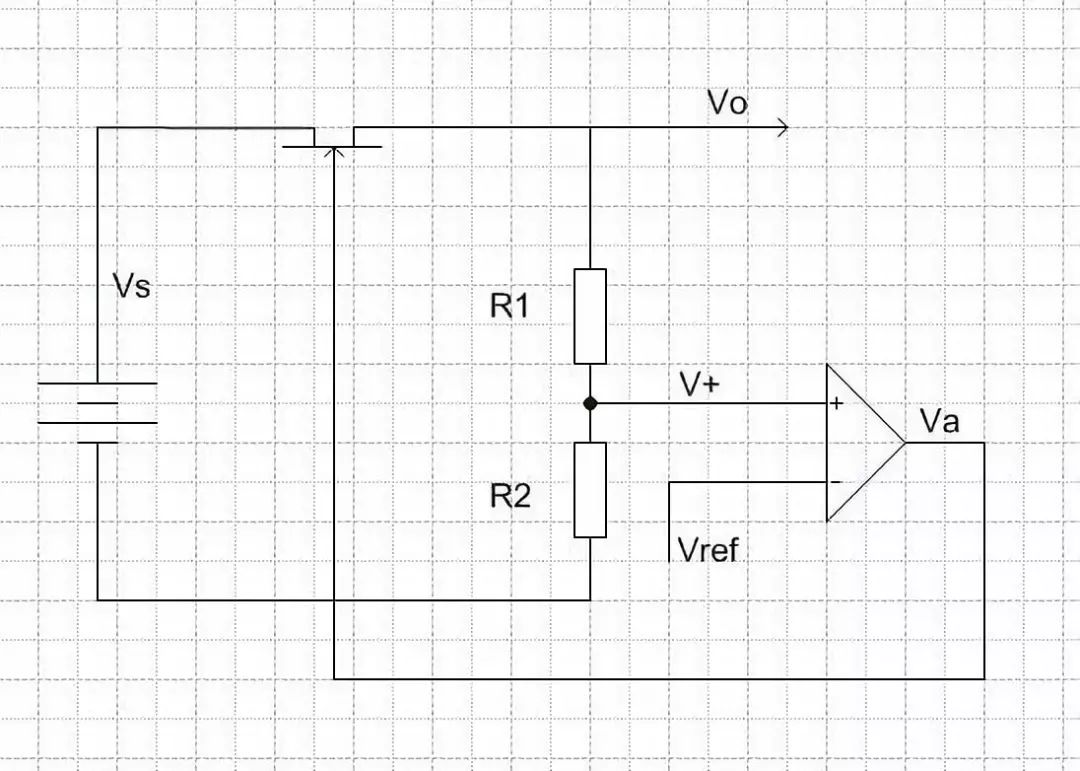

LDO使用誤差放大器來比較參考電壓和反饋的輸出電壓,通過調(diào)整功率晶體管的柵極電壓,來調(diào)整輸出電流大小。在等效電路模型中,LDO簡單地建模為一個可調(diào)電阻,確保當輸入電壓和負載發(fā)生變化時輸出電壓是穩(wěn)定的。

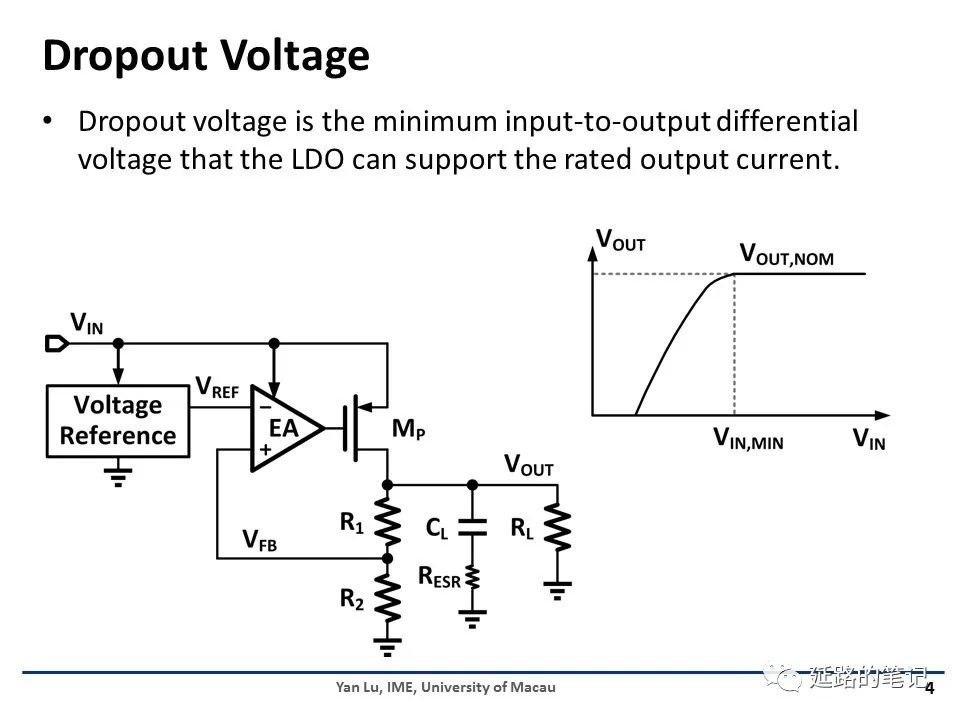

壓差(Dropout Voltage)的定義為:LDO能夠支持的額定最大輸出電流情況下,最小的輸入減輸出的電壓差。

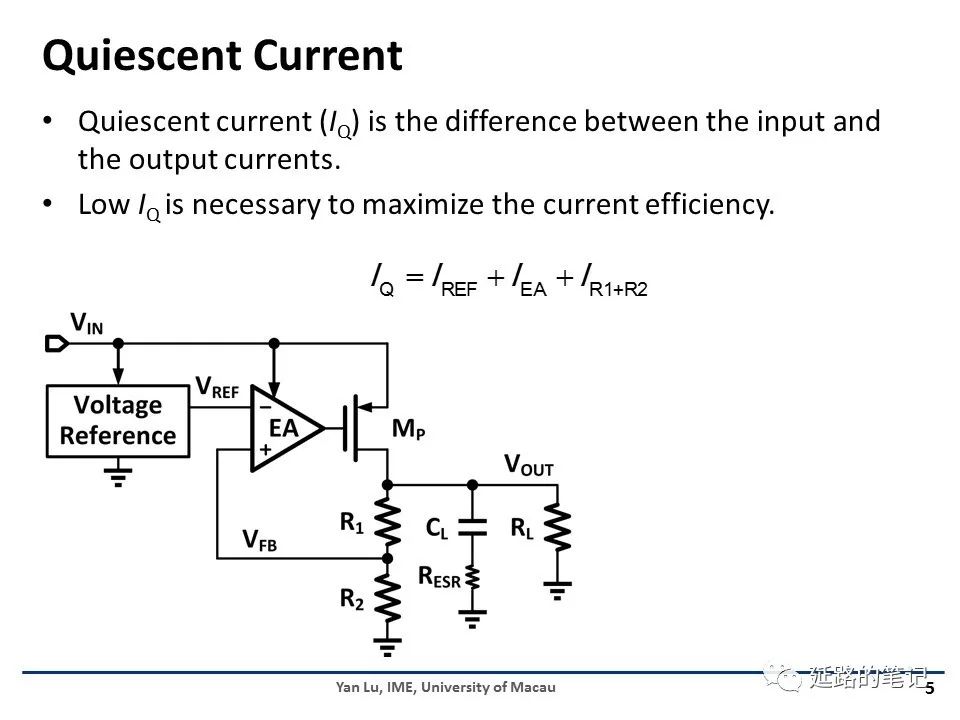

靜態(tài)電流IQ是輸入電流減輸出電流的差值。主要由三部分組成:基準電壓源的電流,誤差放大器的電流以及電阻分壓器的電流。顯然,為了使電流效率最高,需要盡量小。

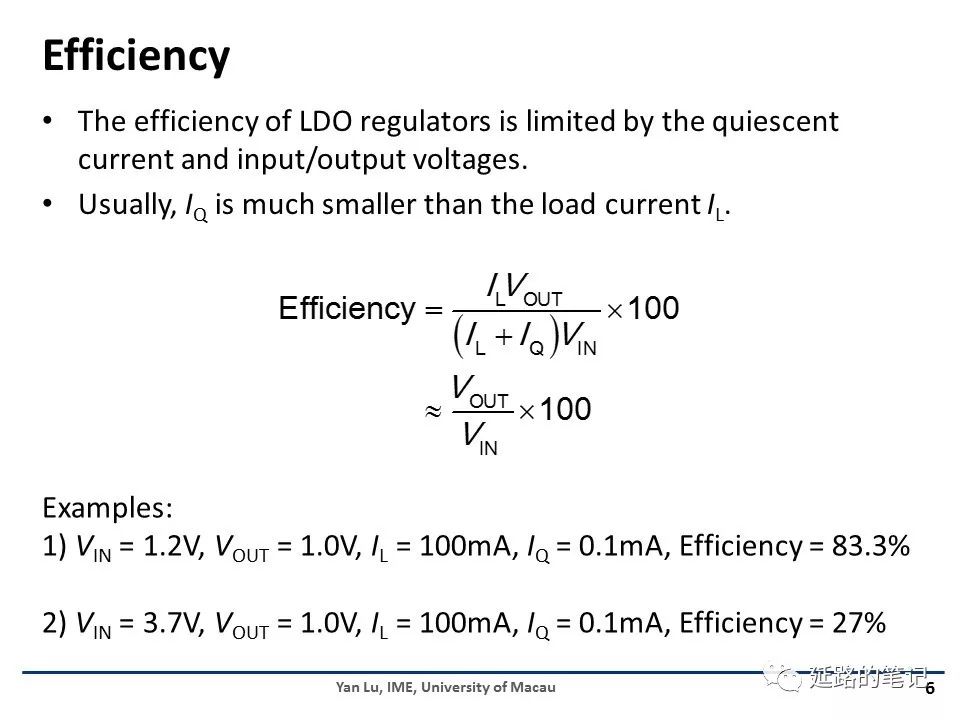

我們來看一下效率的計算公式。效率等于輸出功率與輸入功率之比。通常來說,IQ遠小于負載電流,故可以忽略不計。當輸入和輸出電壓差變大,效率會線性減小。因此效率低是LDO穩(wěn)壓器的主要問題。

可以考慮以下兩個例子,如果前級的DC-DC轉(zhuǎn)換器提供了1.2V的輸入,目標輸出電壓是1.0V,并且當傳輸100mA時,IQ為0.1mA,那么效率為1/1.2 = 83.3%。如果LDO直接與輸出電壓為3.7V的鋰離子電池連接,在其他條件相同的情況下,效率僅僅為27%。因此,LDO通常只作為第二級電源穩(wěn)壓器使用,前一級由開關(guān)電源實現(xiàn)高效率的功率電壓轉(zhuǎn)換。

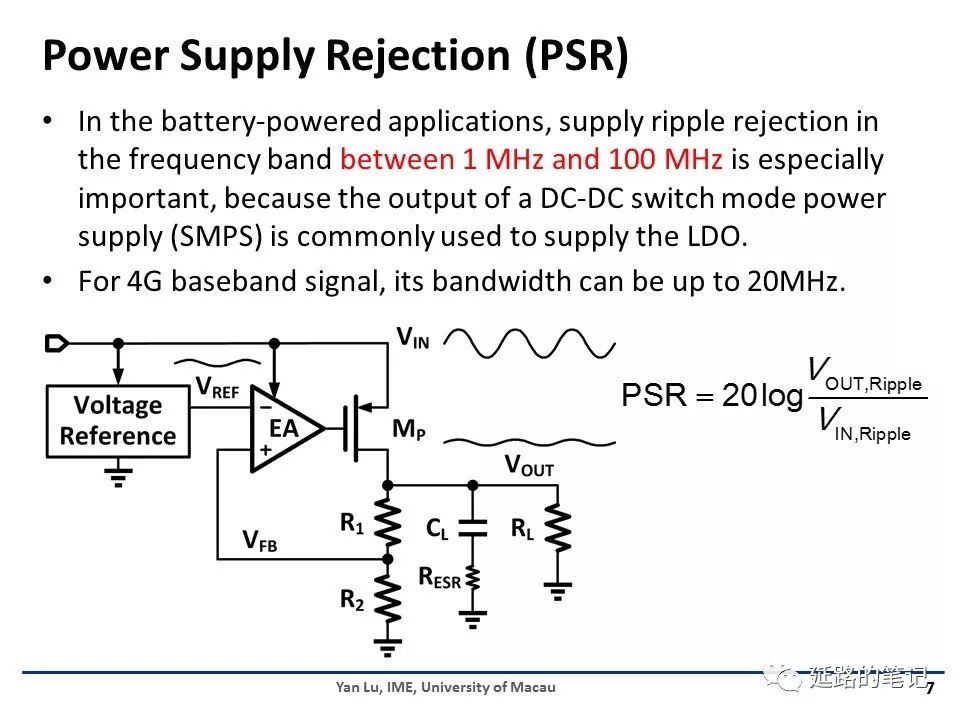

現(xiàn)在我們來看一下電源抑制PSR的概念。PSR的定義為在一定頻率下,輸出紋波電壓和輸入紋波電壓的比值。為了測試PSR,我們可以在不同頻率下在上加入正弦波并觀察衰減的輸出紋波。

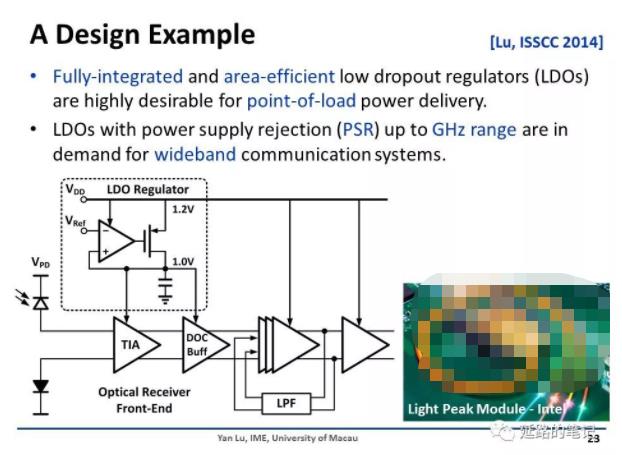

在電池供電的應(yīng)用中,1MHz到100MHz這個頻帶是比較重要的。因為前級的DC-DC轉(zhuǎn)換器工作在此頻率下,并且會產(chǎn)生幾mV到幾十mV的電源紋波。從應(yīng)用的角度看,MHz范圍里的PSR也十分重要。正如在4G的通信系統(tǒng)中,基帶信號的帶寬可以達到20MHz,而在5G系統(tǒng)中,帶寬超過100MHz。

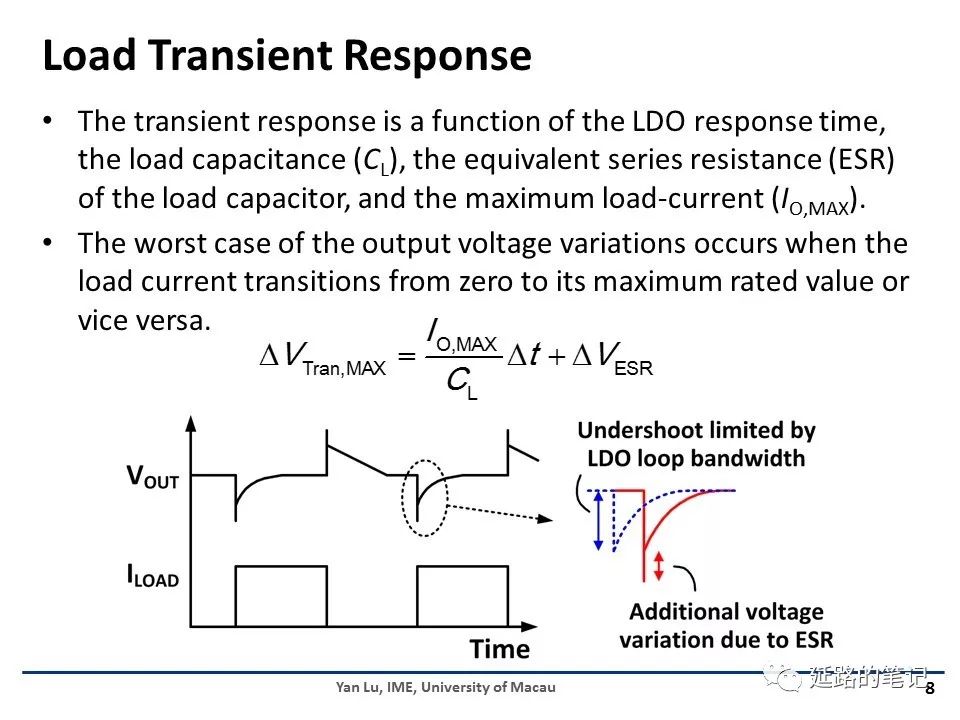

對于負載瞬態(tài)響應(yīng),一般使用輸出電容來提供緩沖電流,以緩解LDO環(huán)路延時。需要注意的是,電容不可避免地存在等效串聯(lián)電阻(ESR)。在古老的設(shè)計中,會添加ESR產(chǎn)生一個左半平面零點來補償次主極點以增加相位裕度。或者,ESR可能來源于布線的寄生電阻。負載瞬變過程中,ESR會提供額外的電壓誤差。比如當負載從高到低發(fā)生瞬變時,在LDO反饋回路響應(yīng)之前,電容會提供絕大部分的輸出電流,而電容電流會在ESR產(chǎn)生一個相反方向的電壓。因此,我們會觀察到額外的負脈沖電壓(紅色部分)。

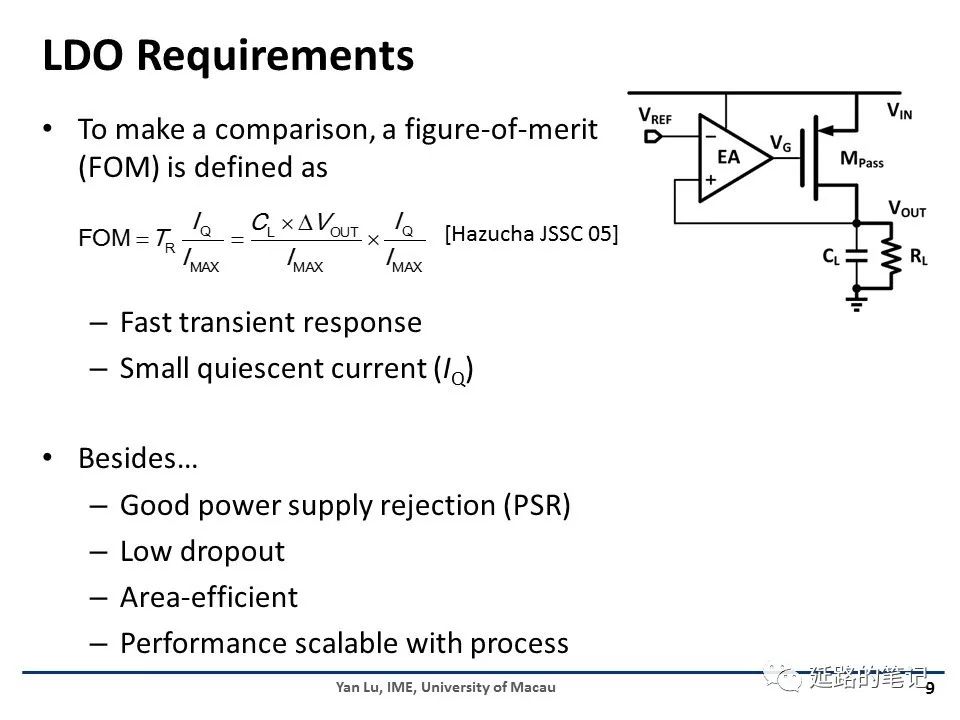

為了比較不同的LDO的性能,英特爾公司的Peter Hazucha提出了一種性能指標FoM。其中,響應(yīng)時間TR等于負載電容乘以ΔVOUT再除以最大輸出電流。為了獲得更好的FoM,我們需要使用更小的IQ來提供更大的最大電流。為此,需要設(shè)計一種低功耗的快速響應(yīng)LDO。很明顯,這是功耗和速度的折中。如果速度不夠,那就只能電容(面積)來湊了。

除了響應(yīng)速度,PSR對于噪聲敏感的模擬和射頻負載來說是一個非常重要的指標。此外,還有幾個考慮因素,比如實現(xiàn)低壓差才能實現(xiàn)高能量效率。同時,全集成LDO需要做到面積優(yōu)化,面積就是成本。并且,其性能相對于工藝制程來說應(yīng)該是要可擴展的,即當我們把同樣的電路結(jié)構(gòu)搬到更先進工藝的情形下時,性能也應(yīng)該要相應(yīng)地變得更好。但這一點并不是所有的LDO設(shè)計都能滿足的,取決于設(shè)計者的思路和采用的架構(gòu)。這個后面還會提到。

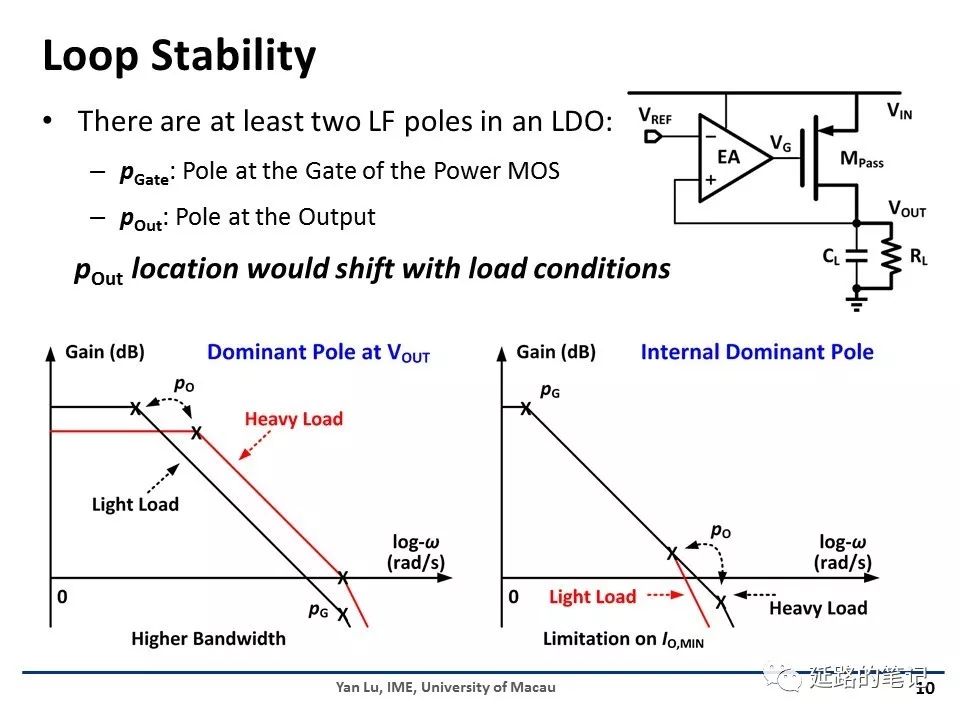

在一個典型的LDO設(shè)計中,LDO會存在至少兩個低頻極點。Power MOS的柵極有很大的RC時間常數(shù),這是因為誤差放大器的輸出電阻和柵極的寄生電容都很大。同時,輸出節(jié)點也有大電容,它來自濾波電容或者負載本身。顯然,由于LDO的負載電阻和導(dǎo)通電阻會隨著輸出電流的改變而改變,輸出極點也會因負載條件的不同而改變。

使LDO反饋回路穩(wěn)定是LDO設(shè)計中最基本的需求。因此,在我們設(shè)計LDO的時候,我們需要想清楚應(yīng)該把LDO的主極點設(shè)計在什么位置。

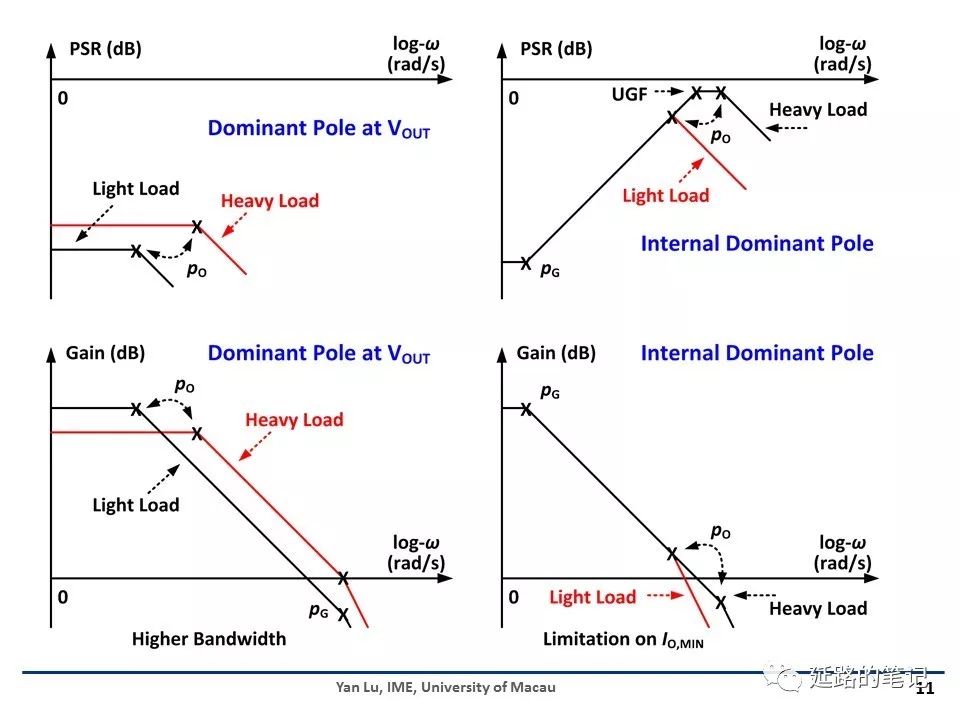

如果我們把主極點設(shè)計在輸出節(jié)點處,當負載較大時,單位增益頻率UGF在重載條件下會增加,因為輸出極點會移到更高的頻率。當單位增益頻率接近第一個非主極點時,環(huán)路的穩(wěn)定性會降低。

另一方面,如果我們把主極點設(shè)計在LDO的內(nèi)部節(jié)點時,需要把內(nèi)部極點設(shè)計在較低的頻率下。這樣在輕載或空載的情況下,輸出幾點會接近主極點,環(huán)路的穩(wěn)定性會受到的限制。

另一方面,如果考慮到PSR的影響,最好把主極點放在輸出節(jié)點。這樣我們可以在輸出節(jié)點處放置一個大電容來濾去電源的紋波。這樣,當頻率高于的頻率時,高頻紋波就會被負載電容濾去。

而在內(nèi)部主極點的情形下,PSR主要由LDO穩(wěn)壓反饋回路決定。當環(huán)路增益減小時,PSR會變得很差。在UGF附近的頻率處,PSR下降到大約0dB,即沒有PSR。

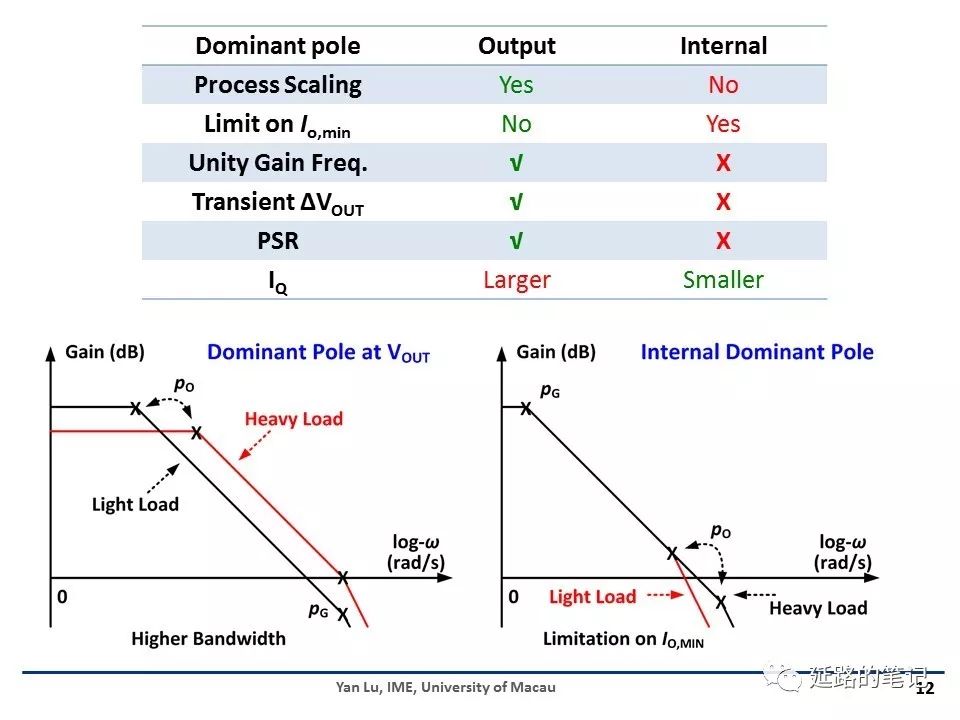

該表總結(jié)了把主極點設(shè)計在輸出節(jié)點和內(nèi)部節(jié)點時的各自優(yōu)缺點。把輸出極點PO作為主極點時,當工藝尺寸變小時,電路性能也會隨之變好,這是因為在更先進的工藝條件下,內(nèi)部極點更容易被推到高頻。而把內(nèi)部極點作為主極點時,即使工藝變得更好,單位增益頻率UGF也難以提升,因為在輕載的情況下,UGF會受到的限制(除非引入其他的零點技術(shù)在補償次極點)。把PO作為主極點的缺點是,需要大電流來驅(qū)動內(nèi)部極點去到高頻,這樣會導(dǎo)致LDO的靜態(tài)電流增加。

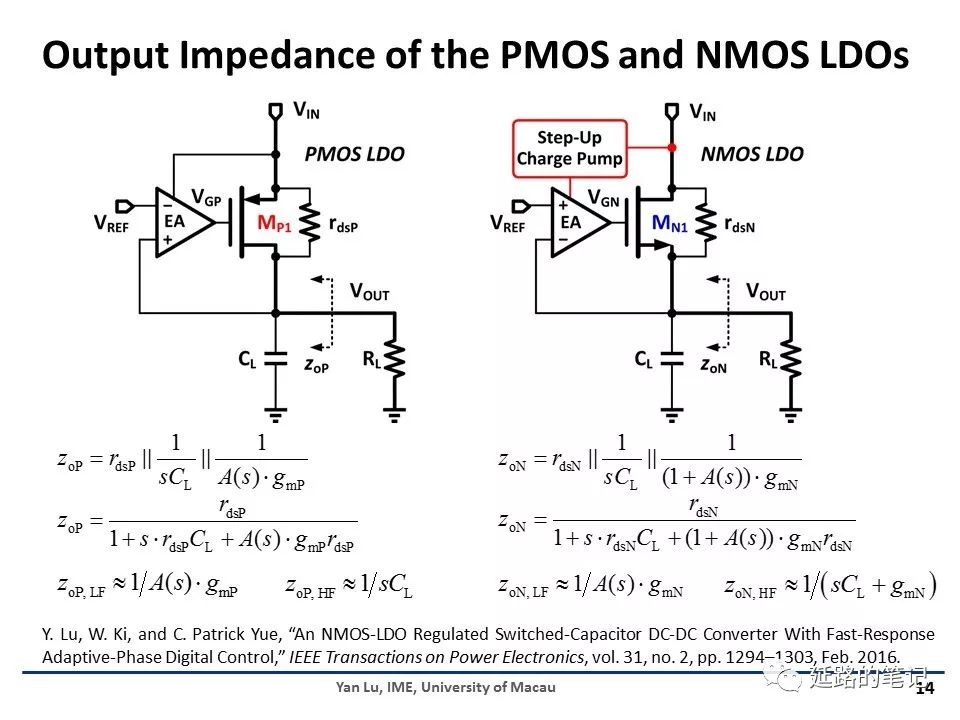

我們可以選擇PMOS或NMOS來作為功率管。顯然,PMOS更容易在低壓下被驅(qū)動,而同樣條件下,NMOS需要更高的電壓來驅(qū)動。為了保持低壓差,一般需要用到升壓電荷泵電路來驅(qū)動NMOS的誤差放大器EA。

就輸出阻抗而言,由于NMOS功率級的一個源級跟隨器,因此它可以提供對負載瞬態(tài)變化的本征響應(yīng)(intrinsic response)。因為在LDO反饋回路響應(yīng)之前,VOUT已下降,那么NMOS功率管的VGS會隨之增加,并因此自動提供更大的輸出電流。因此,在輸出阻抗ZoN的計算中,我們將1/gmN與其他因子并聯(lián),其中g(shù)mN為NMOS功率管的跨導(dǎo)。

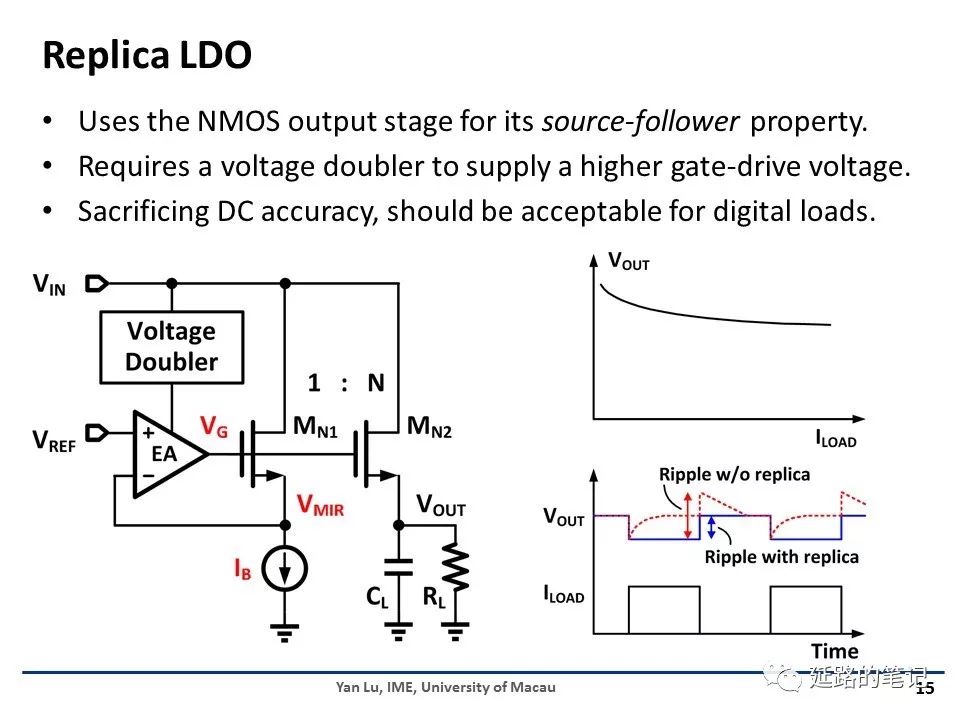

基于NMOS LDO的特性,Replica LDO是一種簡單適用于數(shù)字負載的選擇。在Replica LDO中,MN1和MN2是一對尺寸比為1:N匹配晶體管。如果偏置電流IB和輸出電流之比也為1:N,VOUT則近似等于VMIR,其中VMIR是基準電壓VREF的鏡像電壓。當然,IB和輸出電流不可能完全匹配,所以VOUT會隨著負載電流的變化而變化。如果負載能夠接受電源的變化,比如數(shù)字電路,就問題不大。

另一個好處是,相比于well-regulated情況,VOUT隨負載變化的情況在瞬態(tài)響應(yīng)的時候會實現(xiàn)更小的undershoot和overshoot, 如右下角的圖。

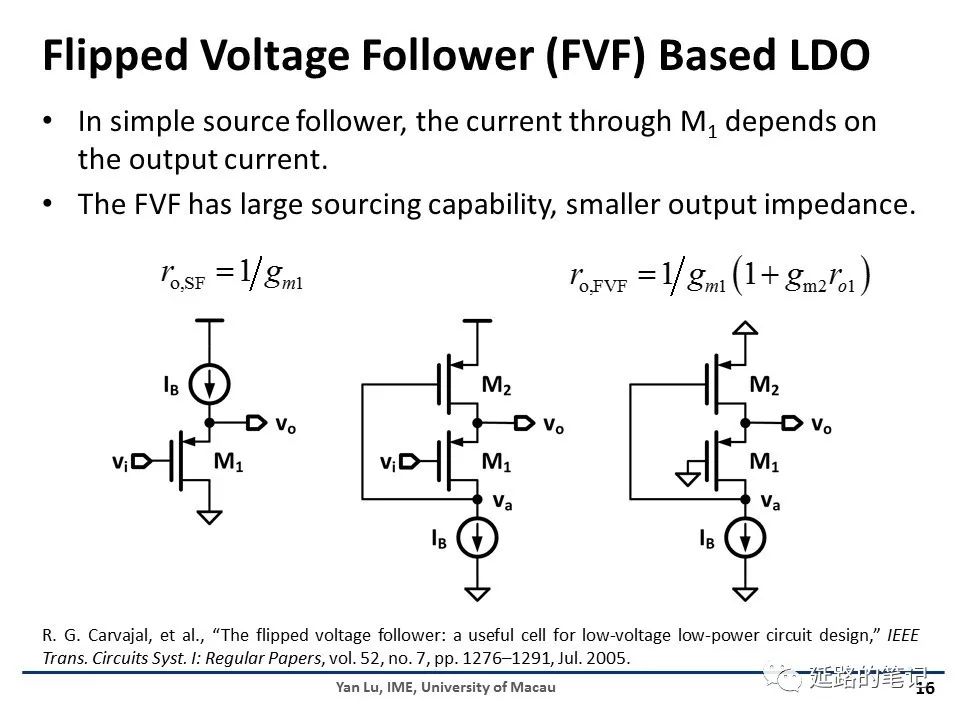

前面講到,Source Follower的輸出阻抗為1/gm。有論文提出了一種新型的源級跟隨器Fliipped-Voltage Follower (FVF)。與普通的源級跟隨器相比,F(xiàn)VF具有更大的輸出電流能力和更小的輸出阻抗。在FVF結(jié)構(gòu)中,M1作為共柵放大級,如果vo發(fā)生一個很小的變化,這一變化將被gm1ro1倍放大到va,并會控制M2的跨導(dǎo)gm2。因此,F(xiàn)VF的輸出阻抗為1/gm1ro1gm2。

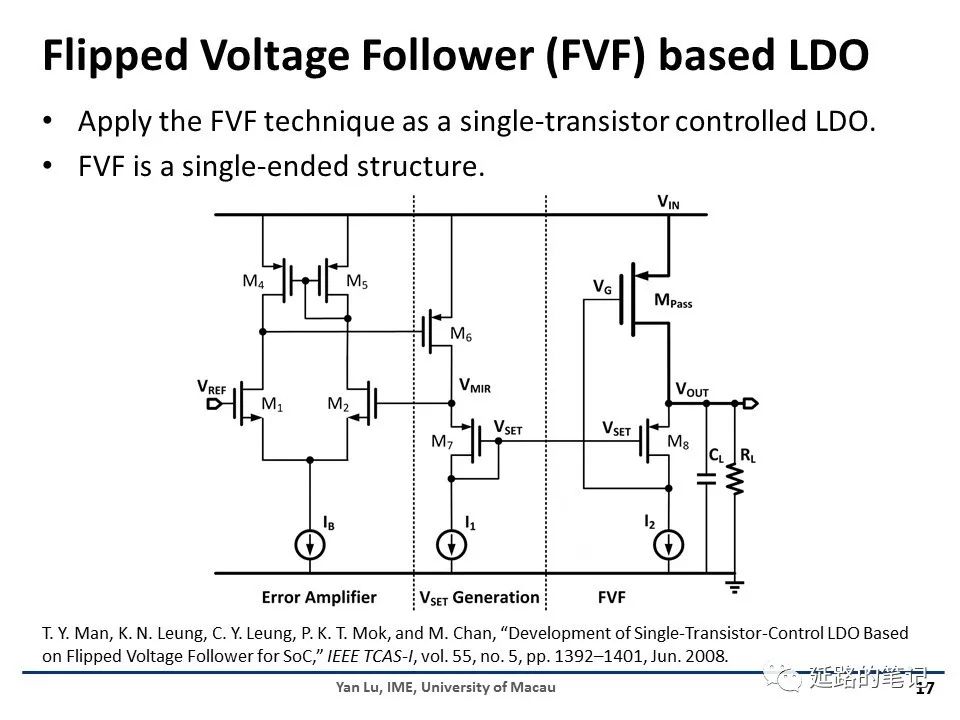

良好的輸出電流的能力使得FVF本身即可作為一個簡單的LDO,其中VSET僅為M8提供直流偏置。當I1和I2,M7和M8大小匹配時,VOUT應(yīng)該近似等于VMIR,其值接近VREF。誤差放大器和VSET電壓偏置僅消耗微小的電流,因為它們僅提供直流偏置電壓。與具有的差分輸入對的傳統(tǒng)LDO相比,F(xiàn)VF是單端結(jié)構(gòu),它的電流利用率相對差分結(jié)構(gòu)更高。因為傳統(tǒng)差分輸入的誤差放大器的一端在LDO里面是恒定接VREF,那一條只支路的電流被浪費了。

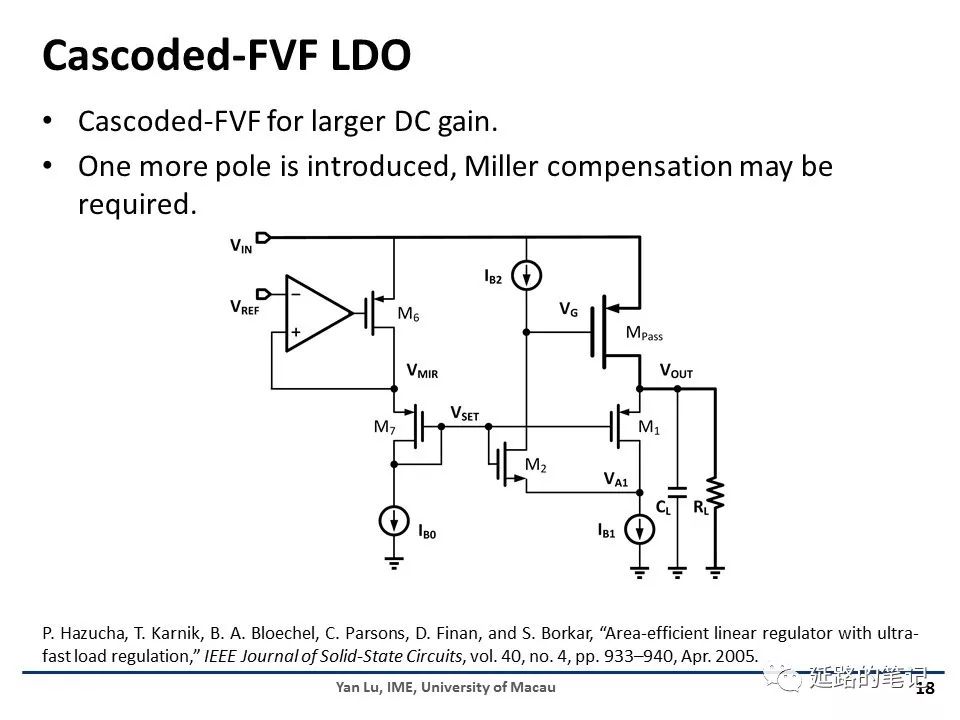

但是,簡單結(jié)構(gòu)的電路只能提供很小的環(huán)路增益,這會導(dǎo)致DC regulation較差。為了達到更大的DC增益,可以使用共源共柵FVF結(jié)構(gòu)。它采用M2作為另一個共柵放大器級。現(xiàn)在,環(huán)路中存在來自于VOUT、VA、VG的三個極點。因此,從穩(wěn)定性角度來考慮,需要采用密勒補償。

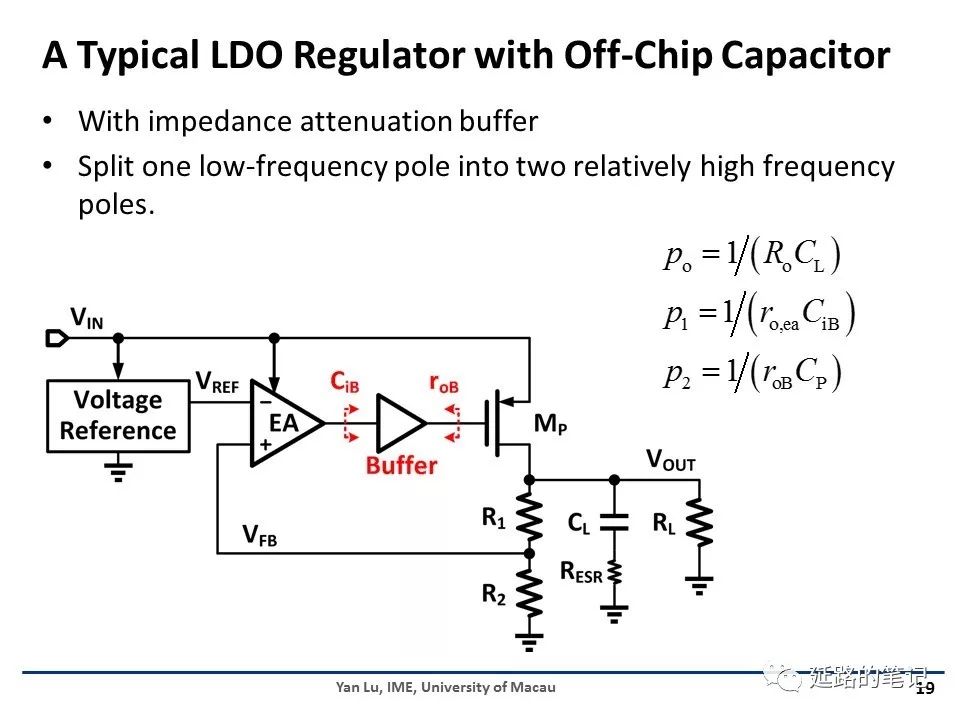

如圖顯示了一種典型的LDO,其帶有片外負載電容和一個內(nèi)插的buffer。片外的大電容使得輸出極點很容易能成為主極點。同時,buffer的輸入電容和輸出阻抗都很小,這樣可以更好地驅(qū)動MOS功率管。因此,buffer的作用是把MOS功率管的一個低頻極點拆分成兩個相對高頻的極點。實現(xiàn)buffer最簡單的方法是使用一個輸出阻抗為1/gm的源跟隨器。但是,如果我們想進一步降低輸出阻抗,只用source follower,需要消耗很大的電流。

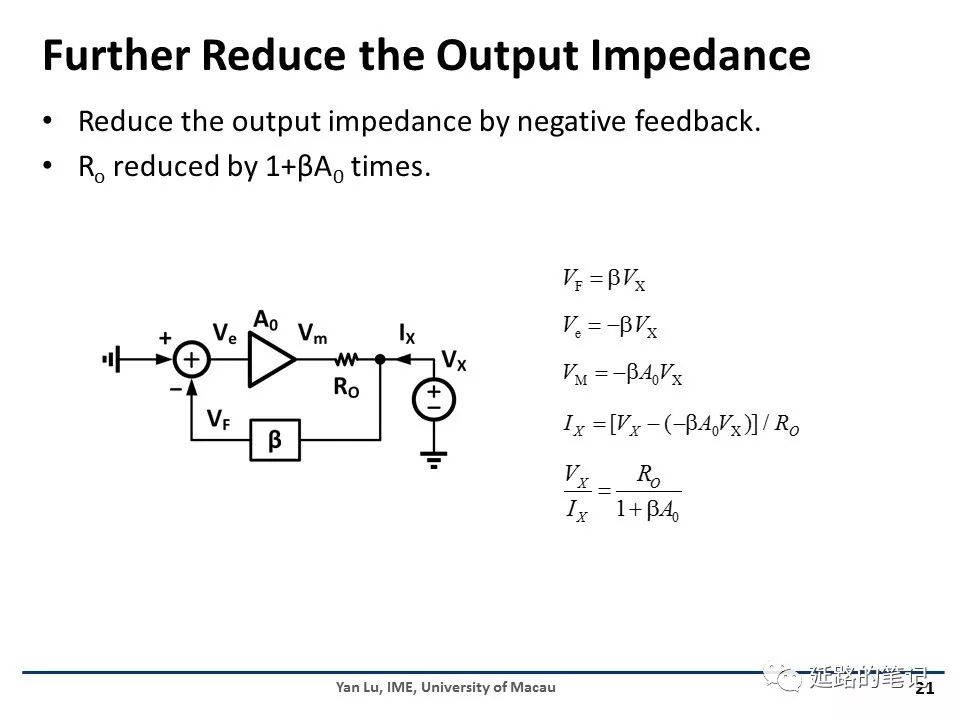

我們可以使用負反饋特性來進一步減小輸出阻抗,而不是簡單地增加source follower的偏置電流。如上圖計算的那樣,如果有一個環(huán)路增益為βA0的負反饋,輸出阻抗可以減小1+βA0倍。

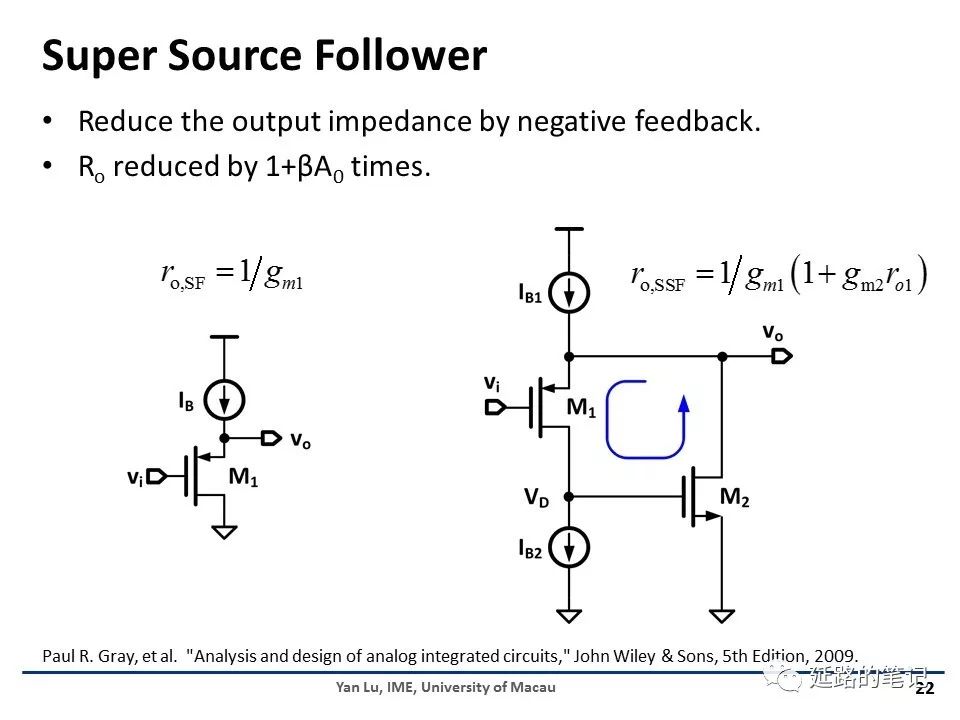

利用負反饋的特性,我們就得到了super source follower (SSF),它增加了一個晶體管M2用于減小輸出阻抗。雖然在SSF中多了一個分支消耗功率,但是DC偏置電流得到了更高效的利用。當輸入減小時,將有更多的動態(tài)電流可以用來下拉緩沖器的輸出。

電子發(fā)燒友App

電子發(fā)燒友App

評論