今天給大家分享的是電源設(shè)計實(shí)例,一步一步教你PCB設(shè)計。

先從交換節(jié)點(diǎn)開始。從那里開始放置輸入電容。然后,輸出電容。接下來是EMI 降低緩沖濾波器,然后是實(shí)際控制 IC 和很容易被忽略的柵極驅(qū)動路徑。最后要放置的組件是信號電平或模擬部分。

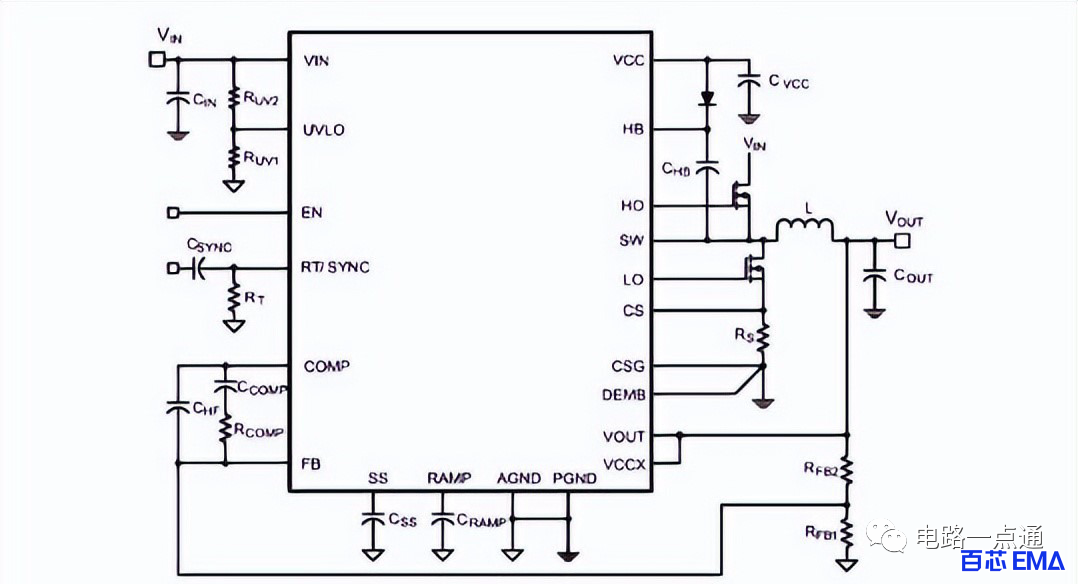

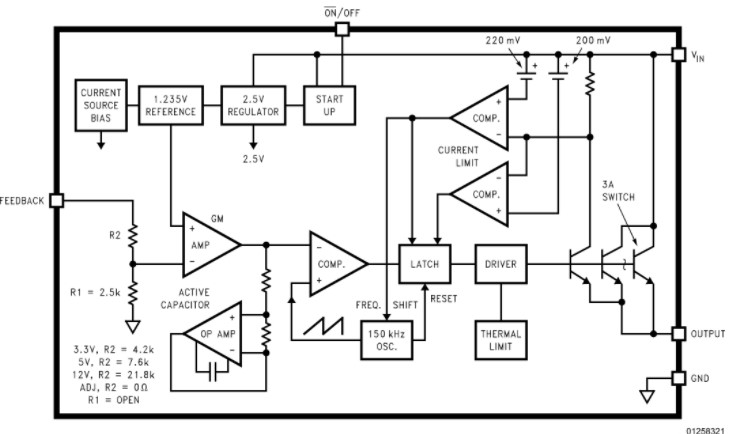

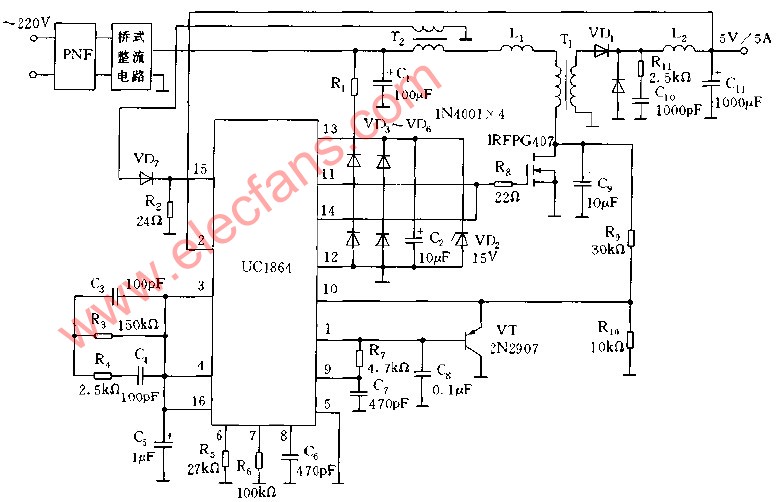

一、典型的同步降壓控制器

典型的同步降壓控制器

上圖為典型的數(shù)據(jù)表首頁示意圖。與大很多理圖一樣,顯示的引腳注釋并不代表實(shí)際的 IC,它是一個 TSSOP-20。所以在看Datasheet的時候,還是要多注意一點(diǎn), 不能只看這一個示意圖。

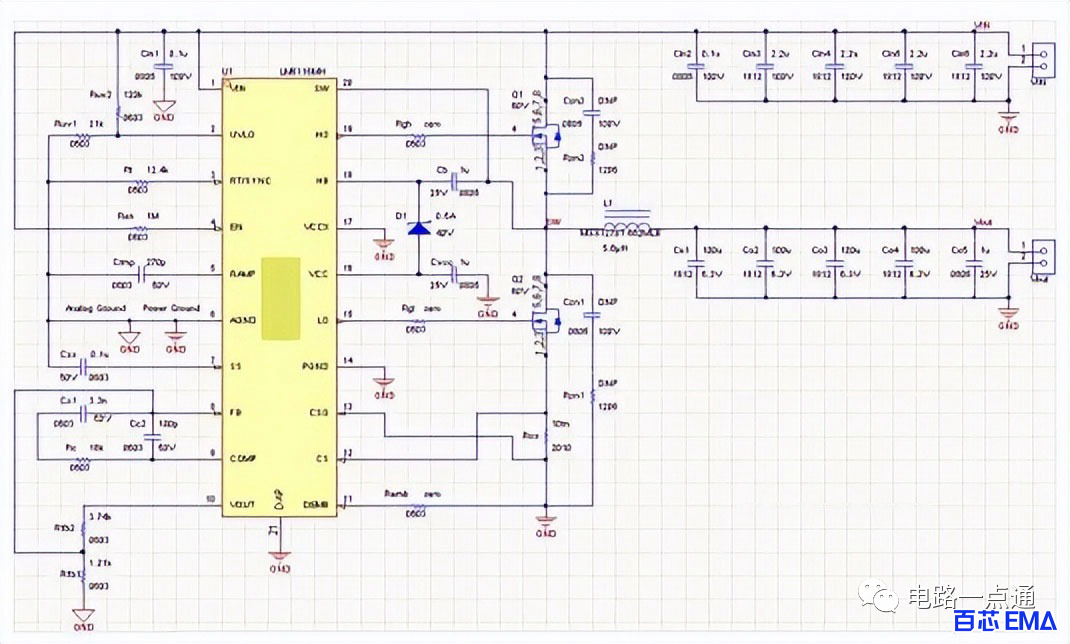

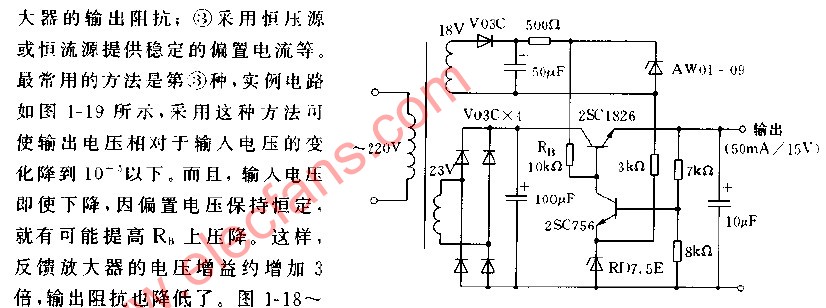

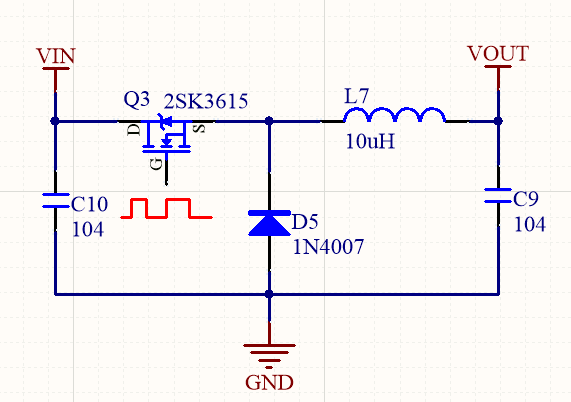

二、實(shí)際同步降壓控制器示意圖

實(shí)際同步降壓控制器示意圖

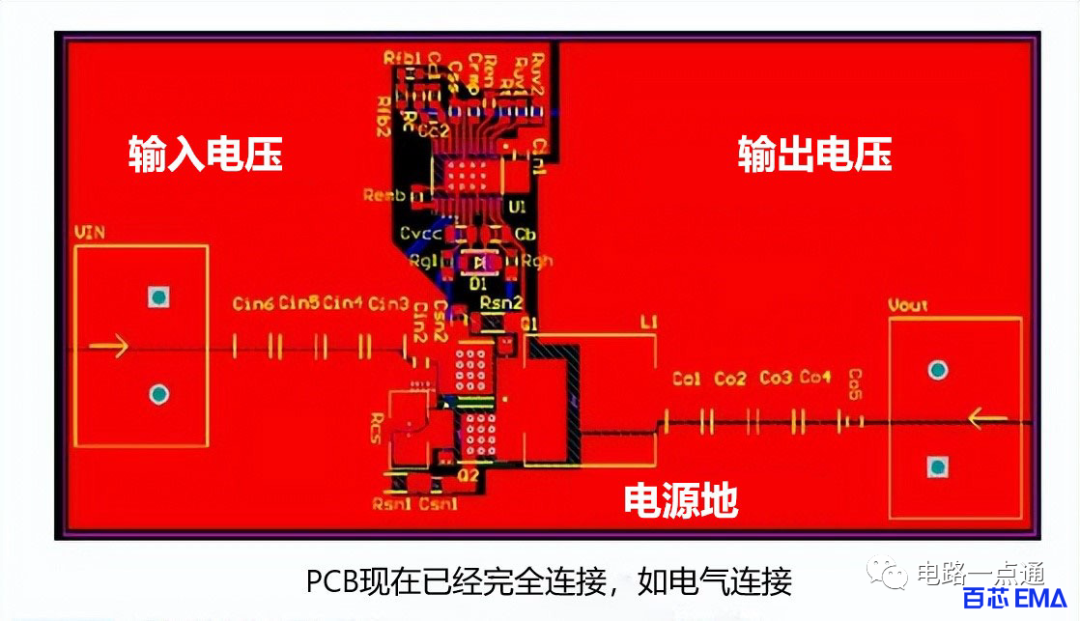

? ?這里可以明顯看到和上面的不一樣了。元件在PCB上的電氣連接方式有許多名稱,不存在標(biāo)準(zhǔn)的一個命名。我一般會先放置開關(guān)節(jié)點(diǎn),通常是電感或者變壓器繞組以及1-2個電源開關(guān),大電阻 RCS 用于檢測電流,它與同步 MOSFET Q2 串聯(lián)。

? ?下面就會分步教大家來設(shè)計PCB。

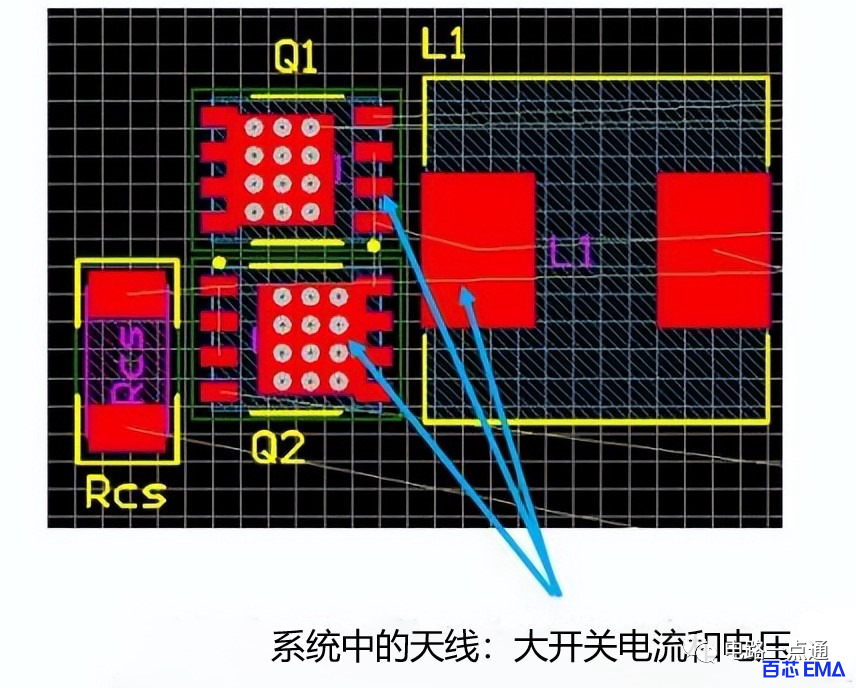

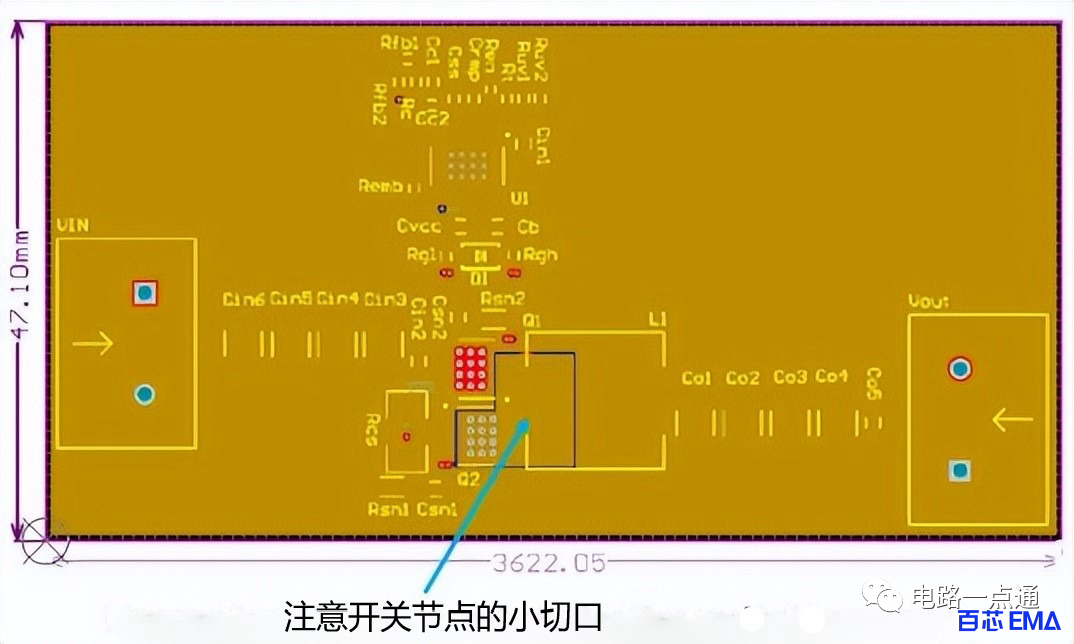

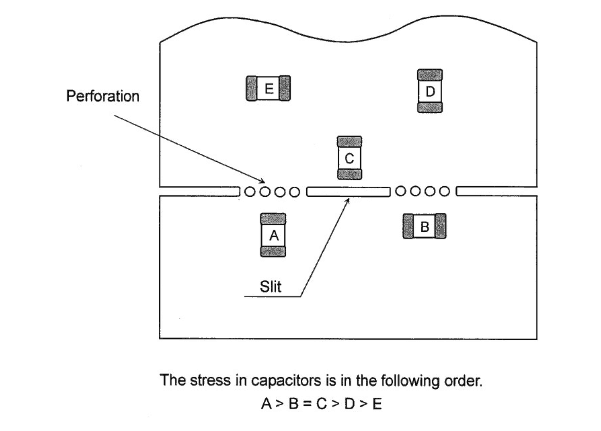

第1步:切換節(jié)點(diǎn)

切換節(jié)點(diǎn)

? ?開關(guān)節(jié)點(diǎn)是一個很好的靜電輻射器,因?yàn)樗蚤_關(guān)頻率在 B 和地之間擺動。位移電流流動,對自由空間中開關(guān)節(jié)點(diǎn)和接地平面之間的電容進(jìn)行充電和放電。一般來說,如果這個節(jié)點(diǎn)的面積最小化會更好。

? ?我一般從構(gòu)成開關(guān)節(jié)點(diǎn)的功率開關(guān)二極管和電感開始,放置在使它們的路徑盡可能靠近的位置。然后,放置了一個剛好覆蓋所有三個路徑的實(shí)體形狀。

? ?對于除降壓穩(wěn)壓器以外的其他穩(wěn)壓器,通過查看高電位擺動的任何節(jié)點(diǎn),尋找方法來最大限度地減少對世界其他地方的電容。在許多類型中,如反激式或 SEPICS,將有兩個開關(guān)節(jié)點(diǎn),每個開關(guān)節(jié)點(diǎn)都需要得到處理。

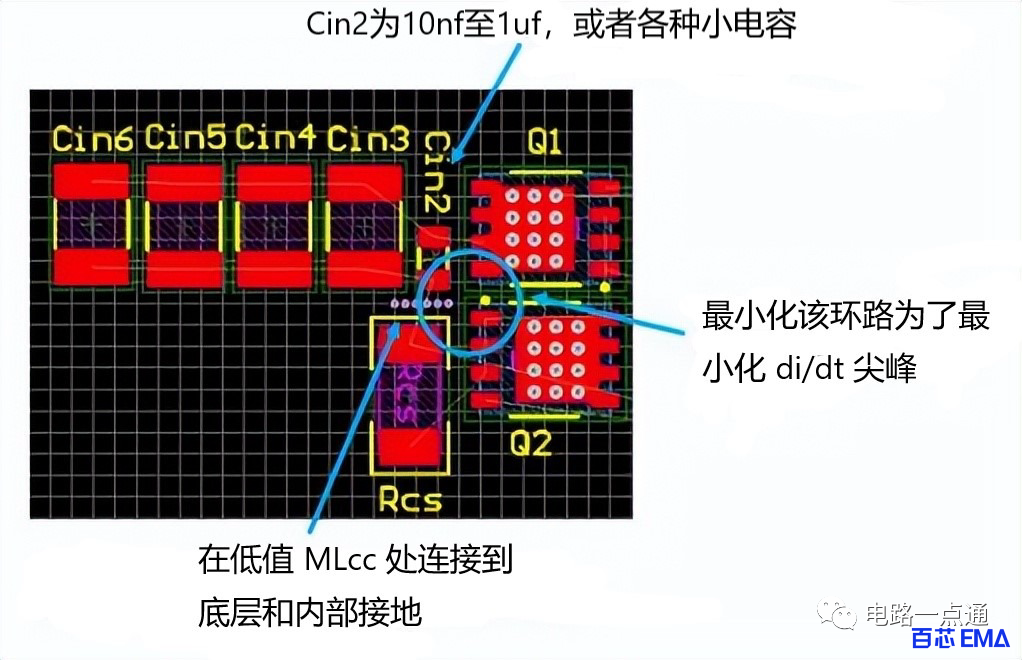

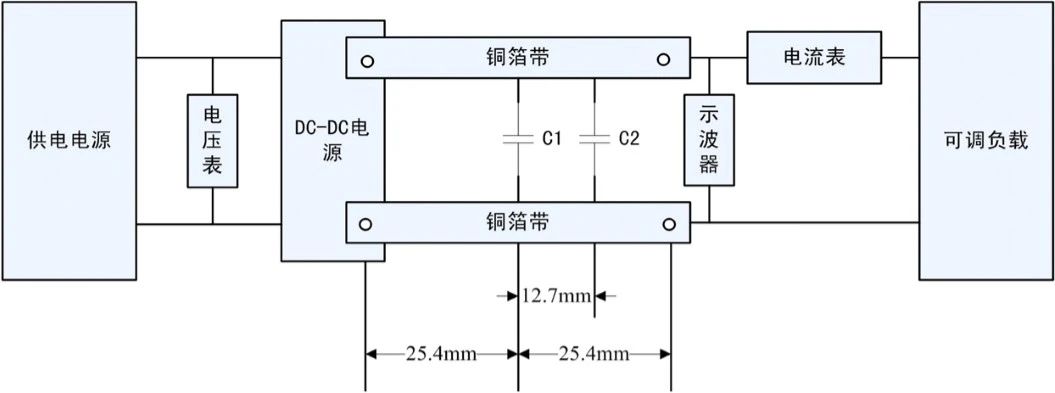

第 2 步:輸入電容組

輸入電容組

? ?輸入電容、高側(cè) FET 和低側(cè) FET 之間的環(huán)路需要最小化,這是 Buck 設(shè)計中最關(guān)鍵的路徑。這里一定要最大限度地減少輸出尖峰。并且一定要使用大銅多邊形作為與 MOSFET 的主電源連接,這在電氣上和熱學(xué)上都會有幫助(同樣這個方法也適用于過孔。)通常越多越好。

? ?通孔還充當(dāng)電路板背面和內(nèi)層的熱通道。如果可以的話,用焊料填充。雖然在電學(xué)或熱學(xué)方面不如銅好,但焊料比空氣好得多。

? ?那個靠近FET的小電容Cin2,是低值 MLCC,通常為 100 nF,主要是為了在降低最高頻率的噪聲和諧波。低值 MLCC的電容值和物理尺寸都很小,可以最大限度地降低 ESR 和 ESL。在 Cin2 之后,有了更大的 MLCC ,降低了開關(guān)頻率的輸入電壓和電流紋波以及更低的諧波。這個電容可以抑制潛在的振蕩并在瞬變期間維持輸入電壓,不過都是低的開關(guān)頻率事件,因此這個電容可以放的更遠(yuǎn)一點(diǎn)。

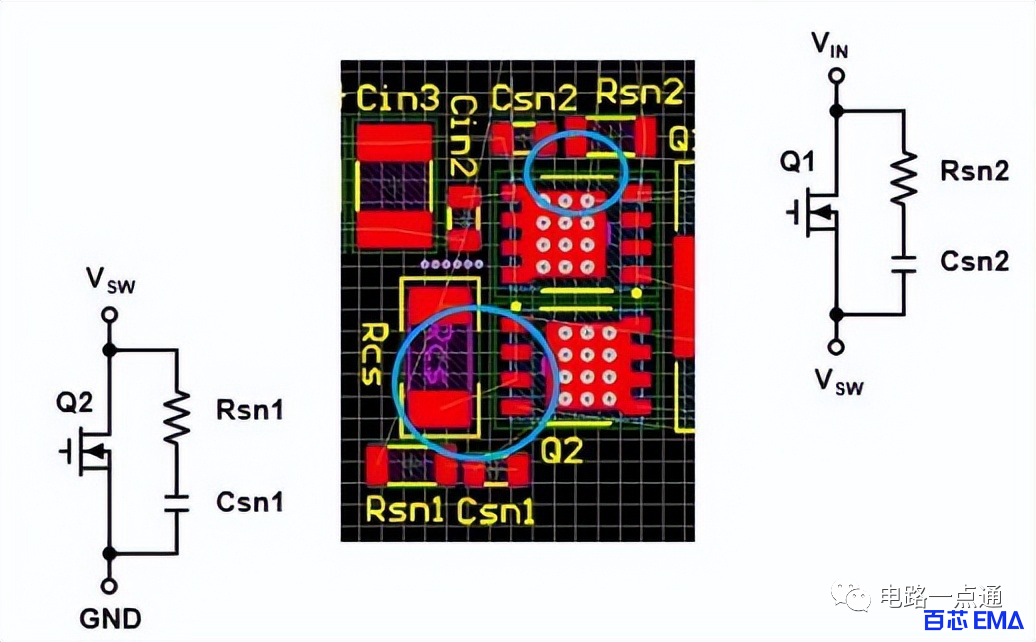

第 3 步:在緊密環(huán)路中獲得緩沖器

在緊密環(huán)路中獲得緩沖器

? ?緩沖器濾波器可以降低高頻噪聲并改善輻射。因?yàn)榫彌_器處理很高的頻率噪聲,通常高于 10 兆赫茲。所以它們得以最小的電感進(jìn)入緊密環(huán)路,不然將無法過濾。

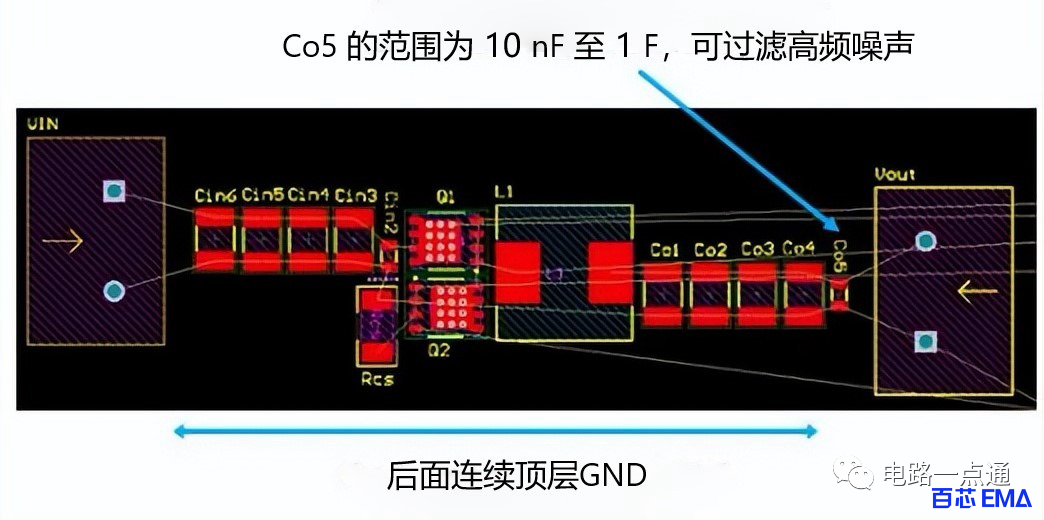

第4步:輸出電容組

輸出電容組

? ?這里必須要注意,在完整的布局之前,我們必須要注意有關(guān)低側(cè) FET、陽極或二極管。這是一個噪聲節(jié)點(diǎn),不應(yīng)直接連接到地平面。這樣做會將噪聲注入地平面。這個就好比一群吵鬧的孩子在寬闊的操場上。

? ?如果你看到降壓穩(wěn)壓器輸出出現(xiàn)尖峰,那么這里連接可能不正確。在理想的設(shè)計中,降壓穩(wěn)壓器的輸出幾乎沒有尖峰。通常,出現(xiàn)在輸出端的任何尖峰都是通過地軌傳導(dǎo)的。

? ?仔細(xì)注意低側(cè)開關(guān)接地之間的路徑,回到輸入電容,輸出尖峰幾乎可以消除,或者至少大大減少。電感將高頻電流和這些元件保持在最低限度。

? ?最小的輸出電容 Co5 恰好靠近輸出連接器或負(fù)載(如果負(fù)載位于同一 PCB 上),以在高頻噪聲干擾負(fù)載之前將其清除。如果高頻噪聲進(jìn)入輸出線束,它會將它們作為天線進(jìn)行輻射。

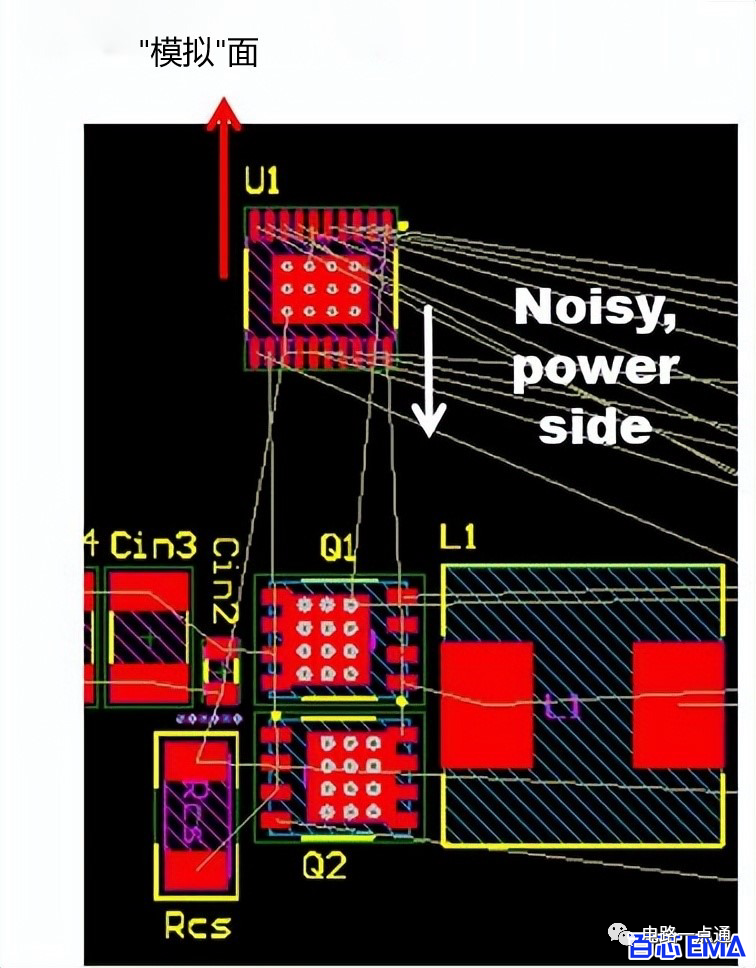

第 5 步:定位 IC

定位 IC

? ?布局良好的IC會將噪聲引腳(如柵極驅(qū)動器)與 IC 一側(cè)的根帶引腳組合在一起。然后,敏感的模擬引腳,如對反饋節(jié)點(diǎn)的控制或軟啟動,則位于另一側(cè)。

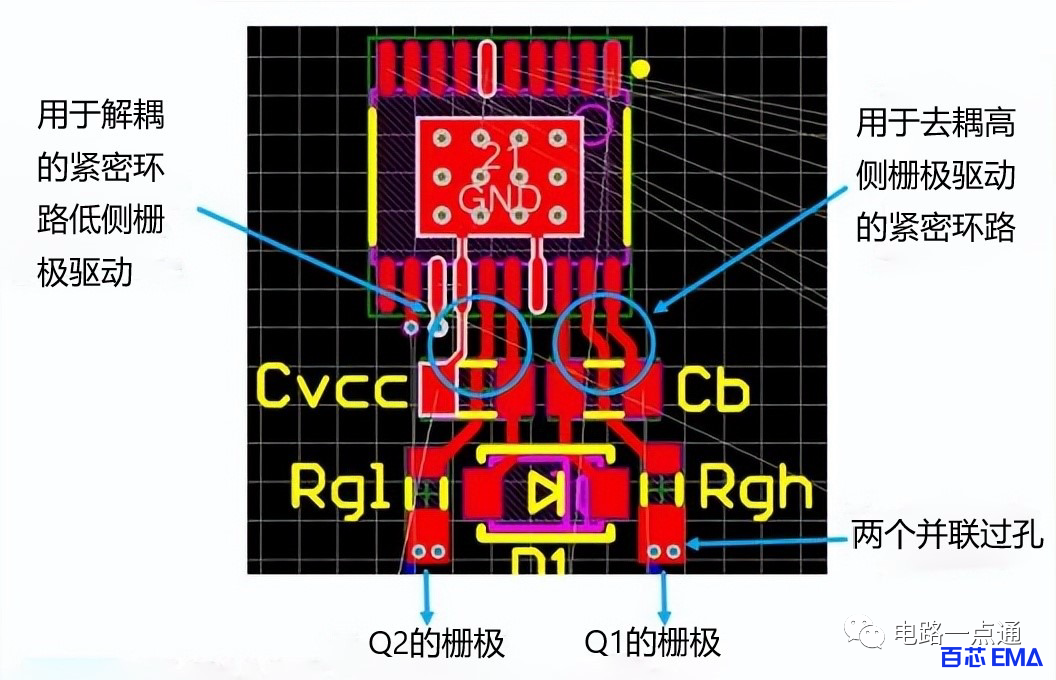

第6步:柵極驅(qū)動電路

柵極驅(qū)動電路

? ?與外部 MOSFET 的柵極連接是非常高的 DIDD 路徑,因此需要仔細(xì)考慮。具有大量柵極電荷的大 FET 會產(chǎn)生數(shù)安培的峰值電流,此處的長連接會顯著減慢 FET 開關(guān)的上升和下降時間。這對于降壓應(yīng)用中的高端 FET 尤為重要,因?yàn)檫^慢的邊沿會增加開關(guān)損耗。

? ?嘗試將柵極到驅(qū)動器的連接直接放在源極到驅(qū)動器的接地連接之上,以盡量減少由此產(chǎn)生的環(huán)路所包圍的面積,并使用至少 0.3 毫米寬的走線。

? ?我通常是通過兩層布線柵極驅(qū)動器,所以我將至少兩個并聯(lián)的過孔防止在該路徑中的寄生電感中。

第7步:完成高端柵極驅(qū)動路徑

完成高端柵極驅(qū)動路徑

? ?有很多設(shè)計在從柵極驅(qū)動引腳到 MOSFET 柵極的短、寬、低電感連接方面做得很好,但它是高側(cè) MOSFET 或低側(cè),返回路徑經(jīng)常被忽略。

? ?對于高端 FET,返回路徑是開關(guān)節(jié)點(diǎn)。出于散熱原因,開關(guān)節(jié)點(diǎn)通常有大量的散熱過孔,可用于將驅(qū)動電流帶回原處。有時,你可以直接在發(fā)送路徑下運(yùn)行返回路徑。由于我是在同一頂層布線,所以我選擇將它們并聯(lián)放置在一起,就像差分對一樣。

? ?通常,還有一個引導(dǎo)程序,是為 n-MOSFET 產(chǎn)生完全驅(qū)動的電荷泵,它的二極管和電容也需要短的、低電導(dǎo)環(huán)路。

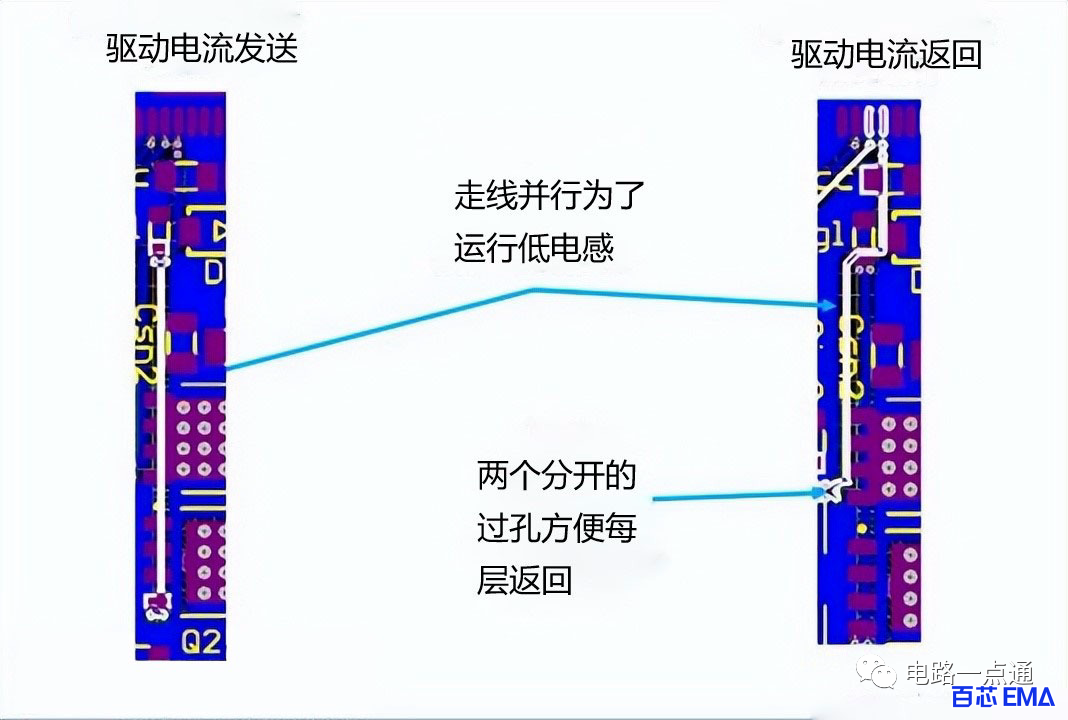

第8步:完整的低側(cè)柵極驅(qū)動路徑

完整的低側(cè)柵極驅(qū)動路徑

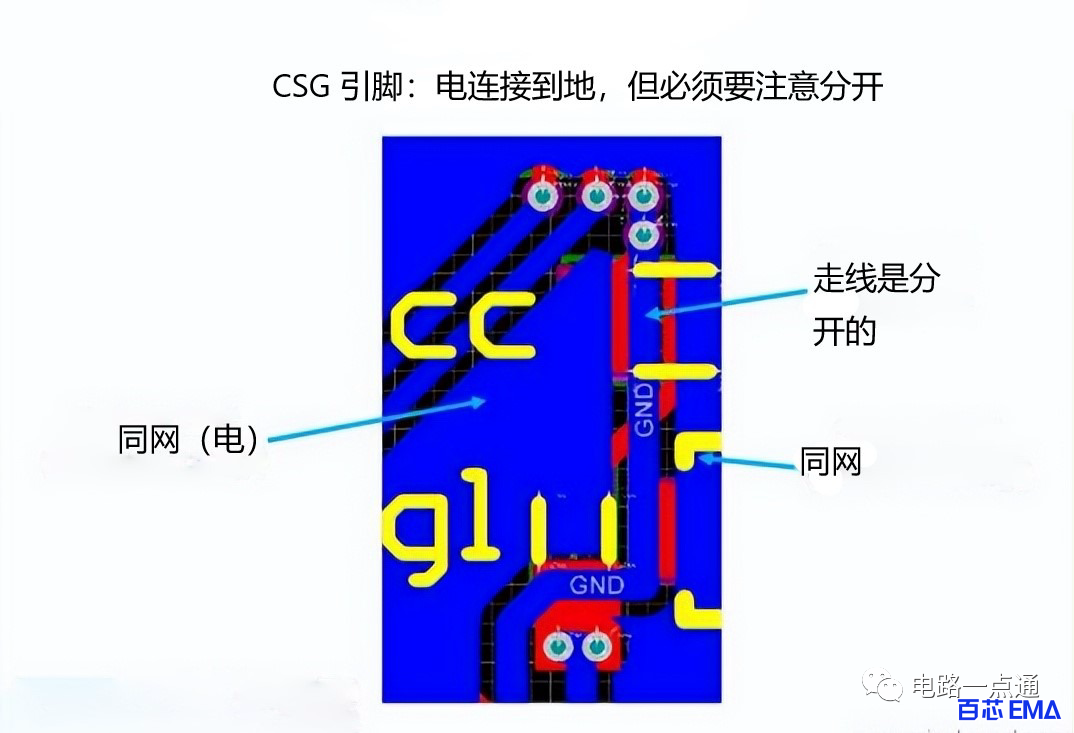

? ?低側(cè)或同步 MOSFET 柵極驅(qū)動的返回路徑通過系統(tǒng)地。這里需要運(yùn)行一個單獨(dú)的跟蹤。為此,許多控制和穩(wěn)壓器 IC 都有專用的接地引腳,通常稱為 P 接地,有時甚至更直接地稱為門回路或類似名稱。所有這些路徑和接地部分之間的物理連接都在 IC 下方。在層間切換時至少使用兩個過孔,并盡可能靠近發(fā)送路徑運(yùn)行這些返回路徑。

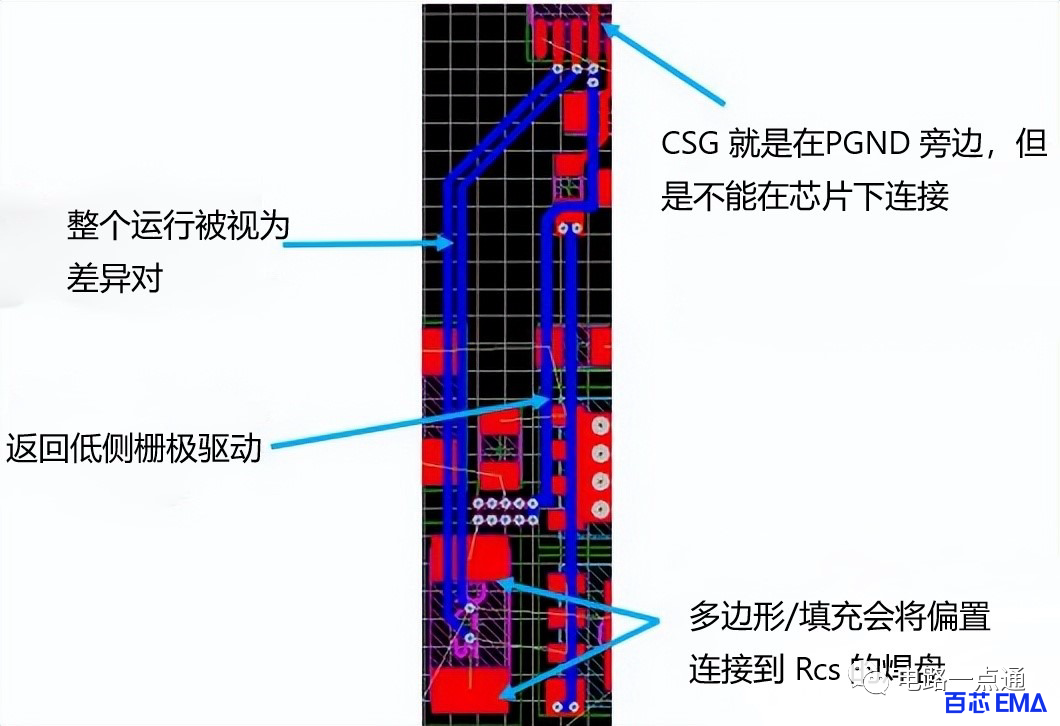

第 9步:差分電流檢測

差分電流檢測

? ?不是每個控制 IC 都有差分感應(yīng)線,你至少得感應(yīng)出一個主電流。還有一個問題,就是弟電流檢測IC的負(fù)極接地。幾乎不可能將差分感應(yīng)線與感應(yīng)電阻布線在同一層,因此它們必須通過過孔。這次不需要并聯(lián)過孔,因?yàn)殡娏髟?a href="http://www.nxhydt.com/tags/ram/" target="_blank">RAM 范圍內(nèi),但是任何實(shí)心接地層都會連接到該負(fù)側(cè)過孔,同時會導(dǎo)致你PCB走線短路。

? ?通常需要將控制器 IC 的 A 地和 P 地連接起來,即模擬地和電源地,有時稱為信號地和電源地,或簡稱為信號地和地。

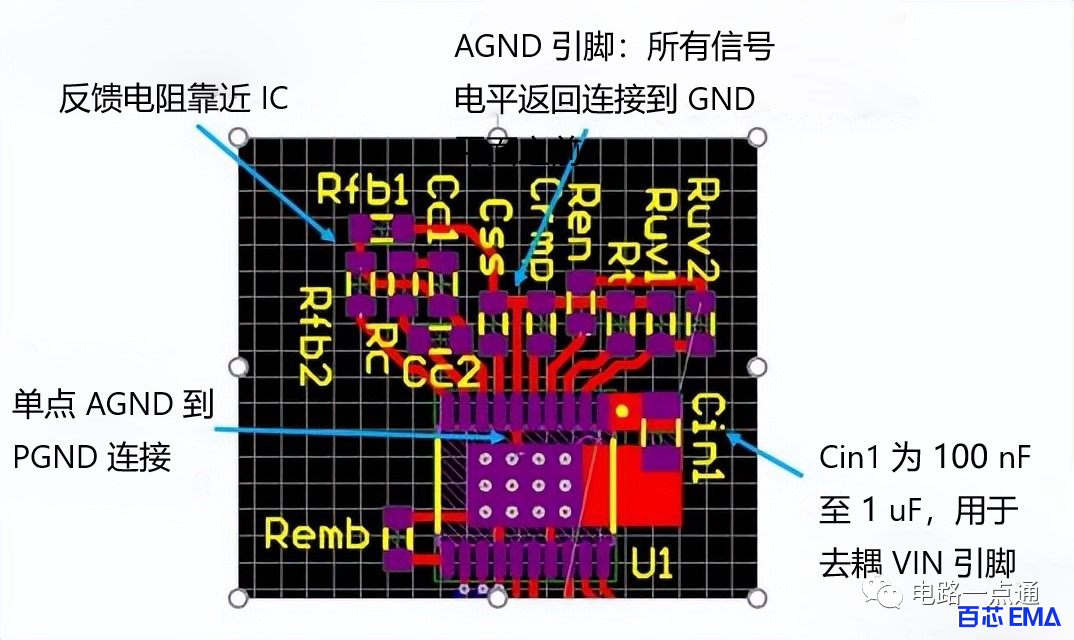

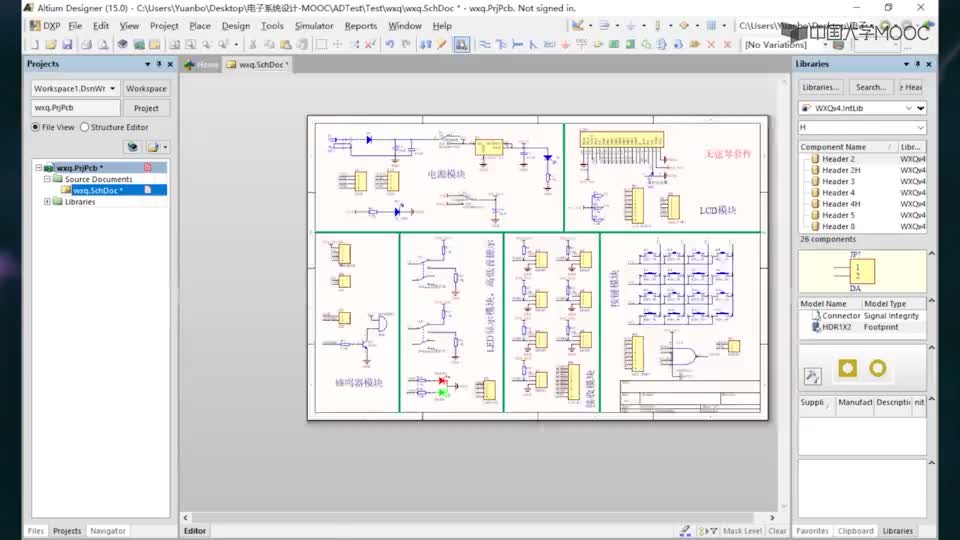

第 10步:放置低功率組件

放置低功率組件

? ?如果你有專門的頂部接地形狀的空間,你可以將其用作所有接地參考控制電路、反饋分壓器、軟啟動和控制環(huán)路的返回。如果這樣的形狀不適合,可以使用菊花鏈從 AGND 引腳連接到各種小信號接地的走線。如果你想通過多層布線此走線,則布局軟件會出現(xiàn)問題,因?yàn)樗胍獙⑦^孔連接到內(nèi)部接地層。而且會引出想要隔離這條痕跡的全部要點(diǎn)。所以,我建議把它放在頂層。

? ?一種方法是提出一個單獨(dú)的 AGND 符號。你通過多層將所有信號接地點(diǎn)連接在一起,而無需連接到內(nèi)部平面。但是當(dāng)連接 AGND 和 PGND,或 AGND 和 PGND 網(wǎng)絡(luò)時,很可能會產(chǎn)生 DRC 錯誤。

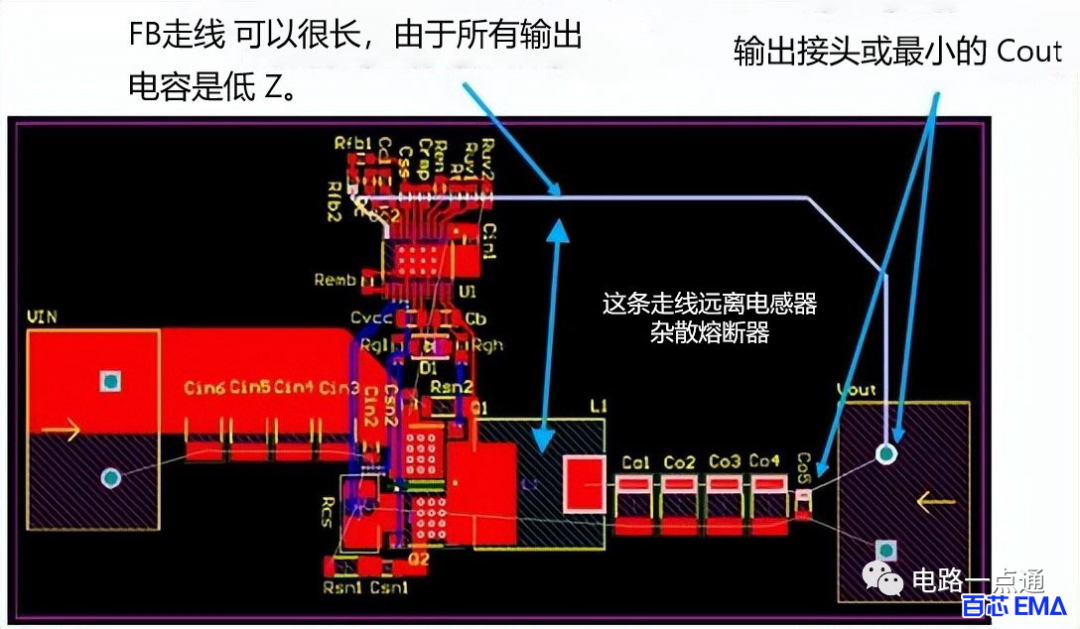

第 11 步:反饋跟蹤

反饋跟蹤

? ?保持最高阻抗走線較短,因?yàn)樗鼈冏钣锌赡苁叭‰s散場。因此,例如,反饋分壓器中的兩個電阻應(yīng)位于非常靠近穩(wěn)壓器反饋引腳的位置,而不是電源輸出附近。從分壓器頂部到電源輸出的連接是 Vout,這是一個非常低的阻抗連接,因此不會受到噪聲拾取的影響。相反,放大器輸入是一個非常高的阻抗輸入,并且非常容易受到雜散場感應(yīng)噪聲的影響。

? ?有一種趨勢是想讓敏感節(jié)點(diǎn)變大,還錯誤地認(rèn)為這種方法可以提供一些屏蔽的效果,但實(shí)際情況正好是相反的。不僅增加了自由空間的電容,并增加了噪聲拾取的可能性。使敏感走線變窄并盡可能短。

第12步:用銅淹沒未使用的區(qū)域

用銅淹沒未使用的區(qū)域

? ?淹沒未使用的 PCB 區(qū)域的技巧是確保連接到安靜的節(jié)點(diǎn)。

第13步:重新審視切換節(jié)點(diǎn)

重新審視切換節(jié)點(diǎn)

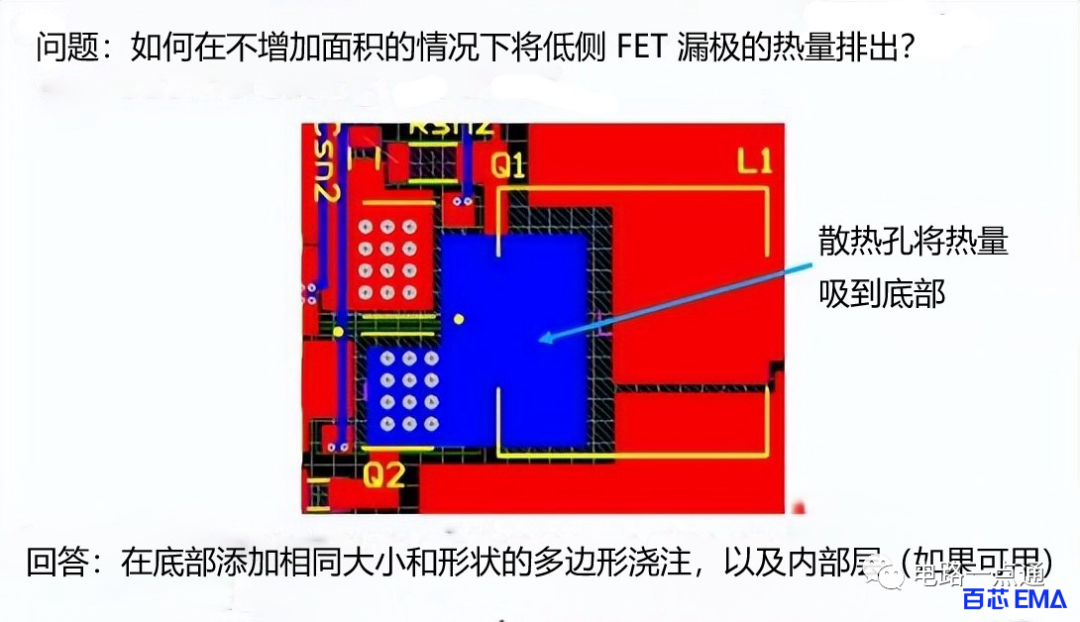

? ?開關(guān)節(jié)點(diǎn)非常重要,我們在底層的首要任務(wù)是審查熱管理和電氣噪聲之間的這一關(guān)鍵.特別是,低側(cè) MOSFET 依靠一些單體銅掩膜來保持冷卻,因?yàn)樗穆O連接到開關(guān)節(jié)點(diǎn),而 MOSFET 的大部分熱量都從漏極散發(fā)出來。這個封裝的占位面積是一個熱增強(qiáng)型 SO8,內(nèi)置 12 個熱過孔。這里可以在底層放置一個多邊形,其形狀和大小與頂層多邊形相同,剛剛覆蓋電感焊盤和兩個 MOSFET 的那個。良好的熱通孔矩陣將有助于將熱量吸收到底層。即使在沒有主動冷卻的設(shè)計中,對流也很可能使一些空氣穿過 PCB 底部。

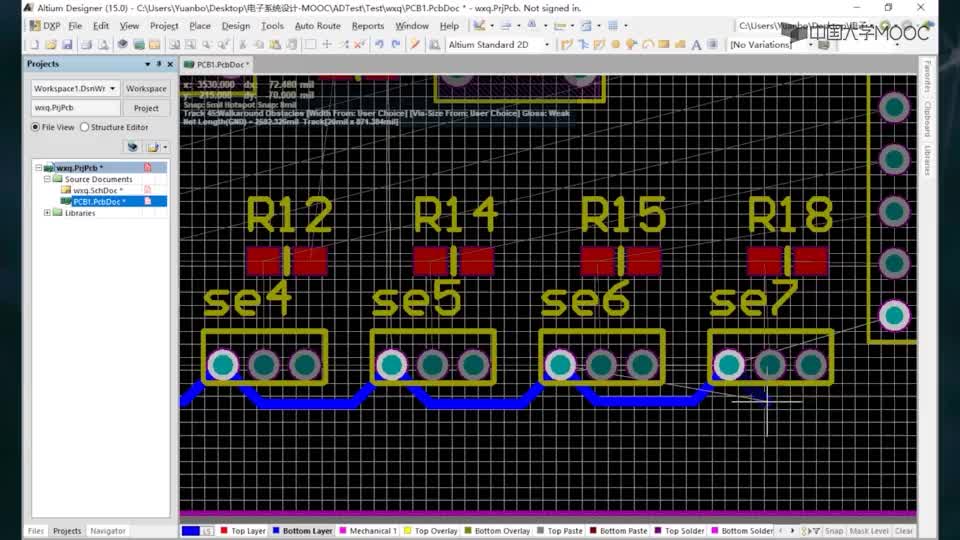

第14步:關(guān)于散熱孔

散熱孔

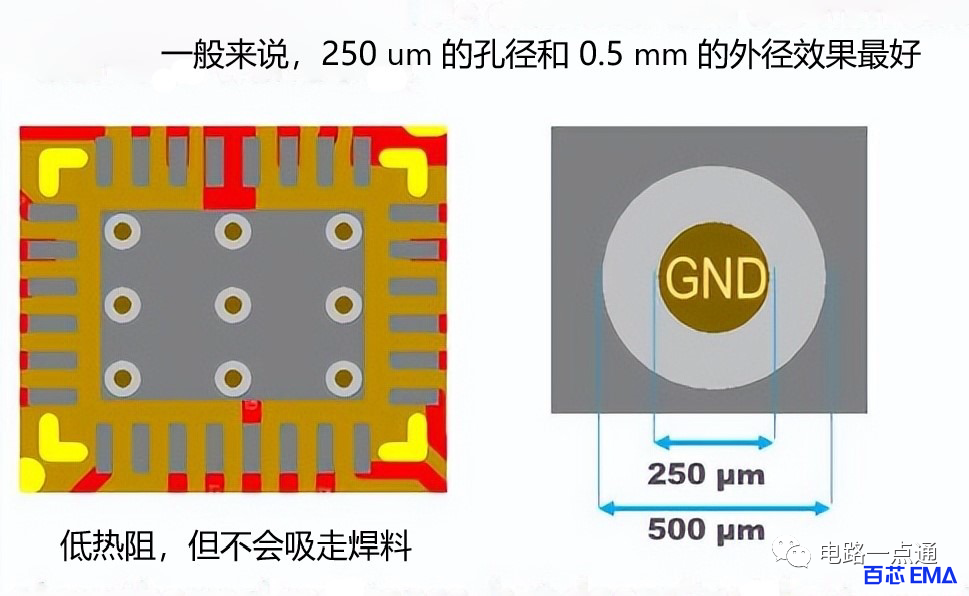

? ?這是一個PCB 封裝,帶有一個大散熱片。當(dāng)直接放置在熱源下方時,熱通孔效果最佳。但同樣,這需要與 PCB 制造商進(jìn)行良好的溝通。我的個人經(jīng)驗(yàn)是 0.25 毫米的孔與 0.5 毫米的外徑相結(jié)合,是一個很好的方案。這些尺寸孔偏小,無法吸走太多焊料,但又不算微孔,鉆孔成本更高。我通常將它們隔開 1 毫米或 1.5 毫米。

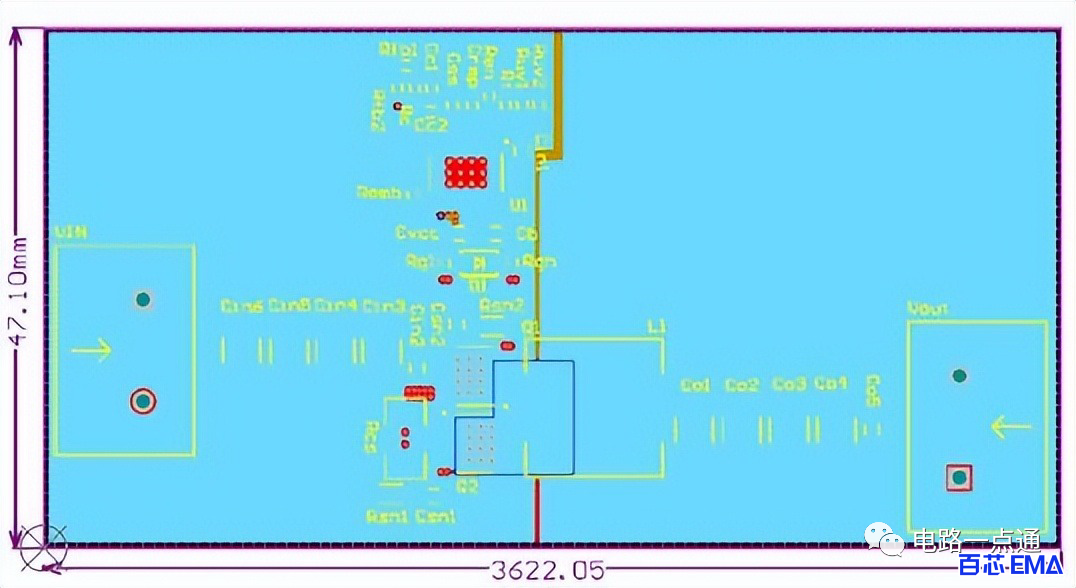

第 15步:用 GND 淹沒底部

用 GND 淹沒底部

? ?在設(shè)計完成前關(guān)閉除接地層之外的所有層是一個非常好的技巧,并確保在完成所有信號和電源線走線的鋪設(shè)后仍然具有良好的接地平面完整性。在許多情況下,過孔是不可避免的,但如果可能的話,應(yīng)避免將其作為電源路徑中的載流元件。只有當(dāng)它們可以用于在設(shè)計中引入冗余銅區(qū)域時,才是比較可靠的。例如與外部走線區(qū)域平行連接的內(nèi)層。過孔被用作熱管,因?yàn)樗鼈兡軌驅(qū)㈨敳慨a(chǎn)生的熱量傳導(dǎo)到 PCB 的背面。可以連接到熱平面區(qū)域的過孔越多,可以實(shí)現(xiàn)的散熱就越多。

? ?使用大量熱過孔時需要注意的一點(diǎn)是,內(nèi)部接地層可能會被嚴(yán)重切斷,最終幾乎沒有有用的電流路徑。這特別有可能發(fā)生在非常小的電路板上,例如穩(wěn)壓器模塊。

第16步:回顧檢查

回顧檢查

? ?許多電路都有接地連接,當(dāng)某個區(qū)域被淹沒時不應(yīng)將其短路。通常可以防止這種情況發(fā)生,建議手動布局。接地區(qū)域(這個三角形)與低側(cè) FET 柵極驅(qū)動的返回路徑以及差分電流檢測線的負(fù)連接保持分離。

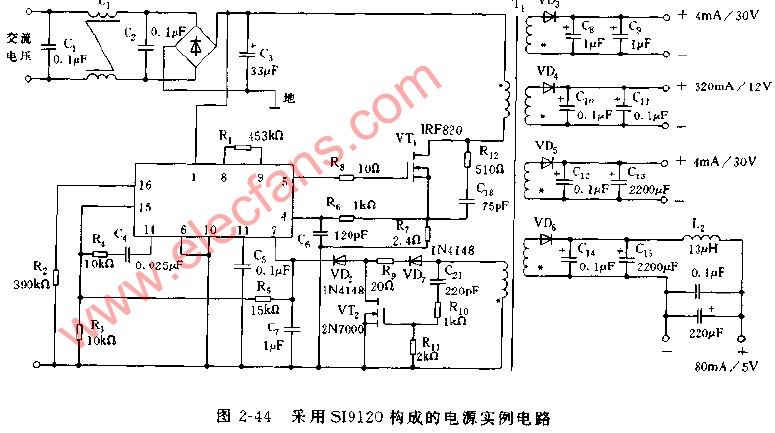

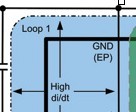

三、四層 PCB – 如何處理?

4層PCB

? ?上圖顯示了4層PCB。雖然有4層,但我還是連接頂層的所有電源焊盤,并用接地、VIN 和 Vout 的銅澆注淹沒任何未使用的區(qū)域。然后,我在第二層上放置了一個實(shí)心地平面,就在頂層下方。第三層我在 VIN 和 Vout 之間分開,但有時我會在這一層放置信號層走線。第四層保留為地面,很多信號電平連接都在這一層。這樣做是因?yàn)槿绻@些連接位于內(nèi)部層上,則調(diào)試電路會變得很難。

1、內(nèi)部平面/第 1 層應(yīng)為 GND

內(nèi)部平面/第 1 層應(yīng)為 GND

? ?稍微靠近頂層會增加注入頂層的 VIN 和 Vout 多邊形中第二層地之間的電容。這些小電容非常適合過濾高頻噪聲,因?yàn)樗鼈兺ǔT?100 pF 到 1nF 的范圍內(nèi)。但如果是開關(guān)節(jié)點(diǎn),我就會考慮打亂我的第二層地平面。

2、VIN 和 Vout 的內(nèi)部平面/第 2 層

VIN 和 Vout 的內(nèi)部平面/第 2 層

? ?與底層一樣,我放置了一個與頂層和底層相同大小的形狀,并用大量的散熱孔連接它。其他所有東西都是接地的,只被信號跡線或熱管理的過孔分開。添加這些大的連續(xù)形狀會增加更多的自由容量,無論是在左側(cè)的 VIN還是在右側(cè)的之間。它們還有助于傳播和散熱。開關(guān)節(jié)點(diǎn)的切口有助于從高側(cè) FET 和漏極排出熱量,而不會讓噪聲以電容方式耦合到其他平面。

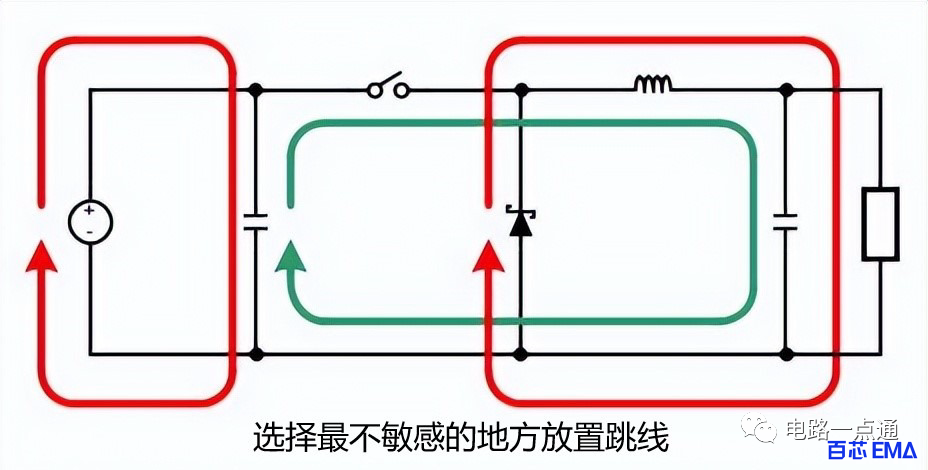

四、單面布局

單面布局

? ?單面 PCB 在成本有限的 AC 到 DC 穩(wěn)壓器中非常常見。比如你的手機(jī)充電器。但金屬芯 PCB 或 MCPCB 成本的快速下降意味著越來越多的 LED 驅(qū)動電路與 LED 一起直接放置在 MCPCB 上。單層 MCPCB 成本的暴跌也導(dǎo)致放置在鋁芯多點(diǎn)板上的功率元件數(shù)量增加。這通常意味著在一層中布線所有內(nèi)容,并且通常意味著很少或沒有過孔。

? ?0 歐姆分流器通常用于將一個連接跨接在另一個連接上,但這些會同時增加電阻和電感。所以,回到大開關(guān)電流的分析。避免在這些路徑中放置分流器。基本上,沒有與電源開關(guān)串聯(lián)的分流器,也沒有與陽極或二極管之間的接地連接串聯(lián),

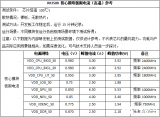

五、元件放置策略——經(jīng)驗(yàn)法則

你可以將電感與電感器串聯(lián),但要在安靜(輸出)端進(jìn)行,而不是噪聲(開關(guān)節(jié)點(diǎn))端

跡線寬度:對于 35 μm 厚度的銅,每安培 0.75 毫米;對于 17.5 μm,每安培 1.5 毫米

每個過孔 1 A 的 DC MAX 是一個很好的設(shè)計目標(biāo)

旁路帽的過孔應(yīng)與焊盤相切,最好每個焊盤兩個

? ?與電感串聯(lián)的走線電感通常不是什么大問題。它只會增加路徑中的總電感。相反,您不想增加與電感器并聯(lián)的大量電容,可能會引起問題。如果你必須添加一些與現(xiàn)有電感器串聯(lián)的電感器,通常最好使輸出路徑更長一些,這樣就可以最大限度地減小噪聲開關(guān)節(jié)點(diǎn)的尺寸。

? ?使用過孔將旁路帽連接到平面,每個焊盤至少需要一個連接切線的過孔,每個焊盤兩個更好,三個稍微好一點(diǎn)。

? ?整個電路板布局經(jīng)常被提到的最小化雜散電感,將每個高 DIDT 路徑視為高頻 RF 連接,快速邊緣將具有數(shù)十兆赫茲的頻率分量,可能達(dá)到兆赫茲,布局時永遠(yuǎn)不要忘記這一點(diǎn)。

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評論