邏輯分析儀測試在基于FPGA的LCD顯示控制中的應用

摘要:邏輯分析儀作為基礎儀器,應該在基礎數字電路教學中得到廣泛應用。本文介紹了基于FPGA的液晶顯示控制設計方案,通過使用OLA2032B邏輯分析儀,對控制線進行監測與分析,保證設計方案的準確性,或者在設計出現問題時,快速定位和解決問題。結果表明,邏輯分析儀在數字電路的設計、調試和分析中,起著很重要的作用。

關鍵字:LCD;邏輯分析儀;總線分析;觸發

一、引言

邏輯分析儀是數字設計驗證與調試過程中公認最出色的工具,它能夠檢驗數字電路是否正常工作,并幫助用戶查找并排除故障。邏輯分析儀的主要特點是能夠同時觀察多個信號;能夠按高低電平、升降沿等模式觸發多條信號線,并查看結果。在基礎教學實驗室中,邏輯分析儀應該與示波器處于同等重要的地位,但示波器的身影隨處可見,邏輯分析儀多數是紙上談兵,而且隨著很多仿真軟件的成熟,設計人員在計算機上便可以觀察被控器件的輸出信號,這樣在教學實驗室中,就回避了價格昂貴、操作繁瑣、不易維修的邏輯分析儀,但軟件仿真與硬件輸出有時會有一定的差距,這就會造成設計結果與我們預想的結果不同,而且很難查找其原因,這就需要我們觀察硬件電路輸出的控制信號。本文針對邏輯分析儀的使用,主要介紹了OLA2032B獨立臺式邏輯分析儀在EDA實驗教學中的一個典型的應用——基于FPGA的液晶顯示控制設計方案。

二、LCD顯示控制原理簡介

1、LCD的顯示控制原理

實驗的過程中使用了清華大學提供的EDA GW48-PK2教學實驗箱,主要使用其中的液晶顯示模塊,此液晶顯示器為HS12864-3型液晶顯示器,它是一種圖形點陣液晶顯示器,它主要由行驅動器和列驅動器及128×64全點陣液晶顯示器組成,包含七種指令,讀寫指令共用八路數據。可完成圖形顯示,也可以顯示8×4個(16×16點陣)漢字。

在實驗箱上,可以由FPGA直接控制LCD液晶顯示器,如圖1所示,FPGA保存子模,生成繪圖指令,并根據指令生成相應的時序,發送給LCD。LCD端的DDRAM控制器接收時序控制信號并將圖像顯示在液晶屏上。

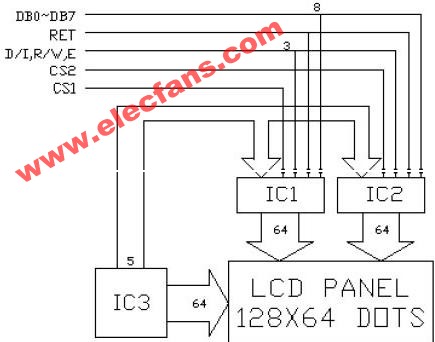

液晶模塊的硬件構成如圖2所示,液晶屏被分為左右兩個區域,它是通過片選信號CS0、CS1選擇當前信號所控制的區域,讀寫指令共用八路數據,通過幾根控制線完成液晶顯示器的讀寫工作。該設備內置64×64位的顯示存儲器DDRAM,顯示屏上各像素點的顯示狀態與DDRAM中的數據一一對應,DDRAM的數據直接作為圖形顯示的驅動信號。DDRAM中某一點的數據為“1”,則液晶屏上相應的像素點顯示;DDRAM中某一點的數據為“0”,則液晶上相應的像素點不顯示。圖2中,IC3為行驅動器,IC1、IC2為列驅動器,IC1、IC2、IC3中含有很多功能器件。

圖2 模塊主要硬件構成

通過控制DI、RW、E、CS1和CS2這五個信號管腳的電平并向數據總線上發送相應的數據,我們可以對液晶屏控制器進行簡單的操作指令,如顯示開關設置、顯示起始行設置、地址指針設置和數據讀/寫等指令。這些指令可以分為兩類,即顯示狀態設置指令和數據讀/寫操作指令,根據控制指令表(表1)書寫操作指令。

其中:D/I:數據/指令標志位,0表示數據總線上信號為指令,1表示數據總線上信號為數據;

R/W:讀/寫標志位,0表示FPGA向數據總線上做寫操作,1表示FPGA讀數據總線。

表1 液晶屏控制指令表

如圖3所示,在設計的過程中,讀寫時序非常關鍵,為保證讀寫操作的正確性,可用邏輯分析儀進行調試,主要觀察信號的時序關系,以及讀寫的數據值的正確與否。讀寫時序有具體的時序參數要求,可以通過邏輯分析儀的測量功能,測量其中時間參數與讀取時序參數表對照,具體測量方法詳見下文。

圖3 讀寫操作時序

2、設計思路

LCD顯示控制器設計要點:

1) LCD的讀寫是一個連續的過程,需要設置好起始地址后連續的進行寫入,這需要一個狀態機來實現(LCD控制器);

2) 向LCD發送指令之前需要確定LCD的狀態是否可以接收指令,即要先進行讀狀態字的操作,這也需要一個狀態機來實現(LCD讀/寫接口)。

3) HS12864-3液晶屏自帶DDRAM,讀寫DB[7..0]實際上是和DDRAM交換數據。

4) 由于DDRAM為并行8位數據總線,為了發送數據盡可能簡單,建議在LCD模塊中采用雙向8位RAM。

5) 不斷刷新128*64的每一像素的數據,但只需產生數據向雙向RAM中刷新。無需關心如何繪制到LCD上。

三、使用邏輯分析儀進行調試

1、設計過程中出現的問題

在實驗結果中發現LCD模塊每隔一段時間可能產生一些不穩定的因素,左半屏可能會不顯示,有時出現滾屏的現象,有時會在液晶顯示器上出現散點,或出現圖像混亂現象,如圖4所示。這種現象一般由于控制指令出現問題,控制線與數據線的時序關系出現偏差,出現這種現象需要使用邏輯分析儀進行調試。

圖4 液晶顯示的異常現象

2、搭建實驗環境

基于以上問題,需要我們搭建一套實驗環境,查找液晶顯示過程中可能出現的錯誤,實驗設備以邏輯分析儀為主,配備相應的測試附件,如果希望存儲實驗數據或者設置,還需要將邏輯分析與PC相連,利用邏輯分析儀的配套軟件,將所要的數據存儲下來。這樣便搭建了PC實時控制軟件+OLA邏輯分析儀+DUT待測設備的實驗環境。

3、連接方式

在邏輯分析儀與被測電路相連時,一般邏輯分析儀的標準配件有兩種連接形式,一種是插針連接方式,這需要實驗板上預留排針式的測試端口,這種情況一般出現在專業的測試板上,連接比較輕松;另一種是飛機頭連接方式,這種連接方式測試鉤非常小巧,可以隨意鉤在實驗板的測試管腳,對實驗板沒有特殊要求,如圖6所示。另外,我們北京海洋興業科技有限公司與美國Pomona公司合作提供很多其它形式的連接方式,如微型SMD測試夾、集成電路測試夾等等,根據用戶的需求建立不同的邏輯分析儀測試方案。

圖6 邏輯分析儀通過飛機頭連接被測電路

4、邏輯分析儀的使用

為了更方便、更快捷的解決設計中存在的問題,我們需要很好的使用邏輯分析儀,利用其獨有的特點和豐富的功能調試棘手的問題,所謂磨刀不誤砍柴工,如果可以很好地駕馭測試手段,就可以達到事半功倍的效果。下面我們主要介紹OLA2032B邏輯分析儀在這個設計實驗中如何最大的發揮作用。

1) Auto-Scale功能

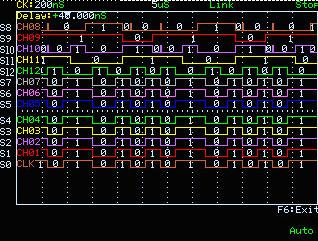

將邏輯分析儀的測試線與被測電路中想要觀察的信號管腳連接好之后,不需要任何設置,只要按下Auto-Scale功能鍵,待測信號便可以在屏幕上顯示,類似于數字示波器的Auto-Set功能,給邏輯分析儀的使用帶來前所未有的方便。如圖7所示,接入的13路信號全部顯示在屏幕上。

圖7 Auto-Scale功能

圖7 Auto-Scale功能

2) 總線形式顯示

由于邏輯分析儀的通道數很多,OLA2032B擁有32路數據通道,如果同時顯示這些信號,未免會顯得雜亂無章,這是我們需要總線形式顯示一組或幾組信號,每組的通道個數可根據實際情況設定,并且每組的信號有高位或地位的順序關系。例如,此實驗中,S0-S7是讀寫指令共用的數據通道,其它S8-S12為5路控制線,為了方便,可以將S0-S7設置成總線形式,并以十六進制或者十進制顯示,這樣可清晰的理解設計者的指令,如圖8所示,可以看出大部分時間寫入的數據為0,對照液晶顯示控制指令表,可以看出寫入的是液晶屏上空白的地方。

圖8 總線形式顯示

圖8 總線形式顯示

3) 通道命名

由于邏輯分析儀的通道數比較多,可以通過顏色來區分不同的通道,也可以給每一個通道命名,如圖所示,我們給每個通道定義與實際意義相符的名字,這樣就非常好區分,方便觀察時序關系。通道的命名可以在儀器上操作,也可以在計算機軟件上操作,后者使用計算機鍵盤,更加快捷。

4) 計算機軟件

OLA2032B邏輯分析儀可以通過一根USB電纜與計算機相連,通過配套軟件,可以讀取采集的信號數據和設置,可以在PC上控制儀器,并且讀取數據和控制儀器的速度都非常快,均可以達到USB2.0的速度,在計算機上顯示的信號波形基本與計算機上的波形同步,沒有延時。圖7圖8均為計算機存儲的圖片。

5) 觸發功能

同示波器類似,OLA2032B邏輯分析儀也具備豐富的觸發功能,包括高階的多階觸發、或階觸發等等。首先可以設置每個通道的狀態進行觸發,如上升沿、下降沿、高電平、低電平等狀態;其次可以進行脈沖寬度觸發,捕獲毛刺;另外可以進行多階觸發、或階觸發,我們稱之為既并行又串行的觸發,這種觸發方式可以用來分析數據的包頭、包尾等。在我們的實驗中,我們可以根據信號的時序關系觸發指定位置,例如圖8的觸發方式為使能端EN的下降沿,這里只用到了最簡單的單通道下降沿觸發方式。

6) 觀察時序使用測量功能

如前所述,對于液晶屏幕的讀寫時序有嚴格的時間限制,如果顯示出現錯誤,很可能是因為讀寫時序以及其持續時間不滿足要求,所以我們需要使用邏輯分析儀的光標測量功能來查找問題所在。OLA2032B提供了三組六根光標,可以測量每根光標對應基準位置的時間差和沒組光標兩根之間的時間差,這樣便可以將測量結果與液晶顯示器參數對照,查找問題所在。請對比圖8與圖3的時序關系。

四、使用邏輯分析儀的注意事項

1、輸入信號的電壓

由于數字信號的電平均較低,一般在5V以內,所以邏輯分析儀的耐壓能力較差,所以盡量不要將電壓較高的信號,長時間的接入邏輯分析中。例如,邏輯分析儀有時也可以用來測量和分析一些串行總線,如I2C、SPI等串行總線,但是一般不用邏輯分析儀分析RS232總線,因為RS232的電平較高,超過了邏輯分析儀的耐壓能力。

2、信號閾值

閾值是判決信號為高電平或低電平的門限電平,所以對于同一個信號,對應不同的閾值可能得到不同的結果,所以我們要根據實際情況選擇閾值大小,有些用戶想要雙閾值的判決,可是大多數邏輯分析儀沒有這項功能,一般將邏輯的域值設置成高電平的門限即可。

3、存儲深度

邏輯分析儀在采集信號時都會將采集到的信號存儲到存儲器(Memory)中,根據用戶的要求,需要采集多長時間、定時分辨率為多少來設置存儲深度,OLA2032B最大存儲深度為512Kbit/每通道。

4、數字信號與模擬信號的相關性

邏輯分析儀觀測到的信號,我們稱之為“偽信號”,只有高低電平之分,也就是說邏輯分析儀觀察到的信號只有水平軸是有意義的,它反映信號的時間關系,而垂直軸是沒有意義的,它并不代表幅度,如果信號出現了問題,尤其是串擾、毛刺等現象,我們要是想知道其來源以及產生原因,還需要與其它儀器相配合,如示波器、頻譜分析儀等等。

小結

本文介紹了邏輯分析儀在EDA教學中的應用,通過OLA2032B邏輯分析儀調試基于FPGA的LCD顯示控制設計方案的實驗。在測試的過程中,我們可以發現邏輯分析儀在基礎教學中起著很重要的作用,比示波器更適合調試數字電路。實踐證明,邏輯分析儀可以縮短我們的設計時間,解決其它儀器或者軟件解決不了的問題,并且它是多通道的時序分析的唯一解決方案,它可以同時看到硬件電路實際輸出的多路信號。我們北京海洋興業科技有限公司推出的OLA2032B邏輯分析儀,希望可以解決邏輯分析儀在基礎教學中作壁上觀的現狀,較高的性價比真正做到讓數字電路教學用得起邏輯分析儀。在這里非常感謝清華大學的老師給我們這樣好的平臺,使我們對我們的產品更有信心。

參考文獻

[1] 許忠信. LCD顯示控制器設計. 清華大學EDA實驗實驗教程.

[2] 康世胤. 基于FPGA的隨機序列發生器和LCD控制器. 清華大學.

[3] 王樂. 邏輯分析儀基礎知識簡介. 北京海洋科技有限公司網站. 06.12.25.

[4] 王樂. 邏輯分析儀的使用. 北京海洋科技有限公司網站. 07.05.08.

[5] 周家明. 邏輯分析儀與示波器的比較. 北京海洋科技有限公司網站. 07.02.15

電子發燒友App

電子發燒友App

評論