集成運放參數測試儀設計方案(2005年電子大賽一等獎)

概述:本系統參照片上系統的設計架構、采用FPGA與SPCE061A相結合的方法,以SPCE061A單片機為進程控制和任務調度核心;FPGA做為外圍擴展,內部自建系統總線,地址譯碼采用全譯碼方式。FPGA內部建有DDS控制器,單片機通過系統總線向規定的存儲單元中送入正弦表;然后DDS控制器以設定的頻率,自動循環掃描,生成高精度,高穩定的5Hz基準測量信號。掃頻信號通過對30MHz的FPGA系統時鐘進行分頻和外部鎖相環(FPGA采用FLEX10K10無內部鎖相環)倍頻,產生高頻率穩定度、幅值穩定度的掃頻信號。

放大器參數測量參照GB3442-82標準,低頻信號幅度的測量采取AD高速采樣,然后進行數字處理的方法;高頻信號的幅度直接采用集成有效值轉換芯片測得。A/D轉換采用SPCE061A內部自帶的10位AD。SPCE061A主要實現用戶接口界面(鍵盤掃描、液晶顯示、數據打印以及其他服務進程的調度)、AD轉換以及測量參數(Vio Iio Kcmr Avd BWG Tr)計算、與上位機通信等方面的功能。上位機主要實現向下位機發送測量指令、與下位機交換測量數據、以及數據的存儲、回放、統計。

一、方案比較設計與論證

(一)測量電路模塊

1、測試信號源部分

方案一:利用傳統的模擬分立元件或單片壓控函數發生器MAX038,可產生三角波、方波、正弦波,通過調整外圍元件可以改變輸出頻率、幅度,但采用模擬器件由于元件分散性太大,即使用單片函數發生器,參數也與外部元件有關,外接電阻電容對參數影響很大,因而產生的頻率穩定度較差、精度低、抗干擾能力差、成本也較高。

方案二:采用鎖相式頻率合成方案。鎖相式頻率合成是將一個高穩定度和高精度的標準頻率經過運算,產生同樣穩定度和精確度的大量離散頻率的技術,他在一定程度上滿足了既要頻率穩定精確,又要在大范圍內變化的矛盾。但其波形幅度穩定度較差,在低頻內波形不理想。

方案三:采用DDS技術。DDS以Nyquist時域采樣定理為基礎,在時域內進行頻率合成,其相位、幅度都可以實現程控,而且用FPGA來實現非常簡單。

在這里我們只需要一個5Hz的單一穩定頻率,要求其頻率,幅度穩定。綜合考慮,我們采用方案三,實現了高精度,高穩定度的5Hz測試信號源。

2、主測試電路

方案一:將測試放大器參數的實現分成4個電路檢測。該方案實現各個參數的測量比較好,且有利于各個參數調試。但是對于要實現智能測試該方案較復雜,在電路中所用的繼電器太多,很容易引起電磁干擾,不利于系統的整體性能提高,且不能實現電路的智能測試。

方案二:采用一級運放。該電路經過仔細的分析會發現它設計的非常的巧妙調試也很方便,不會產生自激、飽和等情況。缺點就是對與精度較高的運算放大器該方案實現不了。

方案三:采用試題中所給的電路。這是一個二級的電路,測試精度非常的高。但在調試中我們發現它很容易出現自激,為了使整個電路保持穩定,我們采取了一系列的穩定措施,如采用雕刻機雕刻線路,并實現大面積的接地,輔助運放加入補償矯正網絡等。

綜合上述,為了實現自動測量,保證測試有更高的精度,采用方案三。

3、信號放大電路

方案一:采用普通的運算放大器放大電路。運算放大器放大電路成熟可靠,選用不同的運算放大器,能夠對各種信號進行很好放大。但其放大值固定,不能動態調整,不便于處理大范圍變化信號。

方案二:采用程控可增益放大器。程控可增益放大器可用單片機方便的進行增益設定,十分有利于處理大動態范圍信號。

由于測量信號動態范圍大,要有效的采樣處理,就要求放大器增益可動態調整,由此我們選用方案二,采用可編程增益放大器AD625和數字電位器AD737組成程控增益放大器,實現對測量信號的有效放大。

4、濾波電路

方案一:采用二階切比雪夫低通濾波器或二階巴特沃斯低通濾波器。切比雪夫 濾波器的幅度響應在通帶內是在兩值之間波動,在通帶內波動的次數取決于濾波器的階數。理想的在靠近截止頻率的范圍內比巴特沃斯有更接近矩形的頻率響應。但這一點是一在頻帶內允許波動為代價的。巴特沃斯低通濾波器幅頻響應是單調下降的,其N階低通濾波器的前(2N-1)階導數在頻率為零處始終為零,故又稱為最大平坦幅度濾波器。

方案二:采用數字濾波。數字濾波有極大的靈活性,可以在不增加任何硬件成本的基礎上對信號進行有效的濾波,而且可以實現模擬器件難以實現的高階濾波。但要進行高效率的濾波,對AD采樣要求有較高的采樣速率和時實性,對單片機要求有較高的數據運算速度。

方案三:采用模擬濾波器加數字濾波。先用模擬濾波器對信號進行簡單的濾波處理,然后AD采樣,進行數字濾波。這樣既可以更加有效的對信號進行濾波,使有效信號更為純凈,便于后級數據處理,又降低了對ADC及單片機的要求,使得利用SPCE061A可以較輕松的實現

在本題中,測量輸出有效信號同樣為5Hz,但伴有大量的高頻及較嚴重的50Hz工頻干擾,為了保持通帶內有效信號的平坦性及純凈,我們選用方案三,模擬用二階巴特沃斯低通濾波器,數字濾波采用有限沖擊響應法設置了低通濾波器及50Hz陷波器。

(二)信號采集模塊

方案一:用AD736 RMS真有效值轉換芯片,AD736的響應頻率在0~10KHZ,采用該器件只需將被測的信號加到它的輸入端上,就可以得到它的有效值,無需軟件處理,測試非常的方便。但是我們在調試中現在AD736 在響應低頻的時候不是很穩定,這樣對整個系統會帶來不穩定。因此我們沒有選用這個方案。

方案二:采用A/D轉換,將模擬信號數字化,然后進行數據處理。 凌陽16位單片機內置有8路10位的A/D,運用起來非常的方便。無需外圍的電路,轉換精度也比較高,因此我們采用了方案二。

(三)用戶接口模塊

1、 顯示方案:

方案一:采用LED或字符型LCD顯示。LED可以用移位寄存器74164或者專用芯片MAX7219驅動,字符型LCD也可以才用74LS164通過同步串口驅動。優點是控制比較簡單,而且串行顯示只占用很少的I/O口。但也有一個很大的缺點,只能顯示一些簡單的ASCII碼字符,顯示的信息量十分的有限,對于本系統較復雜的功能不太適合。

方案二:采用點陣型LCD顯示。點陣型LCD雖然占用的I/O口資源較多,控制也較復雜,但其功能卻是強大的,顯示信息量大,可以保證良好的用戶模式。且我們在系統中用FPGA設計的總線方式,擴展了I/O資源,就無須考慮I/O資源的限制了。

經過綜合考慮我們選擇方案二,不需要很復雜的電路就可以實現并擴展非常強大的顯示功能。

2、 鍵盤輸入方案:

方案一:采用7289芯片與鍵盤相結合,鍵盤的整個控制只需4條控制線。程序的編寫也比較簡單且容易同led顯示接口。

方案二:不使用任何專用芯片,用一塊74LS138譯碼輸出8路掃描信號,3路掃描返回信號線接I/O口輸入(我們設計的是3*8的鍵盤)。這種設計方案電路設計非常的簡單,但是軟件的編寫要考慮軟件去抖等,會比較復雜而且占用大量的CPU資源。

方案三:在FPGA內部構造一鍵盤掃描控制器,專門用以處理按鍵信息,并進行初步的處理(如鍵盤去抖),通過中斷把鍵值發送給單片機。由于我們在FPGA內部已經建立了系統總線,擴展鍵盤非常簡單。而且采用此方法外部硬件電路的設計也非常簡單。

比較三者的優缺點我們選擇了方案三,這樣充分利用CPLD的功能硬件與軟件設計都比較簡單。 二、整機工作原理與功能實現  ?圖2-1-1 系統整體結構示意圖?

?圖2-1-1 系統整體結構示意圖?

系統電路原理圖如圖5-3-1所示。通過繼電器的切換實現四個基本參數和大量程的轉換。測量開環放大倍數和共模抑制比的基準信號采用DDS合成技術產生(DDS合成控制器通過硬件編程在FPGA內部生成)。信號的幅值通過精密整流后的響應信號高速采樣,再經過數字信號處理的方法獲得。采樣信號的幅值測量采用等精度測量方法,通過程控放大器將采樣信號的幅度控制在1-3.3V之間,這樣可以使小信號測量時有效位數增多,又克服了測量大信號量程不足的限制。

-3dB帶寬的測量,通過FPGA與外部鎖相環對30MHz信號進行分頻與倍頻,產生高精確度的掃頻信號,然后通過隔直電容加到被測放大器的同相輸入端(放大器通過繼電器切換接成單位增益組態),放大器的輸出信號通過隔直電容加到有效值轉換芯片的輸入端。掃頻信號從40kHz開始逐漸增大,同時通過AD檢測有效值轉換芯片的輸出電壓,當輸出電壓下降到原來的0.707倍時記下此時的頻率值既是-3dB帶寬截止頻率。

上升時間的測量,單片機向某一特定地址中寫入任意值,啟動上升時間測量功能。接著FPGA輸出一階躍信號給被測放大器(被測放大器也接成單位增益組態),同時啟動高速計數,放大器的輸出信號送給一比較電平設為0.9Vdd的高速比較器,當放大器輸出端的信號增大到0.9Vdd時比較器輸出高電平,FPGA內部計數器停止計數。如圖2-1-2根據此計數值和計數時鐘的頻率便可以得到上升時間。  ???????

???????  ?????

?????

? 圖2-2-1無操作系統與有操作系統的區別

設計到很多的硬件、軟件及其混合的設計。采用操作系統的架構來組織,將非常有利于我們小組各個成員之間的協作開發。有的人專注于服務進程以及用戶界面和數據處理,有人專注于FPGA系統總線和外圍器件以及底層驅動程序的設計。

Mini OS是一款擁有可裁剪、多任務的占先式內核的操作系統。它的任務調用及中斷時間是可知道的,因此,采用Mini OS操作系統將大幅改善軟件設計的環境,提高軟件設計的規范。且該系統的底層模塊完全采用匯編語言編寫,然后采用操作系統調度的方法,很大程度上提高了系統的實時性和執行效率。如圖2-2-2

圖2-2-2 Mini OS 各進程示意圖  (三)其他系統擴展

(三)其他系統擴展

1、語音播報方案

為了豐富人機的接口我們增加了語音的播報利用 凌陽SPCE061位單片機的語音處理功能。只須調用庫函數即可以實現音頻編程或自己錄制語音資源就可以實現語音播放以及語音報警功能。

2、打印功能

為了能夠將測量數據打印出來,我們采用了TL58打印機,該打印機小型、輕便、我們使用并口打印,控制也非常的方便。它帶國家一、二級字庫,可以滿足一般打印的需求。

3、串口通信功能

??? 為了適應網絡化的趨勢,為了能夠進行大批量的數據統計與分析我們設計了此與上位機進行通訊的串行數據接口。我們可以通過此串行接口,將一批運放的測量參數上傳到上位機,然后進行統計分析,對這一批運放的性能參數給出有效的估計。這在實際的科研、生產中比只測量一兩個放大器的參數具有更大的意義。我們還可以通過上位機控制下位機測量相應的參數,并在顯示屏上顯示下位機無法顯示的參數(如波特圖、對正弦信號相應的頻譜)具有虛擬儀器的功能。

三、各子模塊的設計

(一)輸入電壓4~40mV、輸入電流0~4mA量程轉換:

??? 量程轉換通過繼電器和程控放大器相結合實現。繼電器切換大量程;程控放大器切換小量程,最終將信號的幅度控制在1-3.3V之間,這樣既可以使小信號測量時有效位數增多,又克服了測量大信號量程不足的限制;保證了測量的精度和范圍,實現等精度測量。

圖3-3-1?? DDS外圍電路 (四)單位增益帶寬測試:

在該功能中需要40KHZ--4MHZ的掃頻信號,我們通過FPGA和外部鎖相環對30MHz的系統時鐘進行程控分頻和倍頻生成,從而使產生的頻率可以進行數字控制,而且極其穩定。為了測試放大器的截止頻率,我們需要檢測單位增益組態的放大器對掃頻信號的響應情況。對于如此高頻的信號我們不能采用A/D采樣方法處理了,而是采用RMS真有效值轉換的芯片,進過實驗的測試我們最終選用AD637芯片。它的標定響應頻率為6MHZ。我們對其進行了檢測,該芯片完全符合我們的需求。  圖3-1-1 程控放大器原理圖(自動量程轉換)

圖3-1-1 程控放大器原理圖(自動量程轉換)

(二)靜態參數與動態參數的測量:

靜態參數與動態參數的測量具有完全不同的特點,靜態參數測量電路要考慮靜態誤差,系統穩定度等。動態參數測量電路要考慮電磁干擾以及高頻信號的衰減補償等。兩個電路有著完全不同的設計方法和技術指標要求。我們在設計中采用兩個電路分開設計的方法,在最后通過一個繼電器實現兩個電路的切換。

(三)5Hz 4V有效值正弦波的實現:

5HZ 4V信號在電路中要多次用到,對該信號的穩定度有較高的要求,該信號的好壞直接關系到測量的精度。我們采用先進的DDS直接數字頻率合成技術,產生高幅值穩定度和頻率穩定度的信號。外圍電路如圖3-3-1所示:

圖3-4-1鎖相環外圍及接口電路

圖3-4-2 BWG測量電路

(五)自動測量功能的實現:

我們采用了兩大組繼電器來控制電路狀態,實現參數的自動測量。第一組為主測量電路部分,采用6個繼電器實現四個基本參數的測量。由于測量BWG和Tr需要采用完全不同的電路,我們又加入兩個繼電器,很方便的實現兩個電路的切換。示意圖如圖3-5-1:

(六)顯示模塊:

??? 液晶顯示采用金鵬的OCM4X8C型液晶顯示模塊,該模塊是128×64點陣的漢字圖形型液晶顯示模塊,可顯示漢字及圖形,內置國標GB2312碼簡體中文字庫(16X16點陣)、128個字符(8X16點陣)及64X256點陣顯示RAM(GDRAM)。可與CPU直接接口,提供兩種界面來連接微處理機:8-位并行及串行兩種連接方式。具有多種功能:光標顯示、畫面移位、睡眠模式等。

(七)鍵盤模塊:

原理如圖3-7-1所示。鍵盤通過FPGA進行管理,當有鍵按下時,觸發中斷;去抖后將數據發送給單片機,單片機主服務進程接受按鍵值,然后根據按鍵值調度相應的進程。

?圖3-7-1 鍵盤電路原理圖 圖3-7-2 鍵盤服務進程調度示意圖 (八)、UART-PC機通訊:

圖3-7-2 鍵盤服務進程調度示意圖 (八)、UART-PC機通訊:

串口是計算機與外部設備進行數據交換的重要介質,所以串行通信在實際工程實現中有著廣泛的應用。而Microsoft公司的VC++6.0功能強大,其基礎類庫(MFC)封裝了WIN32 API中的標準通信函數,可方便的支持串口通信。在放大器參數測試儀的設計中,能夠很方便地將放大器的各個參數數據顯示并存儲。

我們運用了串口進行了下位機(單片機)與上位機(PC機)的通信。如圖3-8-1上位機接收數據,顯示數據界面。

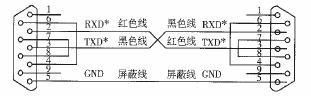

圖3-8-1上位機界面 二者通過RS-232串行口接收或上傳數據和指令。傳輸介質為二芯屏蔽電纜,接線圖如下圖3-8-2所示:

?

圖3-8-2? RS-232串行口接線圖

RS-232信號的電平和單片機串口的電平不一致,必須進行二者之間的電平轉換。在此使用的集成電平轉換芯片MAX232為RS-232C/TTL電平轉換芯片。它只使用單+5V為其工作,配接4個1UF電解電容即可完成RS-232電平與TTL電平之間的轉換。其原理圖如下圖所示,轉換完畢的串口信號TXD、RXD直接和單片機SPCE061A相連接。

圖3-8-3? MAX232外圍原理圖

四、理論計算及分析  圖4-1-1?? 主測量電路原理圖

圖4-1-1?? 主測量電路原理圖

(一)開環放大倍數的測量

如圖4-1-2繼電器狀態:K1,K2接地,K3,K4接通,K5接地,K6接信號輸入端。整個電路構成一個大的環路負反饋,信號從R7端輸入,根據虛短虛斷的概念,因為R7上端與放大器的同相端相聯,為地電位;所以節點OUT1的電位為: ??  (

(  )

)

又:?????????  (

(  為放大器U2的輸出電壓)

為放大器U2的輸出電壓)

得:??????????????????? ??

??

所以:

?圖4-1-2 開環放大倍數測量原理圖

(二)輸入失調電壓的測量

繼電器狀態:K1,K2接地,K3,K4接通,K5,K6接地。如圖 4-2-1

K6接地,放大器U1的輸出與放大器U2的同相端通過一電阻分壓網絡相連,而放大器U2的反相端接地。所以:  根據輸入失調電壓的定義:

根據輸入失調電壓的定義:

???????????????? ?? (

?? (  )???

)???  ?

?

?

圖4-2-1 輸入失調電壓測試原理圖

(三)輸入失調電流的測量

繼電器狀態:K1,K2接地,K3,K4斷開,K5,K6接地。如圖4-3-1

與上面相同有 ,所以有:

,所以有:

????????????????????

?????????????????

?????????????????

?

圖4-3-1 輸入失調電流測試原理圖

(四)共模抑制比的測量

繼電器狀態:K1、K2接信號端,K3、K4閉合。K5,K6接地。如圖4-4-1?運放應對共模信號有很強的抑制能力。表征這種能力的參數叫共模抑制比,用kCMR表示。它定義為差模電壓增益AvD和共模電壓增益Avc之比,即kCMR=∣AvD/Avc∣。

測試原理如圖35.5所示。由于RF>>RI,該閉環電路對差模信號的增益AvD= RF/RI。共模信號的增益AvC= (VO/VS)。因此,只要從電路上測出VO和VS,即可求出共模抑制比

??? ??? KCMR=∣AvD/Avc∣= (RF/RI)o(VS/VO)

KCMR的大小往往與頻率有關,同時也與輸入信號大小和波形有關。測量的頻率不宜太高,信號不宜太大。

?

圖4-4-1 共模抑制比測量原理圖

(五) -3dB帶寬F0

繼電器狀態:K7斷開,K4閉合,K2接信號端;被測放大器構成單位增益狀態。K9接OUT1將單位增益狀態的放大器信號輸出。

-3dB帶寬的測量,通過FPGA與外部鎖相環對30MHz信號進行程控分頻與倍頻,產生高精確度的掃頻信號,然后通過隔直電容加到被測放大器的同相輸入端(放大器通過繼電器切換接成單位增益組態),放大器的輸出信號通過隔直電容加到有效值轉換芯片的輸入端。掃頻信號從40kHz開始逐漸增大,同時通過AD檢測有效值轉換芯片的輸出電壓,當輸出電壓下降到原來的0.707倍時記下此時的頻率值既是-3dB帶寬截止頻率。

(六)轉換速率(SR)和上升時間的測量

脈沖響應時間包括上升時間,下降時間、延遲時間、和脈動時間等。測試電路仍然采用以上電路,繼電器狀態K7斷開,K4閉合,K2接信號端;被測放大器構成單位增益狀態。K9接OUT1將單位增益狀態的放大器信號輸出。讀取響應時間方法如下圖所示。其中tr為上升時間,tf為下降時間,td(r)為上升延遲時間,td(f)為下降延遲時間。在單片機的控制下,FPGA發出一階躍信號,同時觸發高速計數,通過一高速比較器檢測放大器的輸出狀態,當上升到0.9Vdd時鎖存計數值,同時觸發中斷,將計數值送給單片機。單片機根據此計數值和計數頻率便可以計算出上升時間。

圖4-6-1? Tr示意圖

五、電路圖及有關設計文件

(一)電源電路:

為了保證足夠的電源供應,我們制作了一個有±5V、±12V、±15V、0~30V可調的電壓源。 圖5-1-1、圖5-1-2是原理圖

圖5-1-1? 電源電路

?

?圖5-1-2 電源電路

(二)單片機、FPGA系統板電路:

圖5-2-1 單片機、FPGA系統圖

SPCE061A單片機與FPGA為基本系統。數控部分采用SPCE061A同FPGA相結合,61單片機內置有32K Flash 存儲和2K的RAM、8通道的10位A/D、10位D/A。我們用VHDL為FPGA編寫了一個的總線控制器擴展SPCE061A的I/O端口。

(三)測量電路

圖5-3-1?? 測量電路原理圖

(四)精密整流電路

Vo1=0???? (Vi )

)

Vo1=-Vi?? (Vi>= 0)?????????? (1)

運放二構成反相加法器,其輸入為Vi和Vo1,所以有

Vo=-Vi-2Vo1????????????????? (2)

將其帶入式(1)中有:

Vo1=-Vi??? (Vi )

)

Vo1=+Vi??? (Vi >=0)

圖5-4-1 精密整流電路原理圖

(五)低通濾波電路

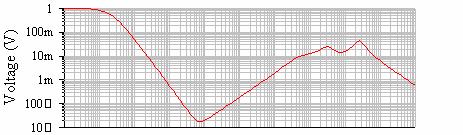

??? 我們在這里設計了個 =30Hz 的有源低通濾波電路。并通過繼電器控制它的通斷,我們把 設計在30HZ主要是保護5HZ的信號不被衰減,也可以讓50HZ及以上的干擾信號進行衰減。圖2-2-6這些電路我們都是用Muilisim2001 軟件進行嚴格的仿真及論證。在1~5ZH信號是960mV ,50Hz的信號是187mV(輸入的交流信號在1V)

圖5-5-1? 低通濾波原理圖

圖5-5-2? 5HZ低通濾波電路仿真圖

六 、系統測試 測量環境 : 24℃

日??? 期 : 2005年9月10日

測試儀器 : 電源:WD990

示波器 TDS2012

信號發生器 GFG-8255A

數字萬用表 FLUKE175

失真度測量儀 ZQ4126

交流毫伏表 HG2170

????? PC P41.7G 128M內存

仿真器:SPCE061A PROBE;EL EDA 測試數據: 表 6-1測試數據

| 集成運算放大器參數測試數據一覽表 | |||||||

| 測試參數 \ 測試器件 |

輸入失調電壓 mV |

輸入失調電流 nA |

共模抑制比 dB |

開環放大倍數 dB |

單位增益帶寬積 MHz |

上升時間 us | |

| LM741C | 測試值 | 1.514 | 18.451 | 88 | 92 | 1.154 | 0.265 |

| 典型值 | 2 | 20 | 90 | 106 | 1.0 | 0.3 | |

| 最大值 | 6 | 200 | 70(MIN) | 86(MIN) | 1.2 | -- | |

| UA741 | 測試值 | 2.414 | 22.456 | 89 | 103 | 0.887 | 0.278 |

| 典型值 | 1 | 20 | 90 | 106 | 0.7 | 0.3 | |

| 最大值 | 5 | 30 | 70(MIN) | -- | 1.0 | -- | |

| OP07 | 測試值 | 0.074 | 1.287 | 120 | 107 | 0.554 | 1.211 |

| 典型值 | 0.030 | 0.4 | 126 | 106 | 0.6 | ||

| 最大值 | 0.075 | 2.8 | 110(MIN) | -- | 0.4 | -- | |

| LM356 | 測試值 | 6.854 | 0.042 | 88 | 105 | 4.776 | 1.437 |

| 典型值 | 3 | 0.003 | 100 | 106 | 5 | 1.5 | |

| 最大值 | 10 | 0.050 | 80(MIN) | 88(MIN) | -- | -- | |

| LM318 | 測試值 | 8.451 | 0.145 | 94 | 103 | -- | 0.177 |

| 典型值 | 4 | 0.030 | 100 | 106 | 15 | -- | |

| 最大值 | 10 | 0.200 | 70(MIN) | 88(MIN) | |||

抗干擾措施:

系統要測量信號非常微弱,最小數量級可達PA級,增益高,非常容易受干擾和產生自激。因此抗干擾措施必須做的很好,才能避免自激,減小噪聲,提高測量精確度。通過理論分析和實驗,我們采用下述方法減小干擾,避免自激。

1.?將系統測量電路放入屏蔽盒中進行電磁屏蔽,避免空間高頻電磁干擾,和工頻干擾。

2.?模數隔離。由于數字電路有非常大的高頻對地干擾,非常容易對模擬電路產生影響。在電路板制作中我們采用了模擬地數字地一點接地。

3.?由于主測量電路工作在高增益狀態下,極易產生自激,使得測量無法進行。為消除自激,我們對輔助運放加上相位矯正網絡,在靠近兩運放處對正負供電進行電源去耦。去耦電容采用一大一小:大的選用漏電流較小的钅旦電解電容,小的采用具有優良高頻特性的cbb電容。這些有效的保證了電路的穩定。

4.電源隔離。由于系統要有 供電,其中繼電器的開關噪聲非常大,實際示波器測量可看到瞬間峰值可達1V,我們采用了完全的獨立電源供電,有效減小對主測量電路的影響。

七、結論

基本完成了系統基本及發揮部分的要求,在某些方面性能有極大的提高,大大超過了要求。但由于時間緊張等原因,整個系統還存在著設計簡陋,測量精度不是很高等問題。由于系統采用了模塊化設計,系統還有很大的升級擴展空間。經過進一步的完善,完全可以應用于實際測量中。

參考文獻:

1 電子電路設計與實踐. 姚福安編著. 山東省科學技術出版社.2001

2 MCS-51單片微型計算機原理與接口技術. 東北大學出版社.1994

3 全國大學生電子設計競賽組委會. 第四屆全國大學生電子設計競賽獲獎作品選編.

4 凌陽16位單片機基礎原理與應用.?? 北航出版社

5 計算機控制系統.?? 機械工業出版社

6 電子系統設計.?? 浙江大學出版社

7模擬集成電路應用.?? 山東大學出版社

8 VHDL數字電路設計應用實踐教程.?? 機械工業出版社

9 FPGA設計及應用.?? 西安電子科技大學出版社?

10 VC++6.0應用設計及提高?? 電子工業出版社

電子發燒友App

電子發燒友App

評論