引言

測試CMOS電路的方法有很多種,測試邏輯故障的一般方法是采用邏輯響應測試,即通常所說的功能測試。功能測試可診斷出邏輯錯誤,但不能檢查出晶體管常開故障、晶體管常閉故障、晶體管柵氧化層短路,互連橋短路等物理缺陷引發(fā)的故障,這些缺陷并不會立即影響電路的邏輯功能,通常要在器件工作一段時間后才會影響其邏輯功能。

功能測試是基于邏輯電平的故障檢測,通過測量原始輸出的電壓來確定邏輯電平,因此功能測試實際上是電壓測試。電壓測試對于檢測固定型故障,特別是雙極型工藝中的固定型故障是有效的,但對于檢測CMOS工藝中的其他類型故障則顯得有些不足,而這些故障類型在CMOS電路測試中卻是常見的。對于較大規(guī)模電路,電壓測試測試集的生成相當復雜且較長,需要大量的實驗數據樣本。

IDDQ測試是對功能測試的補充。通過測試靜態(tài)電流IDDQ可檢測出電路中的物理缺陷所引發(fā)的故障。

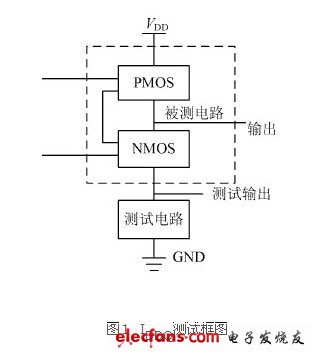

IDDQ測試還可以檢測出那些尚未引起邏輯錯誤,但在電路初期會轉換成邏輯錯誤的缺陷。本文所設計的IDDQ電流測試電路對CMOS被測電路進行檢測,通過觀察測試電路輸出的高低電平可知被測電路是否有物理缺陷。測試電路的核心是電流差分放大電路,其輸出一個與被測電路IDDQ電流成正比的輸出。測試電路串聯在被測電路與地之間,以檢測異常的IDDQ電流。

1 IDDQ測試原理

電流IDDQ是指當CMOS集成電路中的所有管子都處于靜止狀態(tài)時的電源總電流。對于中小規(guī)模集成電路,正常狀態(tài)時無故障的電源總電流為微安數量級;當電路出現橋接或柵源短接等故障時,會在靜態(tài)CMOS電路中形成一條從正電源到地的低阻通路,會導致電源總電流超過毫安數量級。所以靜態(tài)電源電流IDDQ測試原理是:無故障CMOS電路在靜態(tài)條件下的漏電流非常小,而故障條件下漏電流變得非常大,可以設定一個閾值作為電路有無故障的判據。

CMOS集成電路不論其形式和功能如何,都可以用一個反向器的模型來表示。IDDQ測試電路框圖如圖1所示,電路IDDQ檢測結果為一數字輸出(高低電平)。測試電路中電流差分放大電路的輸出與被測電路的IDDQ成正比。測試電路串聯在電源、被測電路與地中間,以檢測異常的IDDQ電流。為了實現測試,需要增加兩個控制端和一個輸出端。

用戶評論

共 0 條評論