在fpga工程中加入時序約束的目的: 1、給quartusii 提出時序要求; 2、quartusii 在布局布線時會盡量優先去滿足給出的時序要求; 3、STA靜態時序分析工具根據你提出的約束去判斷

2020-11-25 11:39:35 5320

5320

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 時序分析是FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-10-21 09:28:58 1283

1283 可能無法滿足時序要求。 跨時鐘域信號的約束寫法 問題一: 沒有對設計進行全面的約束導致綜合結果異常,比如沒有設置異步時鐘分組,綜合器對異步時鐘路徑進行靜態時序分析導致誤報時序違例。 ??約束文件包括三類,建議用戶應該將這三類約束

2023-08-01 09:18:34 1041

1041

FPGA中時序約束是設計的關鍵點之一,準確的時鐘約束有利于代碼功能的完整呈現。進行時序約束,讓軟件布局布線后的電路能夠滿足使用的要求。

2023-08-14 17:49:55 711

711

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 842

842

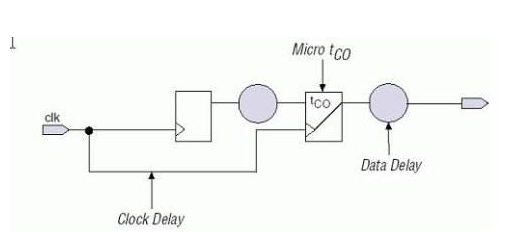

FPGA時序分析系統時序基礎理論對于系統設計工程師來說,時序問題在設計中是至關重要的,尤其是隨著時鐘頻率的提高,留給數據傳輸的有效讀寫窗口越來越小,要想在很短的時間限制里,讓數據信號從驅動端完整

2012-08-11 17:55:55

FPGA時序分析與約束(1)本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:Inter1、什么是時序分析?在FPGA中,數據和時鐘傳輸路徑是由相應的EDA軟件通過針對特定器件的布局布線

2021-07-26 06:56:44

你好: 現在我使用xilinx FPGA進行設計。遇到問題。我不知道FPGA設計是否符合時序要求。我在設計中添加了“時鐘”時序約束。我不知道如何添加其他約束。一句話,我不知道哪條路徑應該被禁止。我

2019-03-18 13:37:27

在FPGA內部的延時不超過某個值,那么FPGA內部的布局布線方式就會受到限制。所以,當我們進行完綜合之后還需要對時序進行分析,以使設計可用。

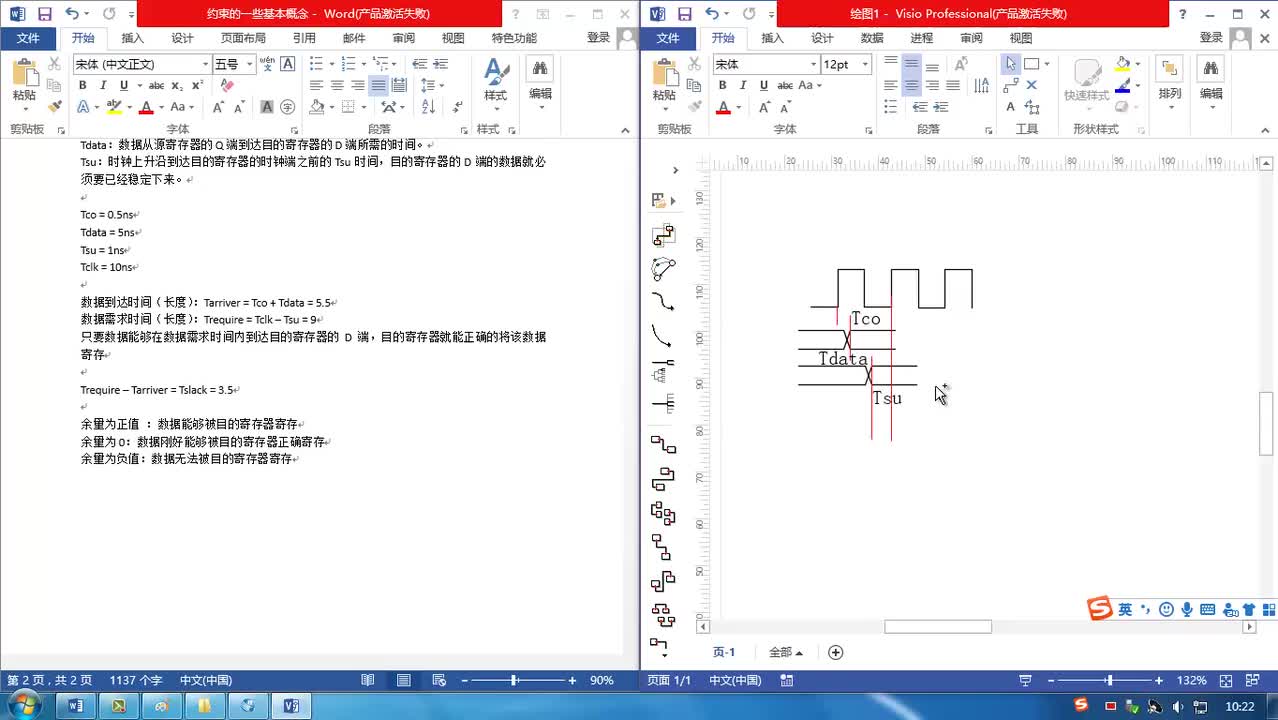

時序分析的基本概念

當我進行時序分析籠統的說應該

2011-09-23 10:26:01

控。從最近一段時間工作和學習的成果中,我總結了如下幾種進行時序約束的方法。按照從易到難的順序排列如下:0. 核心頻率約束 這是最基本的,所以標號為0。1. 核心頻率約束+時序例外約束 時序例外約束包括

2016-06-02 15:54:04

基本的時序分析理論1本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 何謂靜態時序分析(STA,Static

2015-07-09 21:54:41

8.5所示,FPGA將重新進行布局布線。(特權同學,版權所有)圖8.5 時序分析實例2重新布局布線由于添加了時序約束,因此,FPGA的布局布線工具會根據這個實際需求,重新做布局布線。重新布局布線后

2015-07-14 11:06:10

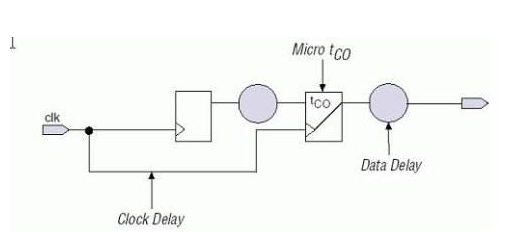

的。請大家記住這一點,下面我們需要利用這個信息對在FPGA內部的PCLK和D[7:0]信號進行時序約束。(特權同學,版權所有)圖8.47 CMOS Sensor輸出信號模型明確了PCLK和D[7:0

2015-08-14 11:24:01

FPGA的時序優化高級研修班通知通過設立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優化的方法。1.FPGA靜態時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優化方法

2013-03-27 15:20:27

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-09-21 07:45:57

用第三方的專門時序分析工具進行時序分析,一般FPGA廠商在其設計環境下皆有與第三方時序分析工具的接口。Synopsys公司的PrimeTime是一個很好的時序分析工具,利用它可以達到更好的效果。將綜合

2018-08-29 09:59:08

,因此,為了避免這種情況,必須對fpga資源布局布線進行時序約束以滿足設計要求。因為時鐘周期是預先知道的,而觸發器之間的延時是未知的(兩個觸發器之間的延時等于一個時鐘周期),所以得通過約束來控制觸發器之間的延時。當延時小于一個時鐘周期的時候,設計的邏輯才能穩定工作,反之,代碼會跑飛。

2018-08-29 09:34:47

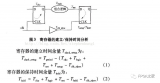

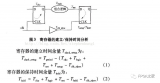

整個系統進行時序分析,所以FPGA需要作為一個整體分析,其中包括FPGA的建立時間、保持時間以及傳輸延時。傳統的建立時間、保持時間以及傳輸延時都是針對寄存器形式的分析。但是針對整個系統FPGA的建立

2012-04-25 15:42:03

如題:fpga時序分析一般都做哪些分析我自己研究時序分析也有一段時間了 ,從理論到altera的timequest,差不多都了解了 ,但就是不知道一個具體的項目都要做哪些約束。求大神知道,或者有沒有這方面的資料(網上資料基本都看過了,沒有說明具體項目的)。

2012-10-22 22:20:32

在學習fpga的過程中的疑問:1、在功能仿真和板級驗真后沒問題,還需要進行時序分析嗎2、怎么知道自己寫的代碼有時序問題?

2017-01-08 17:50:35

fpga時序邏輯電路的分析和設計 時序邏輯電路的結構及特點時序邏輯電路——任何一個時刻的輸出狀態不僅取決于當時的輸入信號,還與電路的原狀態有關。[hide][/hide]

2012-06-20 11:18:44

Modelsim庫的概念,分析一下Quartus II自動完成仿真的代碼,最后能自己寫一些簡單的do文件利用我們添加的仿真庫自動進行時序仿真。前兩個部分是簡單的操作,掌握其中一個部分即可進行時序仿真。最后

2012-02-01 11:37:40

請教大牛,在用quartus II 9.1時進行時序約束時一按鬧鐘按鈕打開time quest界面時程序就卡死了,不知道哪里出問題了,請教大牛應該怎莫辦才好

2019-03-06 06:35:15

請問我已經create了一個bdf文件,怎么對它進行時序分析?

2016-10-08 20:15:41

Verilog HDL 中進行時序控制分別通過下面兩種方式進行:? 延時控制;? 事件控制。延時控制的語法如下:#delay procedural_statement延時控制定義為執行過程中首次遇到

2018-09-25 09:16:12

目標InTime依據人工智能進行數據分析,能自動實現綜合編譯策略的選擇。通過多次迭代,最終確定能滿足時序約束的綜合策略。通過本次的試用,驗證InTime的可用性及有效性,為后續FPGA項目開發流程改進上

2017-07-05 11:00:48

視頻教程利用MiniStar開發板進行講解,視頻課程注重基礎知識和設計思路的講解,幫助初學者了解Gowin的FPGA的物理約束和時序約束。

2021-05-06 15:40:44

什么是時序分析?時序約束的作用是什么?FPGA組成的三要素分別是哪些?

2021-09-18 06:05:51

映射后需要對一個設計的實際功能塊的延時和估計的布線延時進行時序分析;而在布局布線后,也要對實際布局布線的功能塊延時和實際布線延時進行靜態時序分析。從某種程序來講,靜態時序分析可以說是整個FPGA設計中最

2021-05-27 09:28:40

各位好,初次使用pt對fpga進行靜態時序分析,想請教下需要哪些文件。是不是需要:1、在ise或qutartus生成的網表2、SDC文件3、.db文件.db文件必須且只能從dc生成嗎,要是從.lib轉化而來,這個lib文件在fpga設計時又從哪里得到問題貌似比較多,謝謝回答

2014-12-18 16:15:12

,不同的寄存器在時鐘脈沖的激勵下相互配合完成特定的功能,所以要保證不同的寄存器在同一時刻的時鐘脈沖激勵下協同工作,就需要進行時序分析,通過分析得結果對FPGA進行約束,以保證不同寄存器間的時序要求

2017-02-26 09:42:48

邏輯。而對其進行時序分析時,一般都以時鐘為參考的,因此一般主要分析上半部分。在進行時序分析之前,需要了解時序分析的一些基本概念,如時鐘抖動、時鐘偏斜(Tskew)、建立時間(Tsu)、保持時間(Th)等

2018-04-03 11:19:08

你好,我有兩個設計,一個工作在250MHz,另一個工作在450 MHz ......面積不大..我想知道如何為特定的fpga設備進行時序估計。要在fpga上實現特定的設計,我應該知道我的設計是否適合

2020-06-12 14:40:33

片上系統(SoC) IC的廣泛使用,對電源進行時序控制和管理變得越來越重要,今天我們來談一下這個問題?歡迎大家留言一起交流

2019-11-12 10:07:54

延遲和確定正確的相位偏移。4. 使用FPGA設計要素大多數的FPGA利用約束驅動進行布局和布線。時序約束為關鍵信號提供時序信息。TimingDesigner提供獨特的時序參考圖如測量和計算變量結果,從

2009-04-14 17:03:52

以下針對目前項目所用到的SRAM時序進行分析,同時也對SRAM應用在STM32F4上進行詳細解說。以此也可以類推出NAND/PSRAM等時序的應用技巧。時序當前用到的是模式A,其中讀時序如下。圖片截

2022-01-07 07:20:20

問一下啊,在寫時序約束的時候,如何根據設計的要求進行時序上的約束啊,看了好多網上的資料,說的都是有關約束的一些原理。有沒有那位大俠給個設計實例啊!

2023-04-23 11:42:16

1. FPGA時序原理2. 利用quartus進行時序分析3. 查看時序分析報告4. 時序練習1明德揚原價99元的視頻資料,包含100多個案例教學,現在完全免費,共享給大家。更多精彩視頻盡在百度云盤,百度云網址,http://pan.baidu.com/s/1hqIv7ms

2015-11-02 14:34:46

1. FPGA時序的基本概念FPGA器件的需求取決于系統和上下游(upstream and downstrem)設備。我們的設計需要和其他的devices進行數據的交互,其他的devices可能是

2019-07-09 09:14:48

映射后需要對一個設計的實際功能塊的延時和估計的布線延時進行時序分析;而在布局布線后,也要對實際布局布線的功能塊延時和實際布線延時進行靜態時序分析。從某種程序來講,靜態時序分析可以說是整個FPGA設計中最

2019-05-03 08:00:00

映射后需要對一個設計的實際功能塊的延時和估計的布線延時進行時序分析;而在布局布線后,也要對實際布局布線的功能塊延時和實際布線延時進行靜態時序分析。從某種程序來講,靜態時序分析可以說是整個FPGA設計中最

2021-06-24 08:00:01

而又美好,那么我們這么多學費就沒白交哈~ 下面我們進入正題,今天我們講時序一、從靜態時序分析說起 我理解的靜態時序分析,就是我們在不加激勵的情況下,通過對電路進行時序的延遲計算,預計電路的工作流

2015-03-31 10:20:00

時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎常用時序概念QuartusII中的時序分析報告

設置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 本文通過對源同步時序公式的推導,結合對SPECCTRAQuest 時序仿真方法的分析,推導出了使用SPECCTRAQuest 進行時序仿真時的計算公式,并對公式的使用進行了說明。 通常我們在時序仿真中

2011-07-12 10:05:52 97

97 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1168

1168 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 在進行時序分析時片上工藝差別通常會導致嚴重的“時鐘悲觀效應”。這種問題可以通過CPR(Clock Pessimism Reduction)操作來恢復.然而經常有用戶咨詢我們說在他們的設計中CPR操作

2017-02-07 18:04:11 1357

1357 時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

fpga時序收斂

2017-03-01 13:13:34 23

23 FPGA,即現場可編程門陣列,它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。對于時序如何用FPGA來分析與設計,本文將詳細介紹。

2017-06-30 15:09:36 28

28 一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

控制器,在介紹控制器的邏輯結構的基礎上,對FPGA與SDRAM間數據通信進行了時序分析,實現SDRAM 帶有自動預充電突發讀寫和非自動預充電整頁讀寫。

2017-11-18 12:42:03 2054

2054

提出了由于FPGA容量的攀升和配置時間的加長,采用常規設計會導致系統功能失效的觀點。通過詳細描述Xilinx FPGA各種配置方式及其在電路設計中的優缺點,深入分析了FPGA上電時的配置步驟和工作

2017-11-22 07:18:34 6221

6221

作為賽靈思用戶論壇的定期訪客(見 ),我注意到新用戶往往對時序收斂以及如何使用時序約束來達到時序收斂感到困惑。為幫助 FPGA設計新手實現時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實現

2017-11-24 19:37:55 4903

4903

FPGA的設計與高速接口技術可以幫助你滿足今天的市場要求,但也提出了一些有趣的設計挑戰。為了確保存儲器接口的數據傳輸準確,在超過200兆赫茲以上,進行時序分析將發揮更突出的作用,以識別和解決系統運行

2017-11-25 01:06:01 982

982

FPGA時序布局算法TMDCP。將退火過程分發至多線程執行,利用TM機制保證共享內存訪問的合法性,并將改進的時序優化算法嵌入到事務中并發執行。測試結果表明,與通用布局布線工具相比,8線程下的TMDCP算法在總線長僅有輕微增加的情況下,關鍵

2018-02-26 10:09:04 0

0 從最近一段時間工作和學習的成果中,我總結了如下幾種進行時序約束的方法。按照從易到難的順序排列如下:

2018-08-07 14:14:00 13907

13907

時序分析在FPGA設計中是分析工程很重要的手段,時序分析的原理和相關的公式小編在這里不再介紹,這篇文章是小編在練習Vivado軟件時序分析的筆記,小編這里使用的是18.1版本的Vivado。 這次

2019-09-15 16:38:00 5787

5787

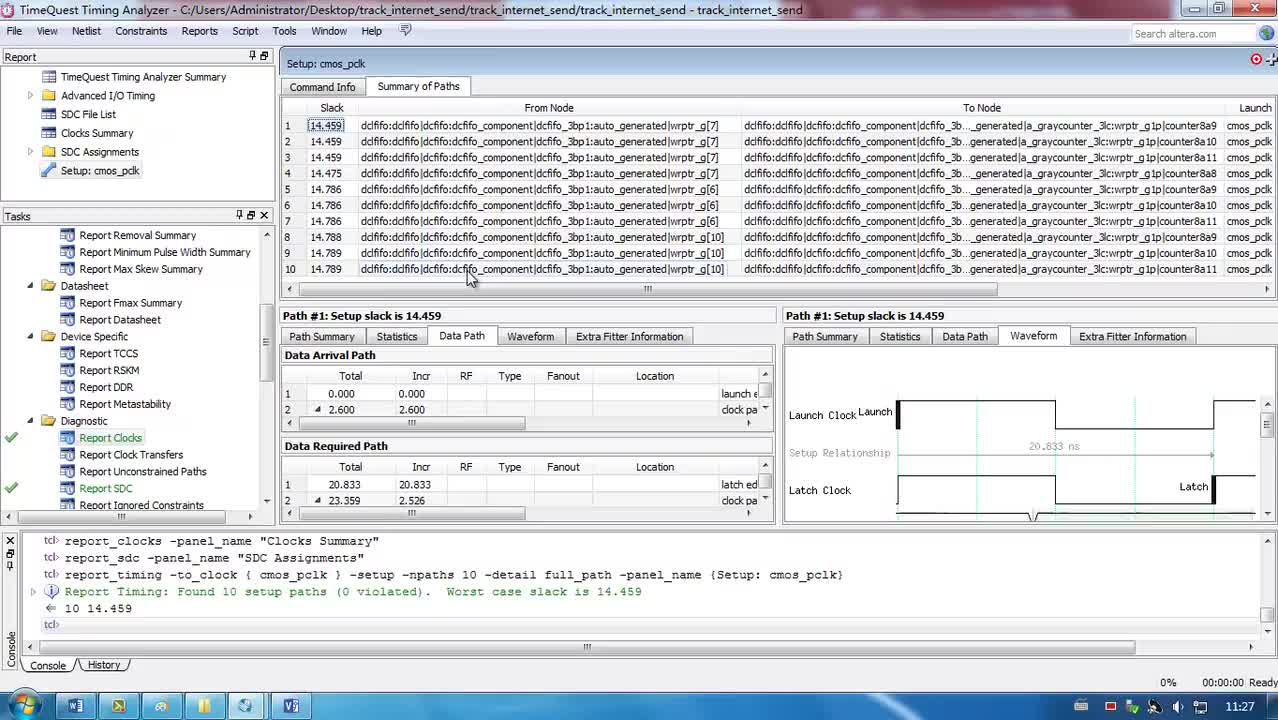

TimeQuest時序約束是作用在門級網表上的,因此在進行時序約束前應該首先編譯一邊工程,之后進行時序約束并再次編譯進行時序分析,直至無時序錯誤為止,之后燒寫工程下板子。

2019-12-19 07:03:00 1151

1151

FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2019-12-23 07:01:00 1894

1894

TimeQuest時序約束是作用在門級網表上的,因此在進行時序約束前應該首先編譯一邊工程,之后進行時序約束并再次編譯進行時序分析,直至無時序錯誤為止,之后燒寫工程下板子。

2019-12-12 07:06:00 1372

1372

靜態時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設計的要求,根據電路網表的拓撲結構,計算并檢查電路中每一個DFF(觸發器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。

2019-09-01 10:45:27 2942

2942

上面我們講的都是xdc文件的方式進行時序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進行時序約束:時序約束編輯器(Edit Timing Constraints )和時序約束向導(Constraints Wizard)。兩者都可以在綜合或實現后的Design中打開。

2020-03-08 17:17:00 19067

19067

靜態時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態時序分析,靜態時序分析不需要測試矢量,而是直接對芯片的時序進行約束,然后通過時序分析工具給出

2020-11-11 08:00:00 58

58 本文檔的主要內容詳細介紹的是華為FPGA硬件的靜態時序分析與邏輯設計包括了:靜態時序分析一概念與流程,靜態時序分析一時序路徑,靜態時序分析一分析工具

2020-12-21 17:10:54 18

18 時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 任何學FPGA的人都跑不掉的一個問題就是進行靜態時序分析。靜態時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種很簡單的解讀辦法,可以看透它的本質,而且不需要再記復雜的公式了。

2021-01-12 17:48:08 19

19 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束利序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 AN-1080: 利用簡單時序控制器ADM108x進行上電和關斷時序控制

2021-03-21 00:41:43 6

6 電子發燒友網為你提供時序分析是FPGA如何設計?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-15 08:51:20 12

12 時序沖突的概率變大以及電路的穩定性降低,為此必須進行時序、面積和負載等多方面的約束。

2021-06-15 11:24:05 2874

2874

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2095

2095 左邊的電路圖是需要分析的電路,我們的目的是要對此電路進行時序分析,那首先要找到該電路需要分析的時序路徑,既然找路徑,那找到時序分析的起點與終點即可。

2022-05-04 17:13:00 1827

1827 時序約束是我們對FPGA設計的要求和期望,例如,我們希望FPGA設計可以工作在多快的時鐘頻率下等等。因此,在時序分析工具開始對我們的FPGA設計進行時序分析前,我們必須為其提供相關的時序約束信息

2022-12-28 15:18:38 1891

1891 任何學FPGA的人都跑不掉的一個問題就是進行靜態時序分析。靜態時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內容又不那么一致,為了徹底解決這個問題,終于找到了一種很簡單的解讀辦法,可以看透

2023-03-14 19:10:03 443

443 FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-04-27 10:08:22 768

768 任何學FPGA的人都跑不掉的一個問題就是進行靜態時序分析。靜態時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種很簡單的解讀辦法,可以看透它的本質,而且不需要再記復雜的公式了。

2023-05-29 10:24:29 348

348

STA(Static Timing Analysis,即靜態時序分析)在實際FPGA設計過程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

FPGA高級時序綜合教程

2023-08-07 16:07:55 3

3 在離線分析的過程中,可能會對兩個不同的信號進行時間上同步,本文以舉例的形式介紹,如何使用?CANape?或者?vSignalyzer?對不同的信號進行時間同步。

2023-10-13 12:28:59 1155

1155

電子發燒友網站提供《分立式元件對電源進行時序控制的優缺點.pdf》資料免費下載

2023-11-29 11:36:07 0

0

電子發燒友App

電子發燒友App

評論