本文主要使用了Cadence公司的時域分析工具對DDR3設計進行量化分析,介紹了影響信號完整性的主要因素對DDR3進行時序分析,通過分析結果進行改進及優化設計,提升信號質量使其可靠性和安全性大大提高。##時序分析。##PCB設計。

2014-07-24 11:11:21 4410

4410

本實驗為后續使用DDR3內存的實驗做鋪墊,通過循環讀寫DDR3內存,了解其工作原理和DDR3控制器的寫法,由于DDR3控制復雜,控制器的編寫難度高,這里筆者介紹采用第三方的DDR3 IP控制器情況下的應用,是后續音頻、視頻等需要用到DDR3實驗的基礎。

2021-02-05 13:27:00 8224

8224

? 2022年4月20日,中國蘇州訊?—— 全球半導體存儲解決方案領導廠商華邦電子今日宣布,將持續供應DDR3產品,為客戶帶來超高速的性能表現。 ? 華邦的?1.35V DDR3 產品在?x8

2022-04-20 16:04:03 2554

2554

同樣的GEL在自制板上做DDR3初始化也OK(驗證過,DDR3讀寫都正常,數據沒有自跳變),可是問題來我,為什么我用同樣的KEYSTONE DDR3 INIT在自制板上做DDR3初始化老是不成功,老是

2019-01-08 10:19:00

。2.8. 復位注意事項DDR3控制器可以通過硬件復位和軟件復位。硬件復位會重置狀態機,FIFOS,和內部寄存器。軟件復位只會復位狀態機和FIFOS。軟件復位不會復位除中斷寄存器以外的寄存器。當復位執行

2018-01-18 22:04:33

的6678到芯片相應拐角的長度?還有就是不知道這個DQS_ECC和CK_ECC應該怎么看呢?下面是我通過表格計算出來的ddr3初始化的值。

ps:寫個簡單的測試程序,發現寫不進去數,我知道這肯定是我配置有問題,但就是不知道該怎么進行查找,還請專家幫忙解答下,謝謝了

2018-06-21 17:25:42

數據從L2傳遞到DDR3中比數據從DDR3傳遞到L2中運行周期大很多,將近后者的7倍

實驗三:把L2SRAM中的數據存儲到DDR3中

x_data 存儲在L2SRAMZ中

y_dat存儲在DDR3中

2018-06-21 17:19:51

嗨,我是FPGA領域的新手。現在我正在使用Genesys2。我必須控制DDR3內存。我在Digilent網站上找到了一些使用micrlaze處理器的DDR3示例。但是,在我的情況下,我不必

2019-05-05 15:29:38

? ?在調試335x的DDR3時,用的是CCS,非操作系統調試。

? ?按TI給的AM335x——StarterKit.gel,這個文件導入到CCS,debug的時候,DDR3可以驅動,讀寫正常。按

2018-06-21 10:59:20

江山科技最新推出JS-9500內存測試儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條, 內存

2009-02-10 22:50:27

江山科技最新推出JS-9500內存測試儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條, 內存

2009-02-10 22:55:45

江山科技最新推出JS-9500內存測試儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條,筆記本

2009-08-17 23:00:19

江山科技最新推出JS-9500內存檢測儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條, 內存

2009-02-10 22:53:43

江山科技最新推出JS-9500內存檢測儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條, 內存

2009-03-12 16:05:56

江山科技最新推出JS-9500內存檢測儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條,筆記本

2009-08-17 22:58:49

概述: JS-9300A內存檢測儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測

2009-03-13 15:46:57

了極大的挑戰。 本文主要使用了Cadence公司的時域分析工具對DDR3設計進行量化分析,介紹了影響信號完整性的主要因素對DDR3進行時序分析,通過分析結果進行改進及優化設計,提升信號質量使其可靠性

2014-12-15 14:17:46

通過DDR3內存名MT41J128M16-16Meg*16*8Banks通過命名怎樣算出內存的大小?

2017-06-15 21:19:11

DDR3(double-data-rate three synchronous dynamic random accessmemory)是應用在計算機及電子產品領域的一種高帶寬并行數據總線。DDR3 在 DDR2

2019-05-22 08:36:26

DDR3基礎詳解最近在IMX6平臺下做DDR3的測試接口開發,以前在學習嵌入式時,用的是官方源碼,沒有做過多的研究。此時需要仔細研究DDR3的引腳與時序,此篇是我在學習DDR3做的歸納與總結,其中有

2021-07-28 09:02:52

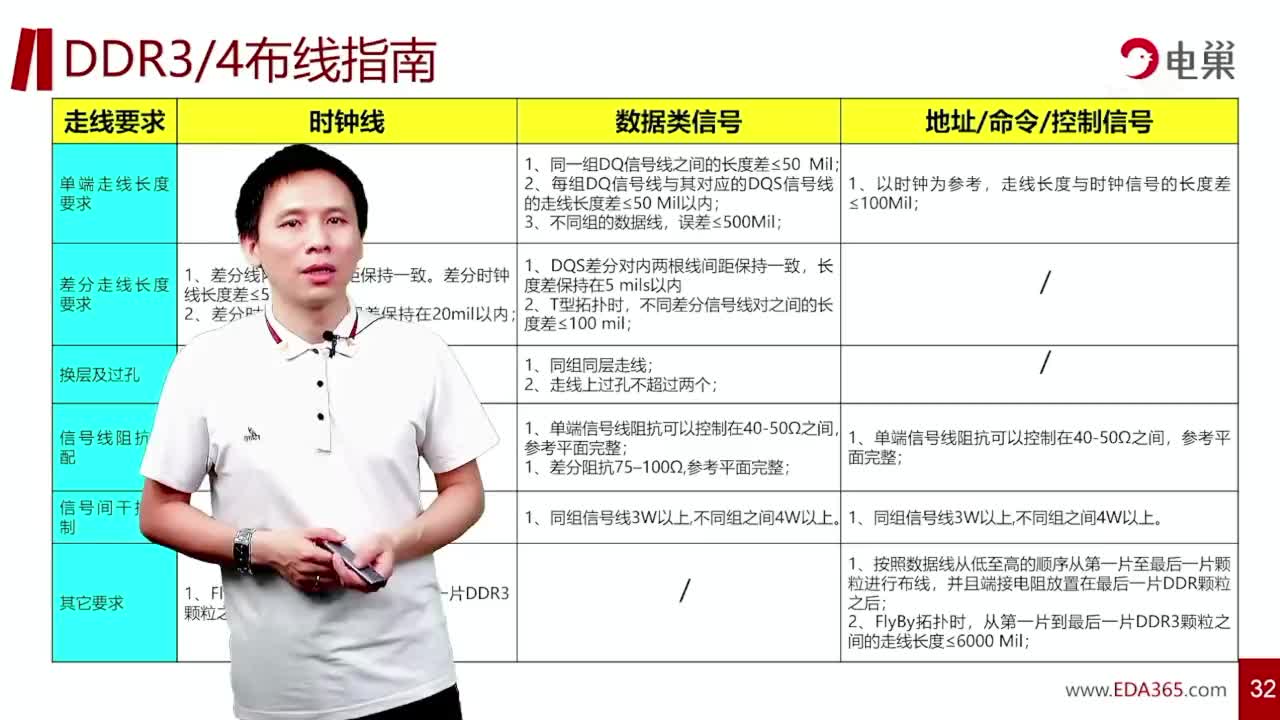

共享交流一下,DDR3布線技巧

2016-01-08 08:17:53

大家好,最近在學習DDR3的讀寫,用的是Spartan-6的 x16,DDR3型號MT41J64M16,在進行write時,地址總是出現兩遍,第一遍后面出現data=XXXX,感覺像是data

2018-06-28 19:11:52

CPU的DDR3總線只連了一片DDR3,也沒有復用總線將DDR3的CS直接拉到地的話,DDR3初始化不成功所以說DDR3的CS信號是通過沿采樣的嗎,電平采樣不行?無法理解啊還是有其他方面原因

2016-11-25 09:41:36

DDR3芯片讀寫控制及調試總結,1. 器件選型及原理圖設計(1) 由于是直接購買現成的開發板作為項目前期開發調試使用,故DDR3芯片已板載,其型號為MT41J256M16HA-125,美光公司生產的4Gb容量DDR3芯片。采...

2021-07-22 08:33:54

本帖最后由 一只耳朵怪 于 2018-6-21 15:24 編輯

各位好!關于DDR3,之前有小結過如果進行DDR3的SW leveling和進行EMIF4寄存器的配置。但是調試時,如果進行DDR3的問題定位,現小結一下,附上相關文檔。如有相關問題,可在樓下跟帖討論。謝謝!

2018-06-21 04:01:01

專家,你好,想節省代碼設計的周期,請問是否可以提供6670的DDR3的驅動例子?謝謝

2018-06-21 13:34:52

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

;?增加ACT_n控制指令為增強數據讀寫可靠性增加的變更點主要有:?DBI;?Error Detection;1 電源變化DDR3與DDR4的96 Ball封裝pin定義...

2021-11-12 08:07:07

先用spartan6對ddr3進行讀寫操作,想知道ddr3一般上電多久后可對其進行讀寫操作?求大神解答,感謝!

2014-06-14 16:13:45

#tb_frame_buffer.ddr3_model_c3_inst.cmd_task時間754401251.0 ps警告:在CKE變為活動狀態之前,RST_N變為非活動狀態后需要500 us。ddr3 clk為400MHz,DRP

2019-07-08 08:44:42

? ? ? BeagleBone的參考設計中,DDR3設計是DDR3 Device without VTT Termination。而其他的AM335X的參考設計都是有VTT Termination

2018-06-21 03:05:42

因為工作的需要,最近做了下DDR3 IP核的讀寫仿真,仿真過程中DDR寫數據正常,但在對DDR讀取數據時出現以下的情況:1.MEM_DQ、MEM_DQS、MEM_DQSN始終為高阻態

2019-12-26 23:11:56

FPGA如何對引腳進行分塊?是由VCC的電壓不同進行自行設計分塊?還是每個塊的引腳都是固定的?在進行DDR3與FPGA的硬件連接時,由FPGA的芯片手冊得采用SSTL_15電壓標準,即VDDQ

2021-11-29 16:10:48

本次發布 Gowin DDR3參考設計。Gowin DDR3 參考設計可在高云官網下載,參考設計可用于仿真,實例化加插用戶設計后的總綜合,總布局布線。

2022-10-08 08:00:34

我們參照TMDXEVM6678L開發板設計了一塊FPGA加DSP架構的處理板,由FPGA完成6678的boot啟動任務。在進行程序燒錄調試的過程中,出現了以下問題。未使用到DDR3內存部分的簡單

2019-10-29 17:56:48

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3資料。

2016-05-27 16:39:58

DDR3的IP核配置完畢后,產生了好多文件,請問如何調用這些文件實現DDR3的讀寫呢?看了一些文章,說是要等到local_init_done為高電平后,才能進行讀寫操作。請問DDR3的控制命令如

2016-01-14 18:15:19

看完保證你會做DDR3的仿真

2015-09-18 14:33:11

例程和豐富的DDR3的IP core相關資料。 本視頻教程利用Combat開發板進行講解,視頻課程注重基礎知識和設計思路的講解,幫助用戶快速了解Gowin的DDR3的 IP core的使用。

2021-05-06 15:34:33

穩定的工作。項目名稱:DDR3。 具體要求:實現DDR3數據的讀寫。 系統設計:實現過程:1.新建工程之后打開Create BlockDesign,并修改Design name。2.按照系統設計依次添加

2021-07-30 11:23:45

& 14用于DDR3內存接口,但由于我使用的是3.3V的fash存儲器IC,我必須使用bank 14進行閃存存儲器接口。原因是需要的資源僅在Bank 14中可用.DDR3存儲器連接的bank應該工作在

2020-04-17 07:54:29

并不會注意一些數字上的差異,如DDR3和DDr2,或許大多數人都會追求時髦選擇DDR3,但是你真的了解DDR2與DDR3的區別嗎?作為消費者,其實我們可主宰自己的命運,用知識的武器捍衛自己的選擇。下面

2011-12-13 11:29:47

的 DDR3/DDR3L 設計經過優化的布局不需要 VTT 終端兩個 4 Gbit DDR3/DDR3L 存儲器高達 400 MHz 的時鐘(DDR-800 數據速率)完整的子系統參考,具有原理圖、BOM、設計文件和硬件用戶指南,在專為測試和驗證而開發的完全組裝的板上實施。`

2015-04-03 17:14:40

的 DDR3/DDR3L 設計經過優化的布局不需要 VTT 終端兩個 4 Gbit DDR3/DDR3L 存儲器高達 400 MHz 的時鐘(DDR-800 數據速率)完整的子系統參考,具有原理圖、BOM、設計文件和硬件用戶指南,在專為測試和驗證而開發的完全組裝的板上實施。

2018-09-26 08:53:27

1.項目的板子上要用到兩顆DDR3芯片,板子打樣回來可能要進行測試,對示波器的采樣率可能會有比較高的要求,不知道大家在設計中用的是什么示波器,最好有具體型號2.既然說到DDR3了,有好些個問題都想

2017-10-26 09:54:13

我是一名labview FPGA程序員,使用的是NI 7975 fpga模塊,它具有kintex 7 fpga。該模塊具有外部DDR3 DRAM 0f 2GB以及kintex 7 fpga資源。數據應該從芯片到芯片之間會有多少延遲?這是DDR3 DRAM雙端口(同時讀寫操作可能??)???

2020-05-20 14:42:11

,存儲器控制器讀取數據并將其傳到視頻處理器。視頻處理器對視頻數據進行格式化和壓縮,并通過DDR3存儲器控制器寫回存儲器。當一個視頻數據包全部處理完畢,并準備通過PCI Express接口進行傳輸,DDR3

2019-05-27 05:00:02

SDRAM芯片。DDR3工作頻率為500MHz,經測試其可對3GB/s的數據流進行穩定緩存。4 結束語本文對DDR3讀寫狀態機進行了設計與優化,并對DDR3在不同讀寫方式下的帶寬利用率進行了測試與分析,提出

2018-08-02 09:34:58

同一時刻發起DDR3的讀寫請求,其中1~4通道進行DDR3的寫請求,5、6通道進行DDR3的讀請求,狀態機按照消息優先級的順序依次進行狀態跳轉完成處理,最后將數據分別返回到相應通道中,ChipScope

2018-08-02 09:32:45

控制;DDR3用戶接口仲裁控制模塊將圖形和視頻分別進行中斷處理,提高了并行速度,同時簡化仲裁控制;幀地址控制模塊將DDR3空間進行劃分,同時控制幀地址的切換。經過分析,本文將圖形和視頻中斷分開處理,簡化多端口讀寫DDR3的復雜度,提高并行處理速度。

2018-08-02 11:23:24

適用于該背景的控制狀態機,并對控制時序作了詳盡的分析。系統測試結果表明,該設計滿足大容量數據的高速率存儲和讀取要求。一、引言隨著軟件無線電[1]思想的提出和FPGA技術[2]的不斷發展,高速實時

2018-08-30 09:59:01

基于Xilinx MIS IP的DDR3讀寫User Interface解析特權同學,版權所有,轉載請注明出處參考文檔:ug586_7Series_MIS.pdf1. Command時序首先,關于

2016-10-13 15:18:27

,ddr3的帶寬利用率也只有20%-30%左右。這里就覺得比較糾結。burst length太大,frame buffer的輸出端當要對輸入的視頻幀進行截取一部分的時候會變相降低DDR3帶寬利用率,這樣

2015-08-27 14:47:57

由于系統帶寬不斷的增加,因此針對更高的速度和性能,設計人員對存儲技術進行了優化。下一代雙數據速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的優勢。這些

2019-08-09 07:42:01

自建Spartan6 DDR3仿真平臺

2019-08-01 06:08:47

激光器,AXI互連,DDR3和我們的IP模塊,我們可以進行功能級仿真。但是在得到bitfile之后,我們已經編寫了Kintex705評估板,我們沒有得到init_calib_complete信號,我們

2020-08-05 13:45:44

怎樣對DDR3芯片進行讀寫控制呢?如何對DDR3芯片進行調試?

2021-08-12 06:26:33

一、實驗要求

生成 DDR3 IP 官方例程,實現 DDR3 的讀寫控制,了解其工作原理和用戶接口。

二、DDR3 控制器簡介

PGL50H 為用戶提供一套完整的 DDR memory 控制器

2023-05-31 17:45:39

數據速率 800Mbps

一、實驗要求

生成 DDR3 IP 官方例程,實現 DDR3 的讀寫控制,了解其工作原理和用戶接口。

二、DDR3 控制器簡介

GL50H 為用戶提供一套完整的 DDR

2023-05-19 14:28:45

本帖最后由 一只耳朵怪 于 2018-6-20 11:34 編輯

各位專家好!剛剛學習DSP,還沒有入門。實驗室購買了TMS320C6678開發板。請問:1、為什么DSP需要外接DDR3?2

2018-06-20 00:40:57

邏輯的開發;2. 根據多種通信協議及系統需求,優化或定義設計目標和系統架構;3. 根據需求,定義和設計模塊結構,進行RTL 設計/約束/驗證/綜合/時序分析/DFT等;4. 制定測試計劃,協助完成驗證/測試Check List等芯片測試工作;5. 搭建FPGA平臺進行測試驗證。

2017-11-13 14:46:14

和PL端的Master IP核,共同訪問操作一個Slave端即DDR3 Controllor。 本次實驗就是構建一個這樣的驗證系統。當然了在真正的工程系統中,還需要設計良好的讀寫同步,防止競爭沖突,這就屬于系統設計層面的了,本實驗依靠按鈕觸發有用戶來進行讀寫同步。

2017-09-15 16:35:01 24

24 構建SoC系統,畢竟是需要實現PS和PL間的數據交互,如果PS與PL端進行數據交互,可以直接設計PL端為從機,PS端向PL端的reg寫入數據即可,本節研究如何再實現PL端對DDR3的讀寫操作。

2017-09-18 11:08:55 23

23 DDR3是目前DDR的主流產品,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。最開始的DDR, 芯片采用的是TSOP封裝,管腳露在芯片兩側的,測試起來相當方便;但是,DDRII和III就不一樣了,

2017-11-06 13:44:10 8454

8454

雖然新一代電腦/智能手機用上了DDR4內存,但以往的產品大多還是用的DDR3內存,因此DDR3依舊是主流,DDR4今后將逐漸取代DDR3,成為新的主流,下面我們再來看看DDR4和DDR3內存都有哪些區別。相比上一代DDR3,新一代DDR4內存主要有以下幾項核心改變:

2017-11-08 15:42:23 30895

30895 讀寫操作。DDR3用戶接口仲裁控制模塊將中斷請求分成多個子請求,實現視頻中斷和圖形中斷的并行處理。幀地址控制模塊確保當前輸出幀輸出的是最新寫滿的幀。

2017-11-18 18:51:25 6412

6412

、QDR,當然,還有DDR3 UDIMM插槽。因此,我們所要做的就是通過Quartus軟件來下載一個簡單設計,FPGA進行簡單的數據寫入并讀回。

我們還采用了一些測試設備來幫助進行演示,Nexus

2018-06-22 05:00:00 8250

8250 我們通過Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封裝,速度等級等信息。

2019-03-03 11:04:15 1909

1909

本文檔的主要內容詳細介紹的是DDR和DDR2與DDR3的設計資料總結包括了:一、DDR的布線分析與設計,二、DDR電路的信號完整性,三、DDR Layout Guide,四、DDR設計建議,六、DDR design checklist,七、DDR信號完整性

2020-05-29 08:00:00 0

0 從成本的角度來看,DDR3也許的確要比DDR4低一些,所以從這個角度可以講通。

2020-09-08 16:28:23 4062

4062 通過之前的學習,CPU可以讀寫DDR3了,PL端的Master IP也可以讀寫DDR3了,那二者就可以以DDR3為紐帶,實現大批量數據交互傳輸。

2020-07-27 08:00:00 16

16 這篇文章我們講一下Virtex7上DDR3的測試例程,Vivado也提供了一個DDR的example,但卻是純Verilog代碼,比較復雜,這里我們把DDR3的MIG的IP Core掛在Microblaze下,用很簡單的程序就可以進行DDR3的測試。

2021-05-02 09:05:00 2979

2979

POD模式;? 增加ACT_n控制指令為增強數據讀寫可靠性增加的變更點主要有:? DBI;? Error Detection;1 電源變化DDR3與DDR4的96 Ball封裝pin定義...

2021-11-06 20:36:00 28

28 ??這篇文章我們講一下Virtex7上DDR3的測試例程,Vivado也提供了一個DDR的example,但卻是純Verilog代碼,比較復雜,這里我們把DDR3的MIG的IP Core掛在Microblaze下,用很簡單的程序就可以進行DDR3的測試。

2022-08-16 10:28:58 1241

1241 一、DDR3簡介 ? ? ? ? DDR3全稱double-data-rate 3 synchronous dynamic RAM,即第三代雙倍速率同步動態隨機存儲器。所謂同步,是指DDR3數據

2022-12-21 18:30:05 1915

1915 DDR3的速度較高,如果控制芯片封裝較大,則不同pin腳對應的時延差異較大,必須進行pin delay時序補償。

2023-07-04 09:25:38 312

312

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1896

1896

本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現讀寫操作。

2023-09-01 16:23:19 743

743

摘要:本文將對DDR3和DDR4兩種內存技術進行詳細的比較,分析它們的技術特性、性能差異以及適用場景。通過對比這兩種內存技術,為讀者在購買和使用內存產品時提供參考依據。

2023-09-27 17:42:10 1089

1089 DDR3是2007年推出的,預計2022年DDR3的市場份額將降至8%或以下。但原理都是一樣的,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。

2023-10-18 16:03:56 517

517

DDR4和DDR3內存都有哪些區別? 隨著計算機的日益發展,內存也越來越重要。DDR3和DDR4是兩種用于計算機內存的標準。隨著DDR4內存的逐漸普及,更多的人開始對兩者有了更多的關注。 DDR3

2023-10-30 09:22:00 3895

3895

電子發燒友App

電子發燒友App

評論