雖然示波器不是對硬件要求最高的儀器,鑒于示波器是眾多工程師最熟悉也是測試儀器細分市場最大的單臺儀器,所以我們采訪了全球能將示波器帶寬做到GHz級別廠商中的幾家代表,從示波器的硬件分析入手,帶大家一起了解示波器的核心設計單元。

帶寬,采樣率和存儲深度,是決定一臺示波器市場價值最直觀的三大特性,其中帶寬是最明顯能體現示波器的性能的指標,采樣率的數值和帶寬有著一定的聯系,而這兩個數值則直接關系到示波器的最終售價,其數值也基本都是由模擬單元的硬件性能決定的。

示波器的架構經歷了幾十年的沉淀,特別是最近二十年數字示波器的高速發展,已經基本趨于穩定,普源精電(RIGOL)副總裁邢飛介紹,當代數字示波器的基本組成主要包括:模擬前端(負責信號調理)-》 模數轉換器 (調理后信號數字化)-》 數據采集/存儲/信號處理 -》 顯示與人機接口。其中前兩個部分決定了示波器絕大部分性能指標,也是示波器的核心所在。

帶寬與模擬前端

帶寬,是選擇示波器時最基本的參數,從2004年的30GHz問世,到45GHz的出現,這期間等待了5年,而到60GHz示波器的出現只有短短的3年,而最近的12個月里,示波器三強紛紛更新了自己的最頂級配置示波器,一切仿佛對2002-2004年示波器性能軍備競賽的翻拍。

力科從2004年開始擁有了多年的數字示波器帶寬性能之最的皇冠被安捷倫占據,安捷倫的Infiniium 90000Q最高帶寬做到了63GHz,超過了力科LabMaster10Zi的60GHz。當兩家主要競爭對手都推出60GHz級別的示波器之后,下一步,我們期待泰克科技如何應對。

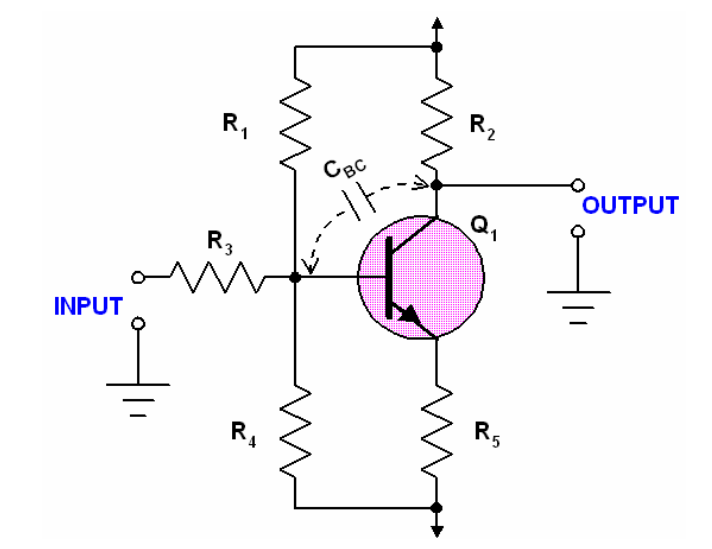

決定帶寬的關鍵是示波器的模擬前端,包括衰減器, 放大器和相關電路,是被測信號進入示波器的大門,示波器的測試信號帶寬很多情況下都是由模擬前端的帶寬決定的,也就是直接影響了示波器的本底噪聲和量程。模擬前端的設計工作在示波器的硬件設計工作當中,實際上占據了一半以上的工作量,并且在很大程度上最終決定了示波器的硬件性能。

對于模擬前端來說,其影響示波器的主要性能指標包括:

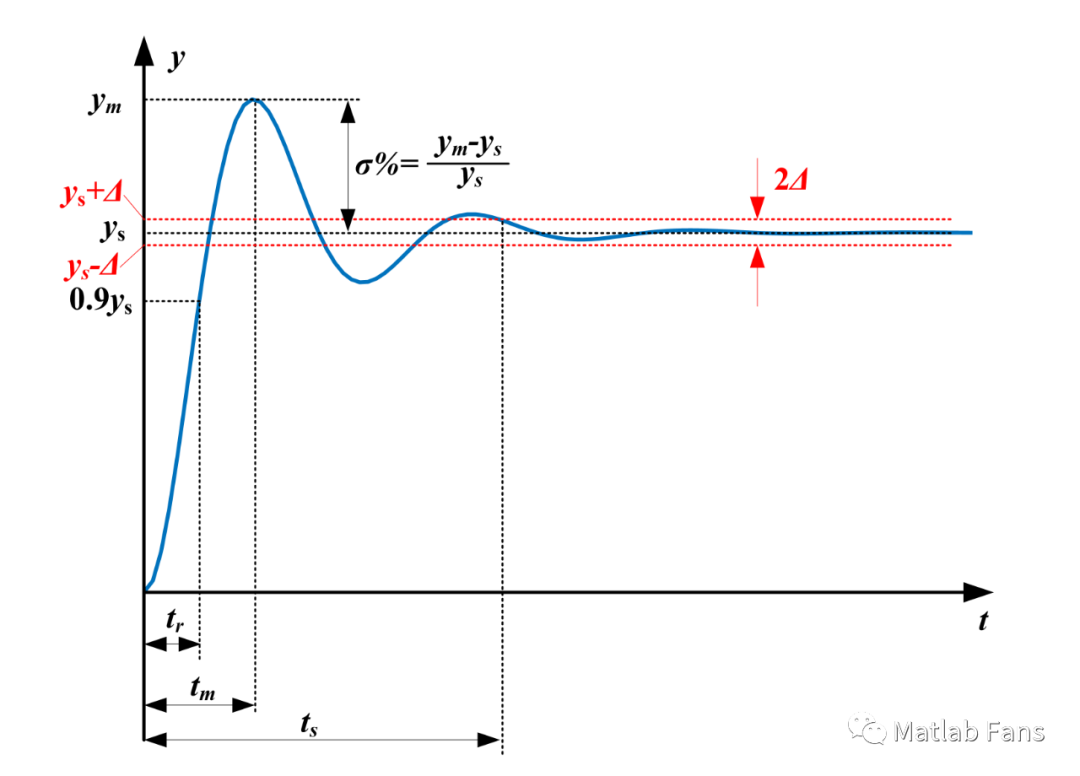

● 模擬帶寬,包括對被測信號幅頻響應特性,在時域上表現為上升時間指標和過沖性能指標;

● 輸入信號幅度動態范圍(非數字處理的最小垂直靈敏度到最大垂直靈敏度的范圍);

● 直流增益精度和偏移精度兩個指標的初始誤差特性和溫度漂移特性;

● 輸入阻抗特性(電阻并聯寄生電容)影響在帶探頭或不帶探頭情況下對被測電路的影響。

如果給示波器的模擬前端設計在整個的硬件設計中的重要地位做一個形象的比喻,模擬前端的作用類似于照相機的鏡頭。很多攝影發燒友在使用單反相機,一個很重要的原因是單反相機的鏡頭有更好的光學特性。類似的道理,模擬前端對輸入信號進行衰減放大和信號調理,系統噪聲也會被放大。如果示波器的模擬前端設計差,系統噪聲大,希望測試的微小信號將無法捕獲;如果在頻域觀測,這些噪聲將使信噪比下降,底噪升高。如果信號通路間的隔離度不夠,其他通道的信號將對被測信號造成較大的干擾。同時,模擬前端的線性度和抗飽和能力也十分重要。

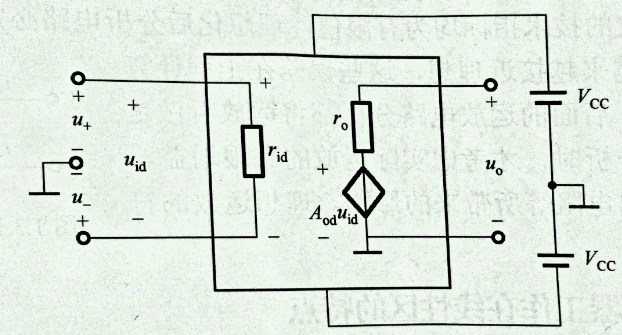

在數字示波器的模擬前端設計過程當中,放大器是模擬前端設計的核心部件之一,邢飛介紹,通過特別的放大器器件選用和設計,RIGOL產品里的放大器既能夠保證示波器的高帶寬特性,又能夠保證示波器的高直流增益精度特性。對于混合信號產品,其數字通道的放大器設計具有有別于模擬通道放大器設計的特殊技術點,除了保持與模擬通道類似的高帶寬特性之外,對于信號調理過程中的幅頻響應特性要求較高,以降低時域過沖,避免數字通道對實際被測信號的采集和現實錯誤。

作為示波器市場近年來殺入的黑馬,羅德與施瓦茨(R&S)中國區示波器業務發展經理焦保春分析,在該公司示波器產品在模擬前端設計中,采用了大量的R&S在射頻測試領域的成熟技術,將射頻設計融合到模擬設計中。這樣做帶來最直觀的好處是大大降低的信號通路的噪聲。在最低的信號量程條件下(1mV/div),示波器依然能夠保持極低的噪聲水平,其信號噪聲有效值為同類產品的1/4以下。通道間的高隔離度,特別是對高頻信號隔離度,也是射頻設計應用的范例。

當然,在高端示波器中,帶寬并非只在模擬前端中得以實現,還可以通過其他數字辦法實現更高帶寬,通常高端示波器帶寬有三種方法:一是前置放大電路直接實現;二是采用DSP拉伸帶寬;三是數字帶寬復用。泰克科技認為,三種方法各有各的優點。目前市場上用得比較多的是前置放大器直接實現和DSP拉伸帶寬技術。從使用上來說,硬件實現的帶寬使用數字技術較少,信號保真度較高,在使用上更為靈活,限制更少,頻響和噪聲譜更為平坦,支持等效采樣、欠采樣,可以允許信號超出屏幕外等,但成本相對較高;相比起來,數字技術則可能造成頻響或噪聲譜的起伏,在某些頻率上有效位低,同時數字技術要求實時采樣、不支持欠采樣,信號超出屏幕外會出現波形畸變,限制相對較多,對使用者的要求也較高。但數字技術實現的帶寬由于硬件成本較低,所以價格也相對較低,在犧牲一些性能的情況下,也為用戶提供了一個廉價的解決方案。總的來說,前置放大器技術和DSP為不同客戶的需求提供了不同選擇。

采樣率和模數轉換器

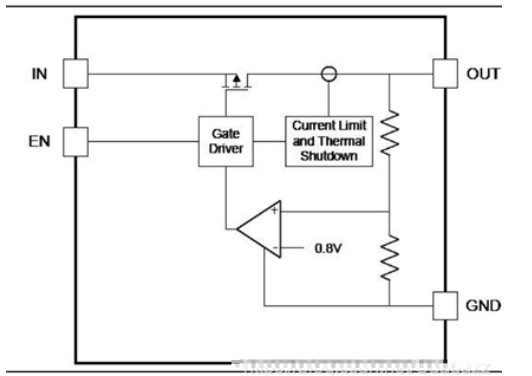

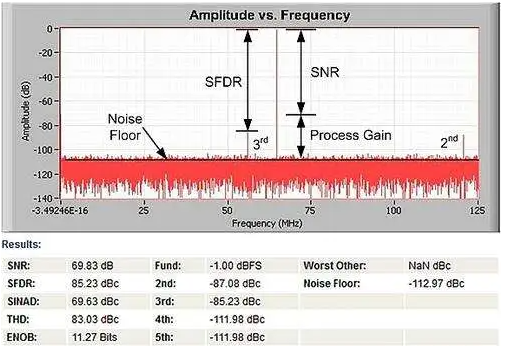

在示波器三大性能指標中,模擬前端決定了帶寬,那么模數轉換器(ADC)則是影響采樣率最重要的一環,ADC是數字示波器的核心器件,其中最關鍵的指標是采樣率和有效的ADC位數。ADC的采樣率直接決定了示波器的數字帶寬,也就是多高頻率的信號能夠有效地采集并顯示。

焦保春認為,A/D轉換器的采樣率不可能無限制提升,R&S擁有目前示波器市場中領先的單核10Gs/s采樣率A/D轉換器。為達到更高采樣率,很多公司采用了交織采樣技術,即用多顆低速A/D并行組合成高速多核的A/D。這種技術帶來的問題是信號的相位誤差。為修正此誤差,大多數示波器廠商使用的DSP修正技術。但DSP修正處理需要時間,這種修正使示波器的波形捕獲率降低。

示波器的采樣還包括采樣率的準確性,就是有效轉換位數(ENOB),常見示波器的A/D轉換器都是8位的。但在實際使用時,真正能夠發揮作用的轉換位數并不能達到8位。一些示波器在高帶寬是甚至會劣化到4位左右。這意味者用戶不可能使用這些示波器準確測量出信號的幅度信息。焦保春介紹R&S A/D轉換器的有效轉換位數可以高達7位以上。

邢飛坦承,模數轉換器主要決定了示波器的實時采樣率指標(例如RIGOL的DS6000,實現了最高5GSa/s的實時采樣率指標),并且在一定程度上,模數轉換器的采樣保持電路部分的滿功率帶寬(Full Power Bandwidth)也影響了產品最終能夠達到的最高帶寬。

超高采樣率需要多個ADC集成實現,安捷倫的90000Q示波器,160GS/s的采樣率是8個20GS/s芯片實現的,而每個20GS/s又是包含80個250MS/s的單芯片,這對時鐘信號的同步要求非常嚴格,特別是時鐘分配到每個ADC后,產生的相位差解決起來挑戰性很大,杜吉偉介紹,磷化銦工藝中,用波導電路設計其采樣時鐘,材料的特性決定其實際電路非常穩定,這是90000Q最困難的硬件設計。

研發是最大的挑戰

對于高端示波器產品,商業芯片出于成本和目標應用的考慮,往往在測試信號的帶寬和A/D轉換速度方面不能滿足高端示波器的要求。很多情況下,只有采用專用的ASIC設計才能解決這些問題。這也是高端示波器廠商不惜重金設立自己的ASIC設計團隊的原因。高性能的A/D芯片也代表了示波器廠商的尖端技術研發能力。

作為本土示波器廠商的杰出代表,RIGOL的邢飛認為,到了GHz級別的示波器,行業領先公司,無一例外都是采用專用芯片實現其頂級示波器產品的需求,甚至于已經無法找到能夠滿足其半導體工藝需求集成電路生產線,只能夠自行開發專用的集成電路工藝(例如磷化銦InP工藝)來滿足其對于高帶寬,高性能的要求。

安捷倫科技數字測試業務部大中國區市場經理杜吉偉介紹,安捷倫的高端示波器在模擬前端方面借鑒了很多射頻微波技術,包括三維的微電路設計、波導電路等,來保證數據在傳到模數轉換器之前已經經過精密的信號調理。安捷倫的高端示波器采用了磷化銦工藝、快膜三維封裝和氮化鋁散熱等技術,對示波器最后性能的領先性體現在本底噪聲和采樣時鐘抖動在同類產品中最低。磷化銦技術在光通信中廣泛應用,安捷倫將其應用到了示波器的模擬前端中,在20GHz以上的高頻示波器上有一定技術優勢,使用了磷化銦的包括前端放大器、觸發電路、采樣保持電路、探頭放大器。

目前可以預見的最主要的技術挑戰還是在器件電路設計方面,更進一步的,半導體工藝條件能夠達到的最高特性指標也會成為儀器產品性能指標提升的一個潛在制約因素。對于模擬前端和放大器設計,調和增益、帶寬和噪聲特性的問題;對于模數轉換器,實現超高速采樣保持,優化模數轉換器的轉換線性度并保持合理的功耗需求;這都是目前面臨的一些主要技術難點。

特別的,邢飛指出芯片工藝和材料決定了電路設計當中晶體管的最高截止頻率fT,并最終從物理條件上決定了所設計出電路可能實現的最大模擬帶寬。當然,模擬前端當中所用的放大器以及模數轉換器的最終特性與電路設計技巧和電路實現方式也是緊密相關的,但其物理條件會最終成為器件設計的極限限制。設計方面,RIGOL就非常注重不單單從器件數據手冊上標明的規格指標上,也從器件設計過程中所選用工藝的技術特點,去進行有針對性的產品選型和最終儀器產品設計。

模塊化的前端設計

隨著半導體集成工藝的進步和示波器性能的提升,單純的模擬前端芯片已經無法滿足最高性能示波器的需求,因此,各個廠商紛紛將前端模擬設計模塊化,實現更高集成和更高模擬性能。安捷倫科技的90000系列產品中,采用了全新的InP技術將模擬前端部分做成6個芯片,其中的幾個芯片以三維封裝的形式封裝成一個大的多芯片模塊(MCM),包括前置放大器,采樣保持和觸發功能單元,成為模擬前端的核心。

傳統上,高速信號采集和處理要求在示波器前端進行一系列連接和切換。信號從被測器件(DUT)輸送到示波器,通過同軸電纜傳送到PCB,經過球柵陣列(BGA)封裝,然后到達第一個集成電路(IC),進行模擬放大或衰減。然后信號輸出封裝,輸送到PCB上,然后發送到包含跟蹤和保持(T/H)集成電路的下一個封裝。只有在經過這一大串連接之后,信號才準備進行采樣、模數轉換和存儲。遺憾的是,這一系列連接和切換及之后多次反復會在采樣前劣化信號,進而損害示波器帶寬和信號保真度。

為克服這些問題,泰克在DPO/DSA70000D系列示波器采用定制設計、高度集成的前端多芯片模塊(MCM)。MCM把多種前端采集和處理組件,包括同軸電纜輸入連接器、前置放大器、跟蹤和保持芯片及端接電阻,合并到一個封裝中,因此在高速信號被采樣前永遠不會接觸PCB。

DPO/DSA70000D系列的定制前端MCM封裝把以前分散的大量組件集成在一起,包括:

● 兩塊前置放大器芯片;

● 一塊8路跟蹤和保持(T/H)芯片,帶模擬濾波器;

● 50歐姆端接電阻;

● 高性能100 GHz帶寬連接器;

● 到PCB的彈性接口。

由于它是一種自含式模塊,MCM減少了信號流經的連接數量及可能的錯誤來源數量。用戶不會再經過單芯片封裝和PCB層而發生多個信號跳變,那樣會在采樣前劣化信號保真度和示波器帶寬。通過使用高性能電纜,高速信號從示波器輸入直接傳送到MCM及內部的集成電路中。IBM的8HP技術是一種130納米(nm) SiGe雙極互補金屬氧化物半導體(BiCMOS)工藝,其性能是上一代工藝的兩倍。

寫在最后

隨著電子技術的快速發展,測試測量任務變得越來越困難。高性能應用,特別是要求芯片檢定、串行數據一致性測試、光學調制分析、雙倍數據速率(DDR)存儲器和寬帶RF檢驗的應用,需要以前不能實現的測試測量功能,包括把杰出的性能(帶寬和采樣率)和靈活性(端接電壓和靈敏度)結合起來,而又不會給信號保真度帶來負面影響。因此,市場的需求還會推動示波器不斷前行,以現有的半導體工藝和材料,帶寬突破100GHz似乎并不是什么難事,據說力科已經在實驗室里進行相應的研發,而安捷倫的InP MCM因為設計的原因,做到63GHz而不需改動硬件設計確實屬于幸運,下一步無疑要研發新一代MCM去實現更高性能的帶寬,提高帶寬只是市場需求是否能驅動投入高額研發費用的問題。

真正的挑戰還是在于采樣率的提升更為艱難,目前,力科和安捷倫都做到160GS/s,而現有的模數轉換器似乎最高的單顆也只能做到10GS/s,無疑,多個模數轉換器的集成是個非常嚴峻的挑戰,特別是在時鐘、校準算法,高速SRAM等方面解決起來非常困難,更重要的是,高頻信號基本都是微波信號,測試和捕獲起來與低頻信號完全不同,對整個采樣過程提出更大的挑戰。

責任編輯:Gt

電子發燒友App

電子發燒友App

評論