作者: Dr. Thorsten Sokoll, Dr. Ove Schimmer

寬帶阻抗受控系統的實現給中心電子構建部件——印刷電路板(PCB)的設計師、制造商和質量保證管理人員提出了艱巨的挑戰。這個挑戰不是源于缺乏電磁設計知識,而且源于PCB行業中巨大的價格壓力:也就是說,在開發人員看來完全適合GHz范圍時鐘速率的理想射頻(RF)基材幾乎沒有使用過。

與此相反,在整個基材中介電常數(DC)不均勻的低成本FR4材料倒是經常使用。另外,將核心材料和半固化片壓合成多層PCB經常導致幾何上的不勻稱,進一步增加了不確定性的來源。然而,為了滿足規定的容差,許多PCB制造商提供對線路阻抗的檢查服務,繼而要求額外的阻抗測試板。這些測試板通常位于PCB邊緣,因此只能部分代表分布在整個生產面板上的實際感興趣傳輸線的特性。在最壞的情況下,被測的測試板可能在規定范圍內,但實際感興趣的傳輸線卻不滿足要求。

阻抗波動經常是不可容忍的

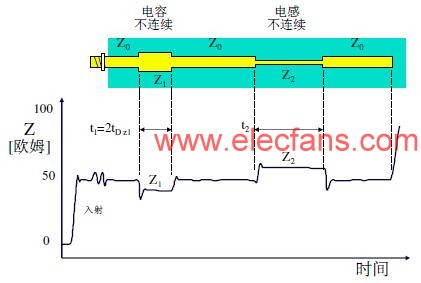

除了材料和生產工藝的特殊變化外,設計參數變化(比如層的改變,到GND平面、PCB邊界或其它傳輸線的距離太短)也時有發生,最終導致不可容忍的傳輸線阻抗波動。阻抗波動的后果是時鐘沿劣化,出現碼間干擾,進而造成不可接受的誤碼率,最終導致性能劣化甚至系統故障。

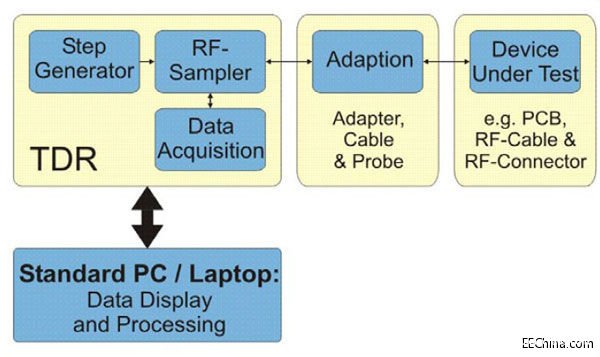

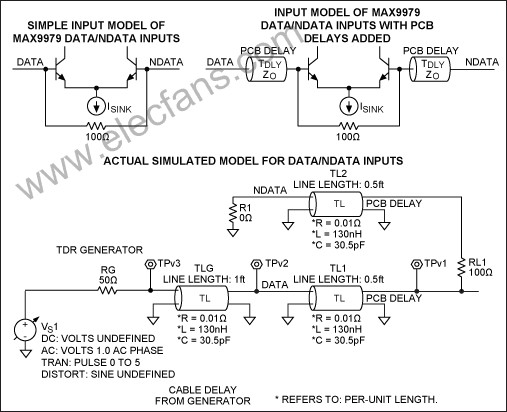

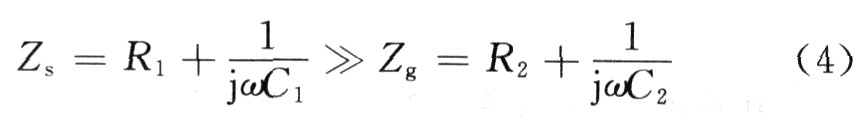

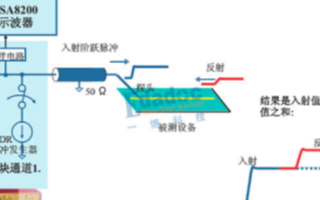

通過時域反射法(TDR)能以很高的精度確定線路阻抗。TDR技術從20世紀70年代就開始使用了,主要用于檢測地下或海底電纜中發生的故障。圖1顯示了基于TDR技術的阻抗測量裝置的框圖。TDR本身只包含一個電壓階躍發生器和帶數據采集單元的寬帶采樣器。

圖1:一個基于TDR技術的阻抗測量系統框圖。

基本的測量原理是這樣的:電壓發生器產生一個階躍信號,通過適配器、電纜和探針傳到待測設備(DUT)。當在待測設備的整個長度上時發生相互作用時,信號將經歷部分反射,并傳回檢測器,從而實現待測設備波形阻抗的空間測量。許多人從雷達應用中了解這種基本原理,因此也常把TDR稱為電纜雷達。

階躍信號的上升時間tr確定了空間分辨率,因此應該盡可能短(對于Sequid DTDR-65來說,tr≈ 65ps,因此空間分辨率大約為5mm)。發生器和采樣器(其模擬輸入帶寬至少是10GHz)之間的同步對于低噪聲工作(即抖動值只有幾個ps)來說至關重要。最理想的是使用“真正直通的”采樣器,不需要外部的信號分離器或耦合器。這種好處是顯而易見的,因為寬帶信號分離器通常是阻性的,會增加插損和噪聲。最后,TDR儀器還要有一個數據記錄單元,這個單元通常是用微處理器或FPGA實現。

高頻TDR設備正常情況下并不使用實時采樣技術,而是使用順序或隨機的采樣技術。與頻閃儀相似,這些設備憑借合理的技術可以記錄快速變化的周期性信號。數據處理和可視化任務一般在PC上執行,可完全集成在高端儀器中,或通過USB或以太網連接。

測量物體到TDR的適配是一個要求很嚴的任務。舉例來說,差分阻抗測量必須使用高精度的相位匹配電纜和探針。如果不能滿足這個要求,偶數模式和奇數模式轉換將降低測量精度。另外,探針的頭應該設計得與待測設備阻抗相匹配,才能實現可能最高精度的測量。

市場上的不同系統

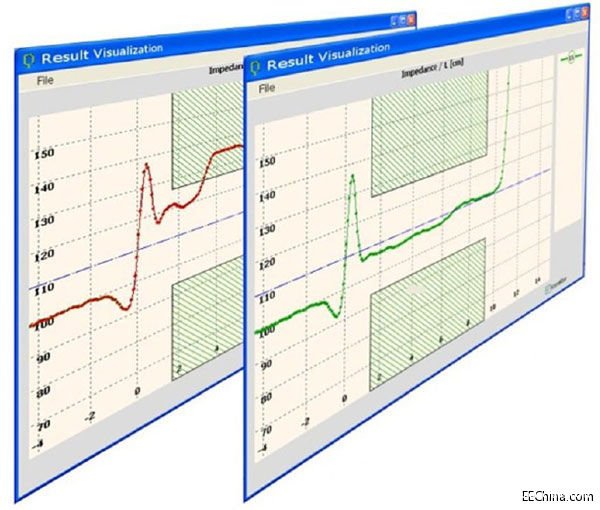

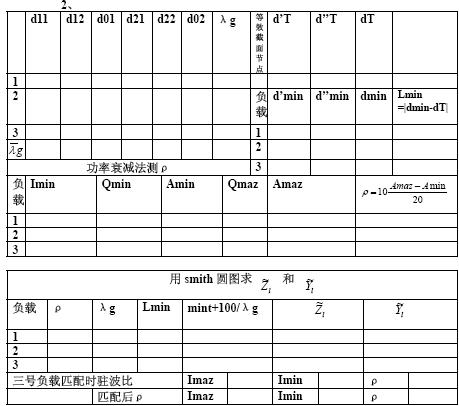

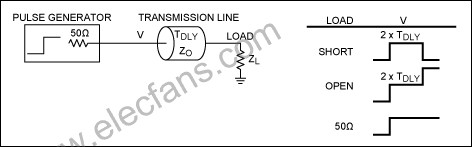

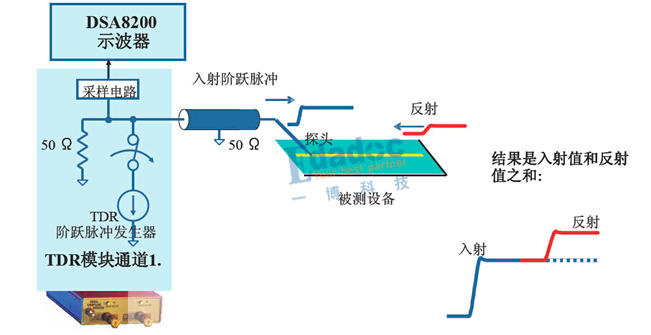

在越來越快的數字世界中,線路阻抗的測量業已表明是目前最重要的TDR應用。圖2顯示了對無干擾(綠色曲線)和有干擾(紅色曲線)傳輸線的這種空間分辨式測量例子。

圖2:正確安裝SMA連接器(1,綠)和錯誤安裝SMA連接器(2,紅)時RG 405同軸電纜的反射圖。

只有傳輸路徑上所有元件(不僅包括蝕刻線,而且包括電纜、連接器甚至集成電路中的終端電阻)都是阻抗匹配的,才能在發送器和接收器之間實現無反射的信號傳輸,從而得到最高的比特率。因此,在評估差分和單端線的信號完整性時阻抗控制是一個很重要的因素。

開發人員和制造商可以從大量不同類型的差分TDR系統(DTDR)中選擇一種用于阻抗控制:從極具成本效益的系統到特別昂貴的系統。一些著名的測量技術制造商提供高精度的高端TDR系統。這些系統可以在高速示波器領域找到,一般都結合了必要的附件,如(D)TDR探針。這些設備非常適合用來測量高達20Gbit/s及以上的傳輸系統。然而對高端設備制造商來說,阻抗控制似乎只是一個利基市場。因此他們不提供專用的工業化解決方案,潛在用戶在達到最終的“阻抗測量”目標之前很快會迷失在無數普通的射頻測量技術之中。此外,由于其高性能和通用性,所有這些系統都屬于高價格領域,這使得投資缺乏吸引力,特別是如果TDR不是持續使用時。

在工業和特殊產品測量技術領域可以發現一些通用性較低的TDR。在過去二十年中這些領域已經建立起了特定的標準程序。這些設備及相關軟件針對測量測試板阻抗進行了優化,在許多PCB制造商那里都有部署。然而,這些TDR不太適合用于PCB內部隨機傳輸線的設計與測試,理由是缺少合適的探針——更糟糕的是——太慢的信號上升時間tr導致太小的信號帶寬,繼而只允許對最小長度約10cm的線進行表征。

作為第三個版本,還有“自我制作的”解決方案。這方面市場上有為數不多的極具成本效益的(D)TDR設備。這樣進一步購買組件(TDR探針和相位調整電纜)一般就能滿足技術上的先決條件。不過在這種情況下,必須在數據記錄、誤差減小、阻抗計算和結果歸檔等方面開發合適的軟件,以便可以追問源自某個來源的解決方案最終并不具有更高的成本效益和安全性。

Sequid GmbH公司最初開發過高分辨率和高精度的TDR系統,用于判斷魚肉的質量。在與德國PCB制造商Elekonta Marek GmbH的合作過程中,現有的基本技術進一步發展為很高性能的系統(Sequid DTDR-65),能夠滿足阻抗控制測量的所有需求。這是一種高穩定的差分時域反射計,適合速率高達10Gbit/s的差分和單端傳輸線的阻抗測量。這種儀器具有65ps的階躍信號發生器,因此支持對測試板和實際電路的高分辨率測量。另外,DTDR-65具有特別好的抖動性能(Jrms《500fs),而這種性能通常是高端設備才有的。

同時開發的軟件解決方案能夠讓非射頻專家也能順利完成阻抗的測量。這種解決方案不僅包含基本功能(比如設備控制),還包含用于顯示線路阻抗的直觀可操作功能。容差模板使得做出通過/失敗(PASS/FAIL)聲明非常簡單。下面介紹了一些簡單的應用例子。

圖3呈現的是RG 405同軸電纜的反射圖,其中的同軸電纜分別按照組裝規范(1)和沒有按照組裝規范(2)裝配了SMA連接器。兩種RG 405電纜的線路阻抗Z0≈51.5Ω,連接器區域的過渡非常明顯。在錯誤安裝連接器的情況下,電容下降(朝低阻抗變形)是可見的。當外部和內部導體安裝靠得太近時這種效應會頻繁發生(也就是構建了一個電容)。

圖3:正確安裝SMA連接器(1,綠)和錯誤安裝SMA連接器(2,紅)時RG 405同軸電纜的反射圖。

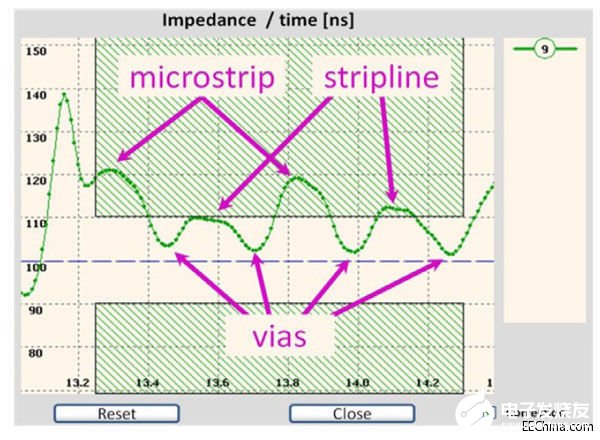

圖4顯示了4層印刷測試電路上的差分傳輸線的阻抗曲線。傳輸路徑一開始是第一層(頂層)中的微帶線,然后通過一個過孔轉到第二層,此時仍然是微帶線,再通過第二個過孔回到第一層表面。這個路線經過幾次反復,最終在第一層終止。顯然這個測試電路不能達到100Ω的目標阻抗:微帶線和帶狀線的特征阻抗分別是Z0≈120Ω和Z0≈110Ω。從這張圖中可以明顯看出,過孔的電容因素會嚴重影響實際系統中的信號完整性,尤其是在高數據速率時更甚。

圖4:在FR4基板的兩個不同層上布線的差分線反射圖。

作為最后一個例子,圖5顯示了USB 3.0連接器和電纜的反射圖。USB 3.0組件的額定阻抗是Z0=90Ω±7Ω。TDR設備仍然工作在100Ω的參考阻抗上(時間范圍t《12.2ns)。從測試適配器到USB 3.0連接器的轉換引起的第一次反射發生在大約12.3ns,正如預期的那樣與所有測量一致。曲線3(綠色)代表開放式適配器的結果,其中的快速阻抗上升指示適配器的(高阻抗)末端。曲線4和5(紅色和藍色)代表兩種不同的USB 3.0電纜組件,每個組件由一個適配器和一個后續電纜組成。雖然電纜都在規范之內,但適配器不符合規范。特別是紅色曲線表明最大阻抗約為122Ω,產生了嚴重反射,進而可能導致USB 3.0控制器降低數據速率。

總之,所有例子清楚地表明,開發人員能夠利用DTDR-65直觀深入地觀察傳輸路徑。開發人員和質檢人員的任務通常包含對所獲得的結果進行容易理解的歸檔。這項任務非常重要,但遺憾的是非常耗時,而且單調乏味。不過這種不受歡迎的工作現在可以用內置的自動化報告生成工具極大地簡化,只需幾次點擊就能形成圖形化和統計性的擴展性評估結果。另外,對大多數普通線路類型來說還可以使用在線阻抗計算器。

圖5:帶開放電路(3)和兩個不同USB 3.0電纜組件(4和5)的USB 3.0適配器的反射圖。

支持廣泛應用

必要的附件包含了高質量的相位調整過的同軸電纜以及TDR探針,可用于不同類型應用:工業探針用于生產過程中的系列測量,高精度探針用于研發——見圖6。DTDR-65還具有卓越的電磁屏蔽性能,完全可以在電池供電的移動應用中使用。

圖6:用于時域反射計DTDR-65的不同探針和附件。

責任編輯:gt

電子發燒友App

電子發燒友App

評論