由于 5G 和IoT互聯(lián)設(shè)備及相關(guān)高帶寬要求預(yù)計將大幅度攀升,所以數(shù)據(jù)中心運營商需要遷移到帶寬更高的網(wǎng)絡(luò),其中的帶寬要超過當(dāng)前通常使用的100 GB 以太網(wǎng) (100GE)。 遷移到下一代 400GE 網(wǎng)絡(luò)要求更快速的內(nèi)存和更高速的串行總線通信。除了把以太網(wǎng)接口升級到 400GE,服務(wù)器還需要采用速度更高的串行擴展總線 接口和內(nèi)存。

PCIe (PCI Express) 擴展總線現(xiàn)在正遷移到最新標(biāo)準化的 PCIe 5.0,也稱為 PCIe Gen 5。 與此同時,DDR ( 雙倍數(shù)據(jù)速率 ) 內(nèi)存也正從 DDR 4.0 遷移到 DDR ≈ 5.0。 PCIe Gen 5 規(guī)范是 PCI-SIG開 發(fā)的 PCIe 4.0 標(biāo)準的快速晉升增強版本。PCI-SIG 是一家標(biāo)準機構(gòu),規(guī)定了所有PCIe規(guī)范。隨著PCIe 5.0 插件機電 (CEM) 規(guī)范的最終確定,PCIe 5.0 標(biāo)準最近完成并于 2021 年 6 月發(fā)布,這是 2019 年發(fā)布的現(xiàn)有 PCIe 5.0 基本 ( 硅 ) 規(guī)范的姊妹篇。

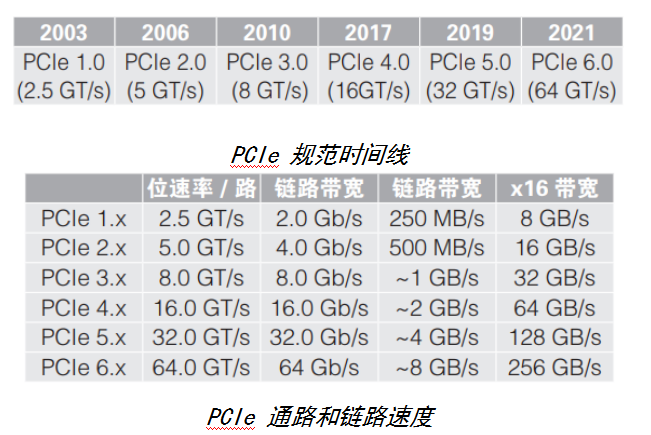

PCIe 標(biāo)準演進,傳輸速度翻番

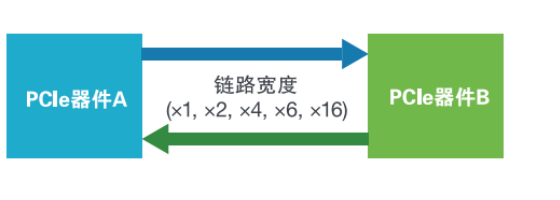

最初的并行 PCI 總線于 1992 年問世,旨在擴展個人電腦的功能,允許添加顯卡和網(wǎng)卡及許多其他外設(shè)。PCIe 是一種高速串行總線, 旨在代替 PCI 及其他現(xiàn)有的傳統(tǒng)接口,如 PCI-X (PCI eXtended) 和 AGP ( 加速圖形端口 )。PCIe 不僅吞吐量高,而且體積小,鏈路寬度可以在 ×1 路、×2 路、 ×4 路、×8 路、×16 路間擴充。PCIe 基于根復(fù)數(shù) ( 系 統(tǒng) / 主機 ) 與端點 ( 插件 ) 之間的點到點總線拓撲,支持基于包的全雙工通信。

PCIe 雙工鏈路通信

PCIe 1.0 標(biāo)準在 2003 年問世,提供了 2.5 G 傳送 / 秒 (2.5 GT/s) 的速率。PCIe 目前提供 2.5 GT/s ~ 32 GT/s 的速率。 PCIe 5.0 把 PCIe 4.0 傳送速率翻了一番,從 16 GT/s 提高到 32 GT/s,但沒有提供任何新增功能,因為當(dāng)時的目標(biāo)是在最短的時間內(nèi)提供額外的速度。

目前發(fā)布的所有 PCIe 標(biāo)準都采用非歸零 (NRZ) 信令。 但是,PCI-SIG 目前正在開發(fā) PCIe Gen 6 規(guī)范,將再次把傳送速率翻一番,達到 64 GT/s,將從 NRZ 信令遷移出去。而 Gen 6 第六代規(guī)范將采用 PAM-4信令,以及低時延FEC (前向糾錯) 技術(shù)來改善數(shù)據(jù)完整性。

所有 PCIe 標(biāo)準都必須向下兼容,也就是說,PCIe 5.0 (32 GT/s 最大數(shù)據(jù)速率 ) 還必須支持 2.5 GT/s、5 GT/ s、8GT/s、16 GT/s 及 32 GT/s。

PCIe 一致性測試,面臨特定挑戰(zhàn)

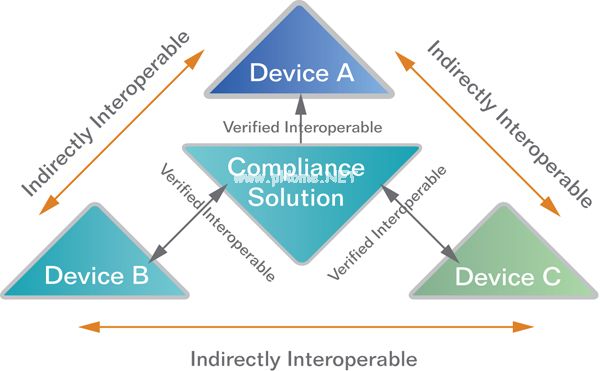

PCI-SIG 是非專有 PCI 技術(shù)標(biāo)準和相關(guān)規(guī)范的開發(fā)者,PCIe現(xiàn)在已經(jīng)成為服務(wù)器事實上的標(biāo)準。PCI-SIG 規(guī)定了 PCI 規(guī)范,以支持要求的 I/O 功能,同時向下兼容以前的規(guī)范。為了能夠在整個行業(yè)內(nèi)采用 PCI 技術(shù),PCI-SIG 同時支持互操作能力和一致性測試,包括實現(xiàn)一致性必需執(zhí)行及通過的測試。

PCI-SIG 允許會員針對其他會員產(chǎn)品和測試套件進行互操作能力測試,參加測試的產(chǎn)品要么通過測試,要么未通過測試。為了通過正式的一致性測試, 產(chǎn)品必須通過至少 80% 的互操作能力測試,并通過所有標(biāo)準性的一致性測試。

PCIe 5.0 面臨特定的挑戰(zhàn)。PCIe 4.0 的最大數(shù)據(jù)速率是 16 GT/s,是 PCIe 上一代的速度加強規(guī)范,經(jīng)驗證實現(xiàn)起來要比以前的標(biāo)準更難。在 PCIe 5.0 中,計算機 PCIe 通道和主板都面臨著明顯的挑戰(zhàn),因為要處理 32 GT/s 數(shù)據(jù)速率。除了在較低數(shù)據(jù)速率遇到的挑戰(zhàn)外,PCIe 5.0 設(shè)備預(yù)計還會遇到明顯的信號完整性挑戰(zhàn)。泰克擁有針對所有數(shù)據(jù)速率 (Tx、Rx 和 PLL 帶寬 ) 的 PCI-SIG 批準的測試套件。

泰克 PCIe Gen 5 Tx 一致性測試解決方案

泰克是 PCI-SIG 的主要貢獻者,為 PCIe 4.0 和 5.0 物理層測試規(guī)范做出了重大貢獻,為確定 PCIe 6.0 Tx/Rx 測量方法做了大量探尋道路式的試驗。泰克還在 PCIe 標(biāo)準開發(fā)和實現(xiàn)過程中在一致性和互操作能力測試方面發(fā)揮了關(guān)鍵作用。

PCIe 5.0 發(fā)射機測試,適當(dāng)?shù)臏y試設(shè)備和自動化軟件至關(guān)重要

在開發(fā) PCIe Gen 5 發(fā)射機器件時,不管是在基本 ( 芯片 ) 級還是在 CEM ( 系統(tǒng)和插件 ) 級,都將要求芯片級驗證 ( 通常由 PHY IP 公司執(zhí)行 ) 和預(yù)一致性測試, 然后才能把器件提交給 PCI-SIG 進行正式的一致性測試。因此,獲得適當(dāng)?shù)臏y試設(shè)備及相關(guān)自動化軟件至關(guān)重要。

PCIe 一致性測試包括:

● 電氣測試 - 評估平臺、插件發(fā)射機 (Tx) 和接收機 (Rx) 特點

● 配置測試 - 評估 PCIe 器件中的配置空間

● 鏈路協(xié)議測試 - 評估器件的鏈路級協(xié)議特點

● 交易協(xié)議測試 - 評估器件的交易級協(xié)議特點

● 平臺 BIOS 測試 - 評估 BIOS 識別和配置 PCIe 器件的能力

在電氣測試方面,它分成兩套測量,一套是基本級,一套是 CEM 級。這些測試又分為標(biāo)準性測試和參考性測試:

PCIe 基本和 CEM 一致性測量

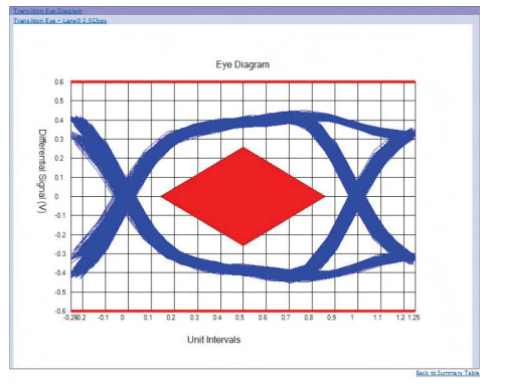

眼圖

這兩類測量都要求高帶寬實時示波器,要能夠捕獲數(shù)據(jù)波形。然后采用后處理技術(shù),進行基本規(guī)范和 CEM 規(guī)范中要求的相應(yīng)的電壓和定時測量。不相關(guān)抖動考查在去除包和通道碼間干擾 (ISI) 后系統(tǒng)固有的抖動。 除了抖動外,示波器還要進行眼高和眼寬測量。基本規(guī)范中規(guī)定了大量的“一致性測試碼型”。推薦使用包含多次發(fā)生的整個一致性測試碼型的波形記錄,來構(gòu)建代表性眼圖。

在器件的基本 Tx 測試中,規(guī)范規(guī)定直接在發(fā)射機的引腳上進行測量。如果不能直接接入,那么測試點應(yīng)盡可能靠近器件引腳。如果用戶很好地了解 S 參數(shù), 那么通過物理復(fù)現(xiàn)通道或仿真,可以反嵌任何接續(xù)通道損耗。從 4.0 規(guī)范開始,描述了另一種反嵌技術(shù), 在波形后處理過程中,對不相關(guān)抖動測量應(yīng)用 CTLE ( 連續(xù)時間線性均衡 ),可以有效消除直到引腳的 ISI。

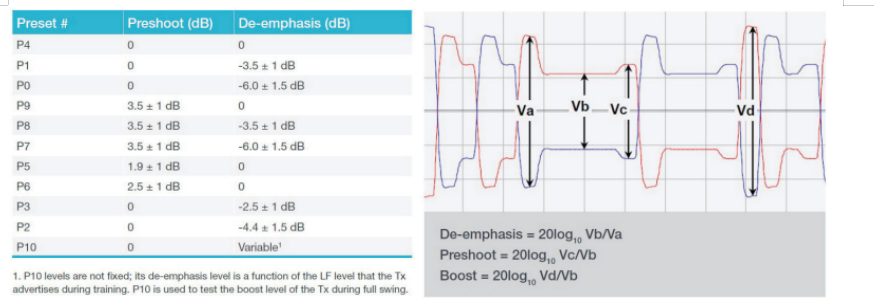

Tx 均衡器預(yù)置

提交 PCI-SIG 認證的任何 PCIe 5.0 產(chǎn)品,都必須使用規(guī)定的 Tx 均衡器設(shè)置預(yù)置成功地通過一致性測試,支持速度從 2.5 GT/s 直到 32 GT/s。這些預(yù)置用來均衡碼流內(nèi)部的頻率相關(guān)衰減差引起的碼間干擾,改善了信號完整性。每個預(yù)置都是下沖 ( 光標(biāo)前 ) 和去加重 ( 光標(biāo)后 ) 的特定組合。

目前有各種特定實現(xiàn)方案,讓 DUT 發(fā)射機掃描通過 各種數(shù)據(jù)速率和 Tx EQ 預(yù)置。但是,基本規(guī)范規(guī)定了一種常用的方法,其中向接收機的通路 0 傳送一個 100 MHz時鐘突發(fā)。這可以采用任意函數(shù)發(fā)生器(AFG) 自動實現(xiàn)。

對最大速率為32 GT/s 的 PCIe 鏈 路, 基本時鐘 (Refclks) 存在著新的驗證挑戰(zhàn)。基本規(guī)范已經(jīng)與數(shù)據(jù)速率成比例擴大抖動極限,但 Gen5 不成比例地把極限下降到 150 fs。這種高頻抖動測量要求正確應(yīng)用公共時鐘傳送功能,并考慮最壞情況傳送延遲。這一最新版規(guī)范還把測量從基本級規(guī)范 ( 芯片級 ) 推高到是 CEM 規(guī)范要求 ( 外表級 ),必需滿足一致性測試。

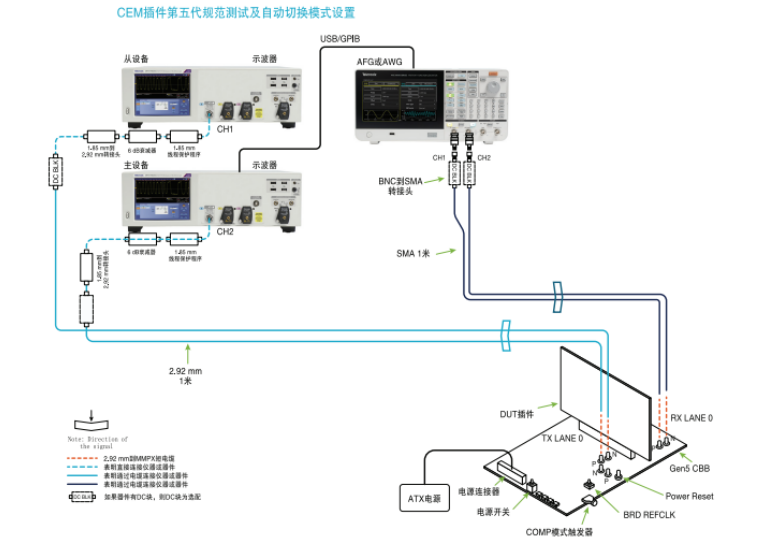

CEM 插件 PCIe 5.0 一致性測試及自動預(yù)置切換

泰克 PCIe 解決方案,讓一致性測試更有信心

示波器帶寬和采樣率要求。對基本 Tx 測試,每條 PCIe 5.0 通路以 16 GHz 速率運行( 因為兩個比特可以在一個周期中發(fā)送 ),三階諧波達到 48 GHz。由于在三階諧波以上沒有太有效的信號信息,所以 PCIe 5.0 基本 Tx 測試只需 50 GHz 帶寬的實時示波器。對 CEM Tx 測試,要在最壞情況通道的末端附近進行測量,減少了高頻內(nèi)容,要求 33 GHz 的帶寬。為確保充足的波形后處理 (SigTest),要求每個單位間隔最少 4 個點,CEM 允許最多 2x sinx/ x 插補,所以最低采樣率要達到 128 GS/s。

自動一致性測試。在一致性測試中,手動執(zhí)行分析既耗時又容易出錯。為節(jié)省時間,最好使用自動化軟件,其不僅可以減少工作量,還可以加快一致性測試速度。對電氣驗證, PCI-SIG 提供了SigTest 離線分析軟件,使用示波器采集的數(shù)據(jù)執(zhí)行分析。自動化軟件還控制被測器件 (DUT),使用任意函數(shù)發(fā)生器作為碼型源,讓 DUT 自動通過一致性測試所需的各種速度、去加重和預(yù)置。

一輪完整的一致性測試要求在不同的 DUT 設(shè)置下每條通路采集多個波形。這個波形集合將按需要分析的通路數(shù) ( 最多 16 條 ) 提高。軟件要能夠管理和存儲分析及未來參考要求的數(shù)據(jù),這對任何一致性測試解決方案來說都是一個重要指標(biāo)。自動化軟件還可以調(diào)節(jié)示波器水平和垂直設(shè)置及采集度。除了配置和分析外,還可以使用自動化軟件管理采集的多個波形。

自動化軟件可以選擇數(shù)據(jù)速率、電壓擺幅、預(yù)置和要執(zhí)行的測試。它還可以提供選項,嵌入包參數(shù)模型,反嵌電纜、 測試夾具或到達規(guī)范規(guī)定的目標(biāo)測試點所需的其他元素。來自軟件的分析結(jié)果通常可以匯編成 PDF 或 HTML 格式的報告,可以包括通過 / 未通過測試摘要、眼圖、設(shè)置 配置和用戶備注。

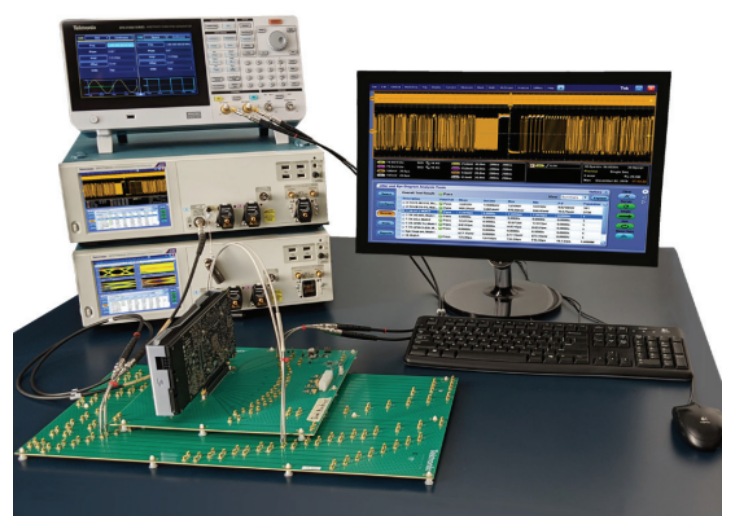

通過使用泰克 DPO70000SX 系列示波器和 AFG31252 任意函數(shù)發(fā)生器,PCI Express Gen1/2/3/4/5 解決方案可以在基本級 ( 芯片 ) 和 CEM 級 ( 系統(tǒng)和插件 ) 自 動進行發(fā)射機驗證和一致性測試。

TekExpress PCIe 5.0 Tx 自動軟件功能:

- 使 DUT 自主步進通過不同的速度、碼型和 Tx EQ 預(yù)置

- 在進行測量前,在發(fā)射機上檢驗信號是否正確

- 執(zhí)行通道和包嵌入和反嵌

- 支持 SigTest 和 SigTest Phoenix 各版軟件和模板文件

- 使用 Silicon Labs. “PCIe 時鐘抖動工具”和泰克 DPOJET 軟件進行 100 MHz 參考時鐘抖動和信號完整性測量

在歷史上,當(dāng)新一代 PCIe 器件進入一致性測試時,很大一部分器件在進行 PHY 和鏈路訓(xùn)練一致性測試時,會在第一次互操作能力講習(xí)會中通不過測試。在PCI-SIG講習(xí)會前,確保完善的示波器、AFG、BERT( 用 于 Rx 測試 ) 和自動化軟件解決方案到位至關(guān)重要。泰克 PCIe 測試和調(diào)試 Tx、Refclk 和 Rx 解決方案可以在互操作能力測試前引導(dǎo)您完成一致性測試和調(diào)試,確保您的設(shè)計滿懷信心地滿足 PCI-SIG? PCIe 標(biāo)準要求。

電子發(fā)燒友App

電子發(fā)燒友App

評論