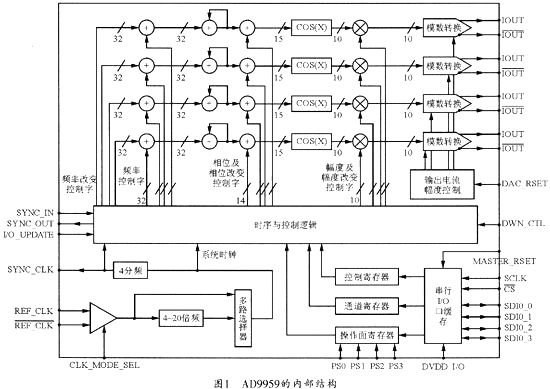

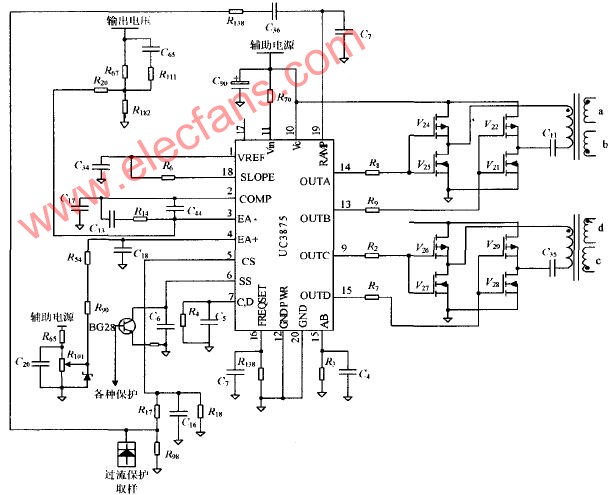

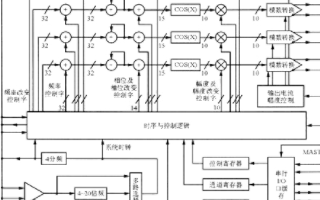

AD9959可以實現最多16電平的頻率、相位和幅度調制,還可以工作在線性調頻、調相或調幅模式。AD9959的應用范圍包括相控陣列雷達/盧納系統、儀表、同步時鐘和RF信號源。AD9959的內部結構如圖1所示,主要特性如下:

◇有4路帶10位DAC的DDS通道,最高取樣頻率為500 MSPS;

◇大于65 dB的通道隔離度;

◇32位頻率分辨率;

◇14位相位失調分辨率;

◇10位輸出幅度可縮放的分辨率;

◇具有增強數據吞吐量的串行I/O口(SPI);

◇可軟件/硬件控制以降低功耗;

◇雙電源(DDS核1.8 V,串行I/O3.3 V);

◇內置多器件同步功能;

◇內置時鐘倍頻鎖相環(4~20倍倍頻)。

2 AD9959的引腳功能

AD9959采用56腳LFCSP封裝,各引腳的功能定義如下:

SYNC_IN:輸入引腳,可同步多片AD9959。使用時應與主AD9959的SYNC_OUT相連;

SYNC_OUT:輸出引腳,可同步多片AD9959,使用時應與從AD9959的SYNC_IN相連;

MASTER_RESET:復位輸入引腳,高有效;

PWR_DWN_CTL:外部電源掉電控制引腳;

AGND:模擬地;

DVDD:數字電源(1.8 V);

DGND:數字地;

DAC_RSET:輸入引腳,可為DAC設置參考電流,使用時應通過一個1.91 kΩ電阻接地;

REF_CLK和REF_CLK:參考時鐘或振蕩輸入端(互補輸入),如果使用單端輸入方式,則應從REF_CLK引腳連接一個0.1μF的解耦電容到 AVDD或AGND;

CLK_MODE_SEL:振蕩器部分控制引腳,接高電平時,電壓不要超過1.8 V,接低電平時,振蕩器被旁路;

LOOP_FILTER:輸入端,使用時應串聯一個零電阻和680 pF電容至最近的AVDD腳(Pin28);

I/O_UPDATE:輸入引腳,通過該腳的上升沿可把串行口緩存的數據內容送至激活的寄存器中,I/O_UPDATE信號應與SYNC_CLK信號保持同步,并須滿足建立時間與保持時間的要求;

CS:片選串口使能信號端,低有效;

DVDD_I/O:3.3 V數字電源;

SYNC_CLK:時鐘輸出,為內部時鐘的1/4,用于同步I/O_UPDATE信號;

SCLK:I/O串行操作時鐘輸入端,在該端的上升沿寫入數據,下降沿讀出數據;

SDIO_0:雙向引腳,用于串行操作的數據輸入和輸出;

SDIO_1:3:雙向引腳,用于串行操作數據輸入輸出,也可用于控制DAC輸出幅度的斜率;

P0~P3:輸入引腳,這四個引腳用于控制調制方式的選擇,掃描累加器的開關或者輸出幅度的升降斜率。該四個引腳中的任何一個引腳信號的變化都等同于一個I/O_UPDATE信號的上升沿,該端須與SYNC_CLK信號保持同步,并須滿足建立時間與保持時間的要求;

CH0_IOUT ~CH3_IOUT, CH0_IOUT ~CH3_IOUT:輸出引腳,四個通道的互補輸出端,使用時,需接上拉電阻至AVDD。

3 工作模式組合

AD9959所具有的的四通道可以使其同時實現多種工作模式的組合。但是,在某些模式下,則需要幾個數據引腳來實現特殊功能,這就限制了組合方式。根據AD9959芯片的資源,可同時實現的工作模式組合如下:

(1) 四個通道可以實現單頻模式、2電平調制模式和線性掃描模式的任意組合,每個通道均可工作在這三種模式中的一種;

(2) 可以同時有一個或兩個通道工作在4電平調制模式,余下的通道工作在單頻模式;

(3) 可以有一個通道工作在8電平調制模式,余下的通道工作在單頻模式;

(4) 可以有一個通道工作在16電平調制模式,余下的通道工作在單頻模式;

(5) 單頻模式下,可以控制每個通道的輸出幅度斜率;

(6) P2和P3引腳用于控制輸出幅度斜率時,任意兩個通道可同時工作在2電平調制模式,也可同時工作在線性調頻或調相模式;

(7) P3引腳用于控制輸出幅度斜率時,可以有一個通道工作在8電平調制模式,余下的通道工作在單頻模式;

(8) SDIO_1~SDIO_3引腳用于控制輸出幅度斜率時,四個通道可以實現各種2電平調制模式的組合,而未用于2電平調制模式的通道則可工作在單頻模式;

(9) SDIO_1~SDIO_3引腳用于控制輸出幅度斜率時,可以同時有一個或兩個通道工作在4電平調制模式,其余通道工作在單頻模式;

(10) SDIO_1~SDIO_3引腳用于控制輸出幅度斜率時,可以有一個通道工作在16電平調制模式,其余通道工作在單頻模式;

(11) 幅度調制、線性幅度掃描和控制輸出幅度斜率功能不能同時實現,但頻率和相位調制則可與控制輸出幅度斜率功能同時實現。

4 串行操作

AD9959的四個通道可共享一組寄存器地址,這種地址共享機制其得可以同時向四個通道的配置寄存器寫入相同的數據。當需要對四個通道進行不同設置時,可以通過設置通道使能位來各自獨立地寫入每個通道設置的數據。

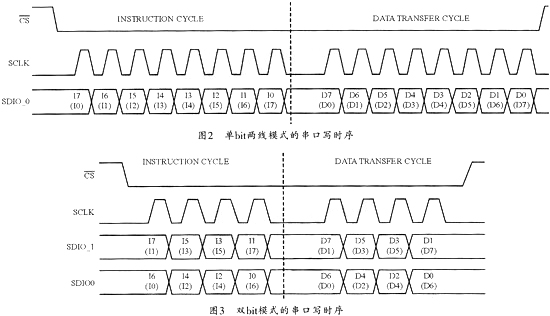

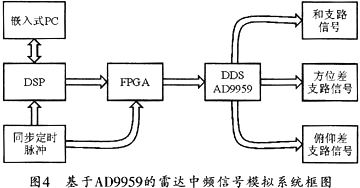

一個串口通信周期分為指令周期和數據讀寫周期兩個階段。首先傳送指令階段的8位指令字,對應于SCLK的8個上升沿,然后執行由指令設定的1~4個字節的數據讀寫,完成后再等待下一個指令周期的到來。

AD9959的串口操作與ADI公司之前推出的DDS芯片基本一致,但由于AD9959有四個串行數據引腳(SDIO_0:3),因而其編程具有更大的靈活性,通過配置相應的寄存器可以有四種編程方式進行串行I/O操作。分別是單bit兩線模式,單bit三線模式。雙bit模式和四bit模式。

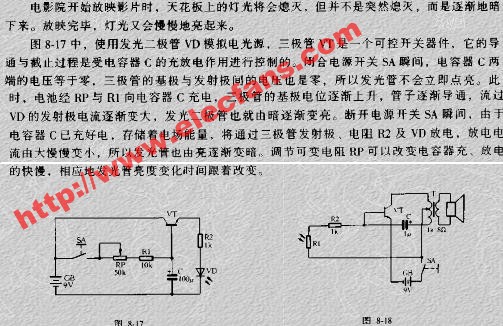

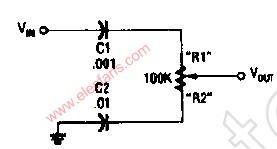

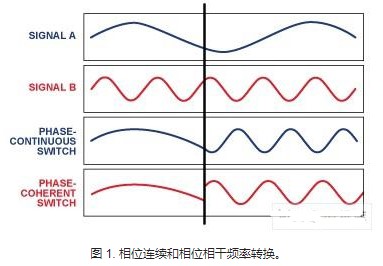

設置為單bit兩線模式時,SDIO_0為雙向數據引腳。設置為單bit三線模式時,SDIO_0為數據輸入引腳,SDIO_2為數據輸出引腳。在這兩種模式下,SDIO_3都作為串口同步恢復信號引腳,通過一個正脈沖使串口恢復為初始等待指令狀態。圖2給出了單bit兩線模式的串口寫時序。

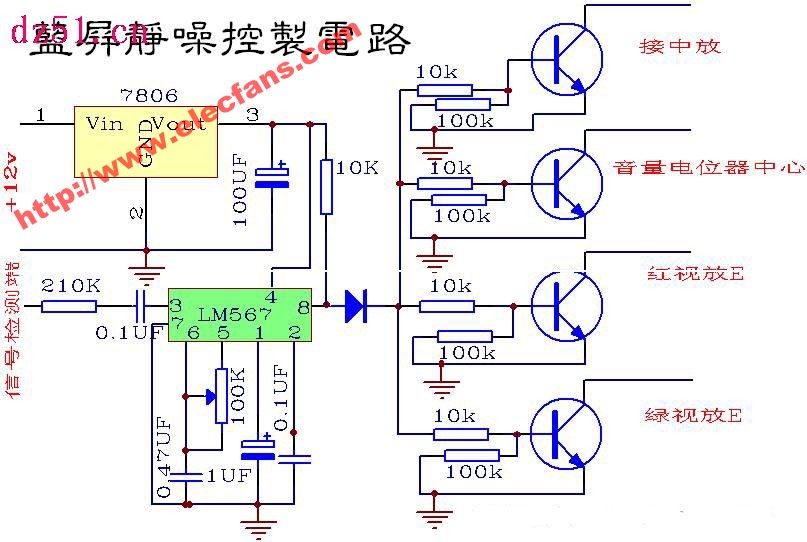

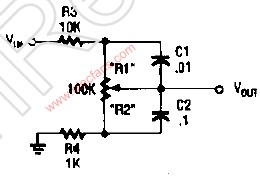

設置為雙bit模式時,SDIO_0和SDIO_1同時作為雙向數據引腳,每個SCLK周期傳輸兩位數據,這樣,傳送一個八位的數據信息只需要四個SCLK周期,SDIO_3仍作為串口同步恢復信號。圖3給出了雙bit模式的串口寫時序。

設置為四bit模式時,SDIO_0:3可同時作為雙向數據引腳,每個SCLK周期傳輸四位數據,故傳送一個八位數據信息僅需要兩個SCLK周期。

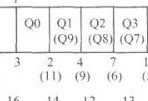

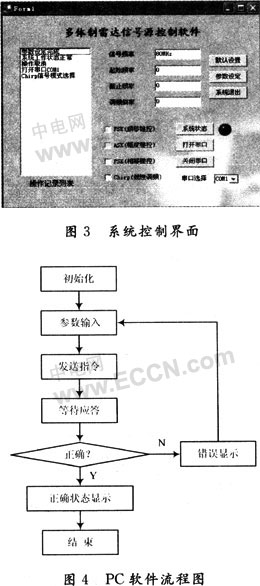

5 在雷達中頻信號模擬器中的應用

現代雷達信號模擬器的設計偏重于運用數字化方式來實現。事實上,隨著實時數字信號處理技術的發展,PC+DSP+DDS的體系結構已成為雷達信號模擬器實現的主要方式。而AD9959由于在一塊芯片上集成了四個DDS通道,因此,AD9959的使用可為多路雷達信號模擬器的設計提供了極大的方便。因為它可使得原本需要多片單通道DDS芯片的系統,現在只需一片AD9959即可完成系統功能。

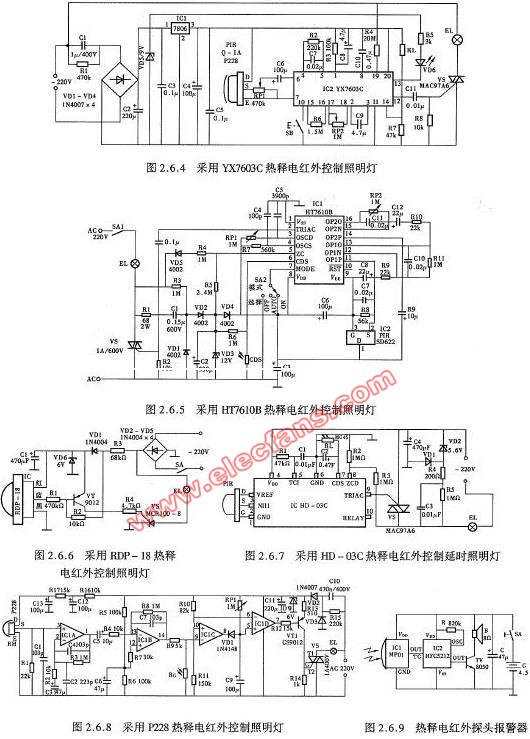

圖4所示是一種基于AD9959芯片的雷達中頻信號模擬系統的三通道設計結構框圖。其信號模擬過程為:嵌入式PC首先對目標及環境進行建模和運算,以生成雷達信號仿真數據庫,然后由DSP根據嵌人式PC傳來的目標信息,計算出與DDS在不同時刻需要生成的對應信號頻率、相位和幅度數據。并將數據傳人FPGA,再由FPGA對數據進行并串轉換,并在同步定時脈沖的觸發下,在特定時間將數據串行寫入DDS,從而完成對DDS的設置。最后再由DDS同時產生三路中頻模擬信號。

6 結束語

AD9959由于內部集成有多個DDS通道,它無需多片單通道DDS芯片及其外部電路,因而有助于簡化系統設計過程,減小PCB面積。實際試驗結果證明:AD9959具有的高性能,可使之廣泛的應用于雷達和通信系統之中。本站還有AD9959的配置程序和應用電路,請搜索。

電子發燒友App

電子發燒友App

評論