采用高輸入頻率、高速模數轉換器(ADC)的系統設計是一項具挑戰性的任務。ADC輸入接口設計有6個主要條件:輸入阻抗、輸入驅動、帶寬、通帶平坦度、噪聲和失真。看看這里羅列的這六個條件,你都了解嗎?

2016-01-13 16:55:38 4864

4864

采用高輸入頻率、高速模數轉換器(ADC)的系統設計是一項具挑戰性的任務。ADC輸入接口設計有6個主要條件:輸入阻抗、輸入驅動、帶寬、通帶平坦度、噪聲和失真。看看這里羅列的這六個條件,你都了解嗎?

2022-07-27 09:07:51 1548

1548 該應用筆記論述了如何選擇適當的變壓器和無源元件,并在不犧牲高速ADC動態性能的情況下獲得較寬的輸入頻響的增益平坦度。

2023-02-09 14:21:57 1134

1134

本文詳細介紹了通常應用于IF和基帶的高速模數轉換器(ADC)的正確布板、元件選擇及元件布局。文中以高分辨率、高速數據轉換器MAX12555系列為例,介紹了優化電路設計、正確高速布板、旁路和去耦技巧、熱管理、元件選擇及布局。

2023-02-23 14:53:19 757

757 ,它主要與二次諧波失真有關;

所需的增益和輸入匹配。

較高的增益要求會提高匹配難度。此外,高增益要求會壓縮ADC內部器件的裕量,從而提高非線性度,而且由于有更多功率經過外部無源器件,它們的非線性度也會

2023-12-18 06:13:51

。源電阻較高或者超過模擬前端(變壓器或放大器)上滿量程輸入信號的一半時,目標頻段中的噪聲將變得難以控制,最終導致轉換器性能下降。

為何如此?如果調低滿量程輸入,必須調高增益。在理論上,這樣做

2023-12-19 06:18:48

道、250 MSPS、14 位 ADC 時的性能與輸入頻率之間的關系。討論了用于共模電壓、電源和接口的各種選項,這些選項經過測量,滿足各種應用的要求。顯示了抗混疊濾波器示例以及它們所提供的性能改進。特性高速

2015-05-11 10:33:40

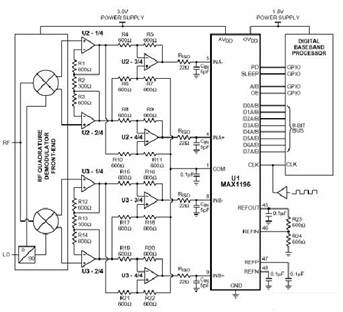

描述此參考設計展示了高速放大器 THS4509 執行單端至差動轉換以驅動高速模數轉換器 (ADC),同時保持卓越的噪聲和失真性能的能力。為交流和直流耦合應用顯示了連接到 ADS4449 四通

2018-08-09 08:38:52

設計說明該子系統演示了如何在可編程增益放大器 (PGA) 配置中設置 MSPM0 內部運算放大器,動態更改增益,輸出放大的信號以及使用 ADC 讀取結果。該配置使用戶能夠使用具有高增益的小輸入電壓

2023-04-12 15:01:32

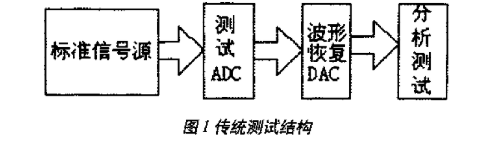

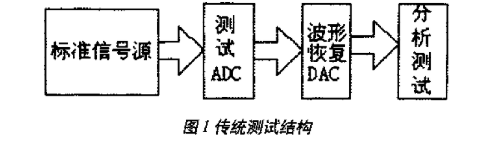

ADC 有比較高的采樣率以采集高帶寬的輸入信號,另一方面又要有比較高的位數以分辨細微的變化。因此,保證 ADC/DAC 在高速采樣情況下的精度是一個很關鍵的問題。ADC/DAC 芯片的性能測試是由芯片

2018-04-03 10:39:35

的增益和輸入匹配。 較高的增益要求會提高匹配難度。此外,高增益要求會壓縮ADC內部器件的裕量,從而提高非線性度,而且由于有更多功率經過外部無源器件,它們的非線性度也會提高。這種效應一般被視為三次諧波。圖

2018-09-17 15:48:29

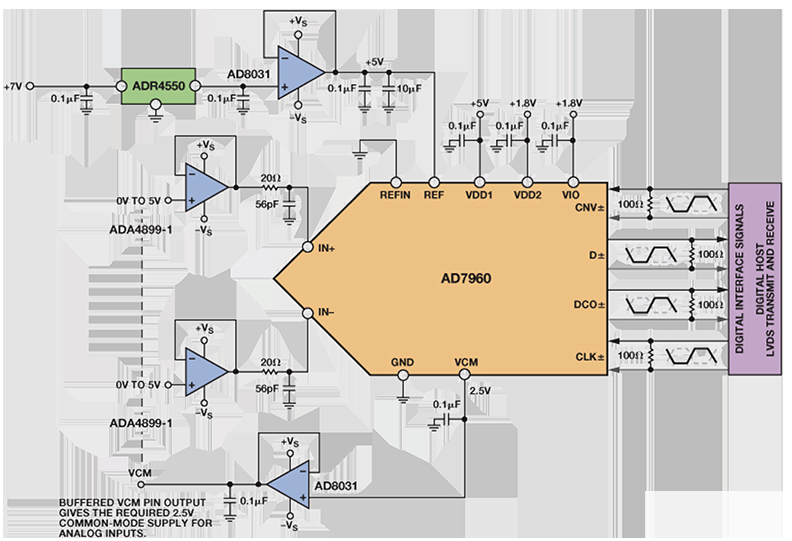

采用高速模數轉換器(ADC)的系統設計非常困難,對于輸入有兩類ADC架構可供選擇:緩沖型和無緩沖型。

緩沖和無緩沖架構的特征

高線性度緩沖器,但需要更高的功率;

更易設計輸入網絡與高阻抗緩沖器接口

2023-12-18 07:42:00

來源 網絡采用高速模數轉換器(ADC)的系統設計非常困難,對于輸入有兩類ADC架構可供選擇:緩沖型和無緩沖型。 緩沖和無緩沖架構的特征 緩沖架構的基本特征 * 高線性度緩沖器,但需要更高的功率

2018-01-23 16:01:44

采用高速模數轉換器(ADC)的系統設計非常困難,對于輸入有兩類ADC架構可供選擇:緩沖型和無緩沖型。 緩沖和無緩沖架構的特征緩沖架構的基本特征高線性度緩沖器,但需要更高的功率;更易設計輸入網絡與高

2018-09-17 15:38:24

采用高速模數轉換器(ADC)的系統設計非常困難,對于輸入有兩類ADC架構可供選擇:緩沖型和無緩沖型。緩沖和無緩沖架構的特征緩沖架構的基本特征*高線性度緩沖器,但需要更高的功率;*更易設計輸入網絡與高

2018-10-18 11:23:57

如今,在設計人員面臨眾多電源選擇的情況下,為高速ADC設計清潔電源時可能會面臨巨大挑戰。在利用高效開關電源而非傳統LDO的場合,這尤其重要。此外,多數ADC并未給出高頻電源抑制規格,這是選擇正確

2018-11-21 17:14:38

而非傳統LDO的場合,這尤其重要。此外,多數ADC并未給出高頻電源抑制規格,這是選擇正確電源的一個關鍵因素。本技術文章將描述用于測量轉換器AC電源抑制性能的技術,由此為轉換器電源噪聲靈敏度確立一個基準

2018-10-15 09:49:24

正確選擇輸入網絡元件對于高速ADC的驅動和輸入網絡的平衡至關重要(參考應用筆記:“正確選擇輸入網絡,優化高速ADC的動態性能和增益平坦度”)。??在較高IF應用中,端接電阻的位置非常重要。交流耦合

2021-10-23 11:10:35

描述此參考設計展示了高速放大器 LMH6554 執行單端至差動轉換以驅動高速模擬至數字轉換器 (ADC),同時保持卓越的噪聲和失真性能的能力。為交流和直流耦合應用顯示了連接到 ADS4449 四通

2018-08-03 06:00:28

驅動器的噪聲性能與ADC的ENOB作一比較。描述這一過程的例子是為采用5V電源工作的 AD9445 ADC選擇和評估一款增益為2、2V 滿量程輸入的差分驅動器。它能處理用一個單極點濾波器限制、占用

2018-11-01 11:14:51

作為應用工程師,我們經常遇到各種有關差分輸入型高速模數轉換器(ADC)的驅動問題。事實上,選擇正確的ADC驅動器和配置極具挑 戰性。為了使魯棒性ADC電路設計多少容易些,我們匯編了一套通用"

2018-10-17 10:52:42

。 AD745還具有卓越的直流性能,最大輸入偏置電流為250帕,最大偏置電壓為0.5毫伏。 AD745的內部補償為更高的增益進行了優化,提供了更高的帶寬和更快的轉換速率。這使得AD745作為一個前置放大器

2020-07-10 15:51:22

。 AD745還具有卓越的直流性能,最大輸入偏置電流為250帕,最大偏置電壓為0.5毫伏。 AD745的內部補償為更高的增益進行了優化,提供了更高的帶寬和更快的轉換速率。這使得AD745作為一個前置放大器

2020-07-13 15:33:31

AD9434BCPZ-500高速ADC芯片是ADI公司的AD9434系列單芯片采樣模數轉換器,該高速ADC芯片是一款專為高性能、低功耗和易用性的設備進行優化,具有出色的動態性能和適合寬帶載波和寬帶

2019-11-12 09:25:36

AD9481-PCB,AD9481評估板是一款8位,單芯片模數轉換器(ADC),針對高速和低功耗進行了優化。該產品體積小,易于使用,轉換速率為250 MSPS,在整個工作范圍內具有出色的線性度和動態

2019-11-07 06:25:57

傳感器的輸出幅度等于ADC輸入范圍的一半,所以ADC驅動器的增益應設置為2。這要求Rf等于Rg,但Rf的選擇有一定的靈活性。

首先來看看不同的Rf(和Rg)值對系統本底噪聲和相應的預期SNR有何

2023-12-11 07:15:15

大多數高動態范圍應用的理想選擇。單位增益穩定性使OPA642特別適用于低增益差分放大器、跨阻放大器、+2視頻線驅動器增益、寬帶積分器和低失真ADC放大器。如果需要更高的增益甚至更低的諧波失真度,請考慮

2020-10-19 15:44:32

dB的小信號增益和34.5 dBm的輸出三階截取(OIP3)提供出色的性能。 該放大器在任何400 MHz帶寬上具有0.5 dB的出色增益平坦度,并且CMRR為35dB。 該放大器具有通過VPD引腳

2020-03-18 16:20:27

`QPA9133是100Ω差分輸入至50Ω單端輸出寬帶增益模塊。 它非常適合作為5G m-MIMO BTS Tx路徑的第一增益級,直接與收發器的DAC接口,從而無需分立的巴倫。該放大器具有出色的性能

2020-03-20 11:09:18

的性能,具有20 dB的小信號增益和35 dBm的輸出三階截取(OIP3)。 該放大器在任何400 MHz帶寬上均具有0.5 dB的出色增益平坦度,并且CMRR為30dB。 該放大器具有通過VPD引腳

2020-03-20 11:15:22

近年來,隨著數字信號處理技術的迅猛發展,數字信號處理技術廣泛地應用于各個領域。因此對作為模擬和數字系統之間橋梁的模數轉換器(ADC)的性能也提出了越來越高的要求。低電壓高速ADC在許多的電子器件

2018-10-08 15:47:53

系統應用,在以下各例中,LTC6430-15 的高線性度、低噪聲和寬頻帶性能經受住了考驗。在以下第一個例子中,LTC6430-15 的差分輸出與 ADC 的差分輸入很相配。LTC6430-15 的輸入

2018-10-18 16:03:48

使運算放大器的噪聲性能與ADC相匹配在混合信號應用中,正確地選擇驅動模數轉換器 (ADC) 的運算放大器至關重要。設計人員必須要對一些問題進行權衡,例如:放大器噪聲、帶寬、設置時間、ADC 信噪比

2009-11-21 14:32:53

濾波器那樣簡單單調地下降。不管是哪一種情況,通常要求通帶平坦度小于或等于1 dB,這對于穩定總系統增益至關重要。 輸入驅動能力是由特定應用需要的系統增益決定。輸入驅動能力與帶寬指標密切相關,并且依賴于所選擇

2018-12-14 09:27:03

正確選擇輸入網絡元件對于高速ADC的驅動和輸入網絡的平衡至關重要(參考應用筆記:“正確選擇輸入網絡,優化高速ADC的動態性能和增益平坦度”)。 在較高IF應用中,端接電阻的位置非常重要。交流耦合

2011-08-05 09:28:06

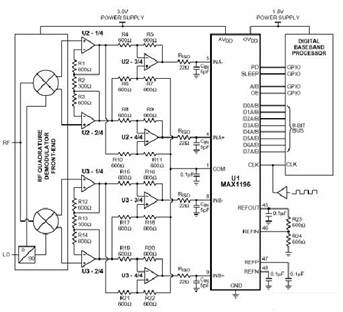

可滿足高性能數字接收機動態性能要求的ADC和射頻器件有哪些?

2021-05-28 06:45:13

。對于選擇高速ADC時專注于其他規范的工程師來說,NSD也可能是一個完全陌生的概念。下面是一些工程師的典型問題的答案,這些答案有助于說明為什么他們應該更多地了解這種ADC性能指標:在奈奎斯特速率ADC數據

2018-11-01 11:33:13

反射到輸入網絡中。如果不加以衰減,它會反射回ADC且被重新采樣,致使ADC的失真或交調失真性能下降。ADC的輸入網絡應盡可能接近50 Ω,以便最大限度地吸收此非線性電荷。使用高吸收性濾波器可抑制采樣過程中產生的非線性信號音,從而改善SFDR。

2019-07-23 06:18:02

一樣的——有源和無源器件均是如此,因此,無論系統最終選擇了什么器件,模擬信號鏈中都會存在誤差。 本文將描述精度、分辨率和動態范圍之間的差異。本文還將揭示信號鏈內部的不精確性是如何累積并導致誤差的。定義新設計的系統參數時,這些內容對于理解如何正確指定或選擇一個ADC有著重要作用。

2021-02-25 07:19:50

如題,如何選擇正確的ADC 輸入端:是先濾波再放大,還是先放大再濾波呢?歡迎大家根據您的經驗討論哦

2023-11-24 06:50:39

高頻應用如何才能取得最好性能所需的變頻器特性?如何選擇適合高頻應用的高速ADC?

2021-04-13 06:45:25

本文介紹如何確定接收器增益,以及接收器增益設置太高時對接收SNR的負面影響。文章也討論如何正確優化數字波束成形器、濾波器、檢波器的動態范圍以及壓縮信號映射。實現上述優化后,系統將最大程度地發揮高SNR接收器的優勢,大幅提高診斷性能。

2021-04-19 10:00:39

網絡表是pcb自動布線的靈魂,是原理圖與電路板設計的接口。只有將網絡表導入后,才能進行電路板的布局布線。 單擊菜單Design,選擇Load nets,彈出如圖19所示的導入網絡表對話框。單擊

2018-09-04 16:20:18

采取措施并可能在下一個數據集準備處理之前移動數據。參考選擇。評估集成ADC時,一個重要標準是內部精密參考源的可用性。在某些情況下,設置多個參考電壓范圍的能力可確保解析ADC不同輸入范圍的靈活性

2019-03-18 06:45:12

目前的實時信號處理機要求ADC盡量靠近視頻?中頻甚至射頻,以獲取盡可能多的目標信息?因而,ADC的性能好壞直接影響整個系統指標的高低和性能好壞,從而使得ADC的性能測試變得十分重要?那要怎么測試高速ADC的性能?

2021-04-14 06:02:51

對高速信號進行高分辨率的數字化處理需審慎選擇時鐘,才不至于使其影響模數轉換器(ADC)的性能。那么時鐘抖動會對高速ADC的性能有什么影響呢?

2021-04-08 06:00:04

降低效率為代價。優化配電網絡可以改善這些參數,同時將噪聲降低到必要的水平。本文在闡述高性能信號鏈中電源紋波的影響的基礎上進一步分析。我們將深入探討如何優化高速數據轉換器的配電網絡。我們將對標準PDN

2021-07-17 07:00:01

,因此可以直接為這些電源軌供電,并且不會降低DAC動態性能。帶有LC濾波器的LTM8074為2 V模擬和2 V數字電源軌供電。圖11.AD9213高速ADC的優化PDN。表3比較了優化PDN與現成標準

2021-07-03 07:00:00

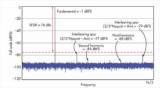

(ENOB)、輸入帶寬、無雜散動態范圍(SFDR)以及微分或積分非線性度等。對于GSPS ADC,最重要的一個交流性能參數可能就是SFDR。簡單而言,該參數規定了ADC以及系統從其他噪聲或者任何其他雜散頻率中

2018-11-01 11:31:37

請問高速ADC或DAC輸入時鐘占空比如果不是50%或遠高于或遠低于50%對ADC或DAC性能有何影響?

2018-08-16 06:09:00

請問高速ADC或DAC輸入時鐘占空比如果不是50%或遠高于或遠低于50%對ADC或DAC性能有何影響?

2023-12-13 07:28:01

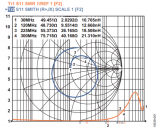

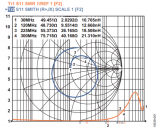

關于HMC8410的問題 貴司發布了寬帶低噪聲放大器HMC8410,從頻響上來看,高端增益偏小(輸入匹配性能大幅下降)。 看起來高頻段增益降低與輸入匹配惡化有關,請問這個輸入匹配惡化是芯片本身輸入特性決定的還是外偏置電路決定的。 通過外偏置電路可將增益平坦度調整到什么樣的水平。 謝謝!

2018-08-23 18:25:22

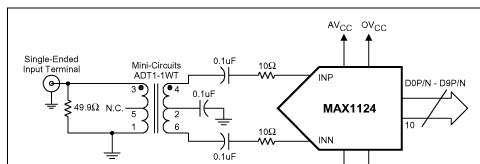

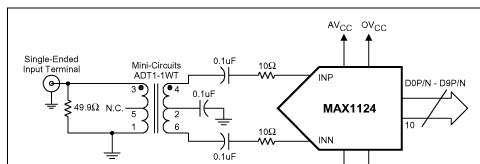

怎樣將單端信號轉換成差分信號呢?變壓器有哪些最優匹配方法?如何改善ADC的增益平坦度并保持它的動態性能呢?

2021-04-22 06:35:25

到航空航天,這些系統在不同的應用中各有不同。。。 硅片處理技術的發展(65 nm CMOS、28 nm CMOS等)使高速 ADC 得以跨越 GSPS(每秒千兆采樣)門檻,同時提供12位或14位性能

2018-11-20 10:50:51

ADC的動態性能。為了將這種影響最小化,ADC的時鐘源必須具有很低的定時抖動或相位噪聲。如果在選擇時鐘電路時沒有考慮該因素,則系統的動態性能在很大程度上將不由前端模擬輸入或ADC的質量決定。理想時鐘

2019-05-30 05:00:04

由工程的角度系統地介紹基于CDMA20001x/EV-DO空中接口技術建立的CDMA移動通信系統無線接入網的設計與優化技術,給出了無線接入網設計與優化的詳細流程和工作內容,并對網絡優化

2009-06-10 14:27:42 26

26 在高中頻ADC應用中,如何改善增益平坦度同時又不影響動態性能:摘要:本文指導用戶選擇適當的變壓器,用于高速模/數轉換器(ADC)前端的信號調理。本文還闡述了如何合理選擇無

2009-09-25 08:22:23 23

23

在高中頻ADC應用中,如何改善增益平坦度同時又不影響動態性能

本文指導

2006-05-07 13:40:17 588

588 在高中頻ADC應用中,如何改善增益平坦度同時又不影響動態性能

摘要:本文指導用戶選擇適當的變壓器,用于高速模/數轉換器(

2008-09-11 21:04:34 755

755

副邊變壓器端接提升高速ADC的增益平坦度

Abstract: The following application note describes the differences between

2009-02-17 10:37:28 789

789

摘要:本文指導用戶選擇適當的變壓器,用于高速模/數轉換器(ADC)前端的信號調理。本文還闡述了如何合理選擇無源元件,在較寬的輸入頻率范圍內改善增益的平坦度,而且不會犧

2009-04-25 09:27:05 408

408

摘要:本應用筆記描述了變壓器原邊端接和副邊端接的區別,通常用于前置高速模/數轉換器(ADC)的信號調理鏈路。本文詳細說明了在較高中頻(IF)的應用中,兩種端接對高速ADC增益平

2009-04-25 09:30:04 412

412

摘要:該應用筆記論述了如何選擇適當的變壓器和無源元件,并在不犧牲高速ADC動態性能的情況下獲得較寬的輸入頻響的增益平坦度。 對于較高IF的模/數轉換器(ADC),

2009-04-25 09:31:04 432

432

摘要:本文指導用戶選擇適當的變壓器,用于高速模/數轉換器(ADC)前端的信號調理。本文還闡述了如何合理選擇無源元件,在較寬的輸入頻率范圍內改善增益的平坦度,而且不會犧

2009-05-01 10:45:52 501

501

摘要:本應用筆記描述了變壓器原邊端接和副邊端接的區別,通常用于前置高速模/數轉換器(ADC)的信號調理鏈路。本文詳細說明了在較高中頻(IF)的應用中,兩種端接對高速ADC增益平

2009-05-01 10:50:25 490

490

摘要:該應用筆記論述了如何選擇適當的變壓器和無源元件,并在不犧牲高速ADC動態性能的情況下獲得較寬的輸入頻響的增益平坦度。 對于較高IF的模/數轉換器(ADC),

2009-05-01 10:51:07 805

805

摘要:本文指導用戶選擇適當的變壓器,用于高速模/數轉換器(ADC)前端的信號調理。本文還闡述了如何合理選擇無源元件,在較寬的輸入頻率范圍內改善增益的平坦度,而且不會犧

2009-05-07 11:10:01 349

349

摘要:本應用筆記描述了變壓器原邊端接和副邊端接的區別,通常用于前置高速模/數轉換器(ADC)的信號調理鏈路。本文詳細說明了在較高中頻(IF)的應用中,兩種端接對高速ADC增益平

2009-05-08 10:30:36 612

612

摘要:該應用筆記論述了如何選擇適當的變壓器和無源元件,并在不犧牲高速ADC動態性能的情況下獲得較寬的輸入頻響的增益平坦度。 對于較高IF的模/數轉換器(ADC),

2009-05-08 10:31:16 566

566

設置高速ADC的共模輸入電壓范圍(中文)

對于包含基帶采樣、高速ADC的通信接收機,輸入共模電壓范圍(VCM)非常重要。特別是對于單電源供

2010-03-30 17:59:39 3883

3883

采用高輸入頻率、高速模數轉換器(ADC)的系統設計是一項具挑戰性的任務。ADC輸入接口設計有6個主要條件:輸入阻抗、輸入驅動、帶寬、通帶平坦度、噪聲和失真。

2013-08-22 16:13:18 24

24 在為高性能系統選擇寬帶模數轉換器(ADC)時,需要考慮多種模擬輸入參數,比如,ADC分辨率、采樣速率、信噪比(SNR)、有效位數(ENOB)、輸入帶寬、無雜散動態范圍(SFDR)以及微分或積分非線性度等。 對于GSPS ADC,最重要的一個交流性能參數可能就是SFDR。

2018-07-10 01:52:00 8762

8762

本文討論了高頻應用要取得最好性能所需的變頻器特性,包括平坦的頻率響應、高輸入帶寬、低輸入滿刻度電壓范圍以及針對多陣列系統調整參數的能力。文章還討論了與選擇高分辨率高速ADC有關的系統設計考慮因素。

2017-09-15 16:07:55 26

26 EDFA 的增益平坦化是 DWDM 系統中的關鍵問題,介紹了 EDFA 增益平坦濾波器的實現技術原理并對其關鍵技術參數進行了比較,認為啁啾光柵增益平坦濾波器是一較好的選擇。試驗表明,在高功率

2017-11-07 10:17:52 14

14 TIDA-01053 是一種 ADC 驅動器參考設計,用于為高動態范圍儀表優化 THD、噪聲和全系統 SNR。ADC 輸入的高電容性質給驅動器設計和器件選擇過程帶來了一些獨特的挑戰,需要同時確保

2017-12-07 18:13:38 0

0 本應用注釋討論了如何通過設計正確的時鐘電路和良好的模擬輸入網絡,來優化高速流水線ADC的性能,以及如何將ADC的高速不失真的數據輸送到FPGA或ASIC上。

2018-05-18 10:34:32 10

10 本應用注釋討論了如何通過設計正確的時鐘電路和良好的模擬輸入網絡,來優化高速流水線ADC的性能,以及如何將ADC的高速不失真的數據輸送到FPGA或ASIC上。

2018-05-18 10:41:22 0

0 在較高IF應用中,端接電阻的位置非常重要。交流耦合輸入信號可以在變壓器的原邊或副邊端接,具體取決于系統對高速ADC增益平坦度和動態范圍的要求。寬帶變壓器是一個常用元件,能夠在較寬的頻率范圍內將單端信號轉換成差分信號,提供了一種快速、便捷的解決方案。

2020-07-31 17:56:42 1554

1554

高速ADC是信號處理機的不可欠缺的組成部分,其性能的好壞對信號處理系統的整體性能也至關重要。通常ADC的技術參數是由生產廠商提供,可作為設計的重要依據,但是在電路板上形成的ADC模塊的性能如何,還與

2020-08-01 11:35:54 3431

3431

固定增益差分放大器簡化對高速 ADC 的驅動

2021-03-21 03:06:00 10

10 電子發燒友網為你提供如何正確選擇一個ADC資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-27 08:45:33 0

0 AD7329:1 MSPS,8頻道,軟件選擇器,True雙極輸入,12位增益Sign Sign ADC數據Sheet

2021-05-10 08:15:59 2

2 AD7322:2頻道,軟件選擇table,True雙極輸入,1 MSPS,12位增益Sign Sign ADC數據Sheet

2021-05-10 11:54:17 1

1 多通道應用中使用的精密高速數據采集系統需要最先進的性能。本模擬技巧涵蓋了在選擇ADC驅動器以優化信號鏈性能時需要考慮的關鍵規格。

2023-01-08 16:16:36 593

593

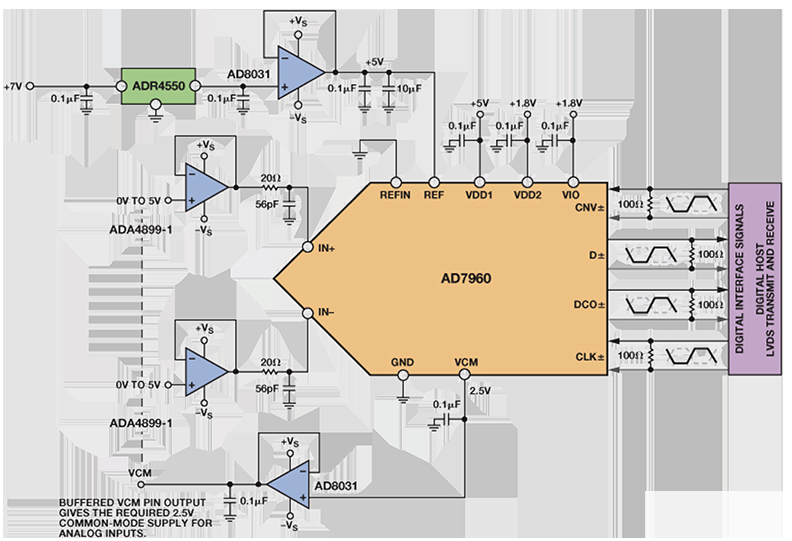

正確選擇電路板元件是滿足高中頻模數轉換器(ADC)苛刻的高動態性能和增益平坦度要求的重要因素。以下技術說明將提供有關輸入網絡的適當選擇,這些輸入網絡旨在借助寬帶變壓器、端接電阻器和濾波電容器輕松進行單端到差分輸入信號轉換。

2023-01-10 11:29:26 734

734

以下應用筆記描述了高速模數轉換器(ADC)之前信號調理電路中常用的變壓器的初級側和次級端接之間的差異。本文詳細介紹了這兩種端接方案對專為高中頻應用設計的ADC的增益平坦度和動態性能的影響。

2023-01-13 14:49:03 538

538

模數轉換器 (ADC) 代表接收器、測試設備和其他電子設備中模擬和數字世界之間的鏈接。如本系列文章第1部分所述,許多關鍵動態參數提供了給定ADC預期動態性能的精確相關性。本系列文章的第 2 部分介紹了用于測試高速 ADC 動態規格的一些設置配置、設備建議和測量程序。

2023-02-25 09:26:43 1754

1754

本文指導用戶如何選擇合適的變壓器,通常用于高速模數轉換器(ADC)之前的信號調理電路。本文還介紹了如何選擇無源元件,以便在很寬的輸入頻率范圍內實現增益平坦度,同時又不犧牲這些ADC的動態性能。最后

2023-02-27 14:33:34 583

583

作為應用工程師,我們經常遇到各種有關差分輸入型高速模數轉換器(ADC)的驅動問題。事實上,選擇正確的ADC驅動器和配置極具挑戰性。為了使魯棒性ADC電路設計多少容易些,我們匯編了一套通用“路障”及解決方案。本文假設實際驅動ADC的電路—也被稱為ADC驅動器或差分放大器—能夠處理高速信號。

2023-11-27 08:31:36 2

2

電子發燒友App

電子發燒友App

評論