摘要:本應用筆記討論了4.3Gsps下行電纜直接RF合成DAC MAX5881與現場可編程門陣列(FPGA)的接口技術。討論的重點是MAX5881高速數字輸入與Xilinx? Virtex?-5 FPGA的接口時序。這里討論的技術同樣適用于其它多種FPGA和定制ASIC。

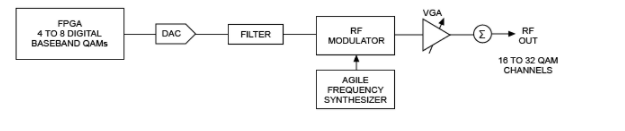

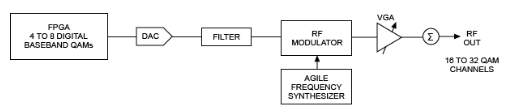

圖1. MAX5881與Xilinx Virtex-5 FPGA的接口(CLKDIV = 0,DDR數據接口架構)

對FPGA DCM2使用外部時鐘反饋,以自動補償FPGA固有的隨溫度變化的輸出數據時鐘。設計外部時鐘反饋路徑,使其嚴格匹配MAX5881的DATACLKP/DATACLKN輸出到FPGA內部數據路徑的延時。這確保了由數字時鐘管理器(DCM)提供的時鐘補償與FPGA時鐘、數據路徑的溫度漂移相一致。使時鐘反饋信號的PCB路徑與數據路徑加上DATACLK路徑長度相等,以確保FPGA的數據輸出變化與DATACLK邊沿一致。給時鐘反饋路徑加上額外的延時,可以使數據與時鐘保持一致。設計或調整延時以確保MAX5881從數據建立到保持時間段內的數據穩定性。可以采用延長時鐘反饋信號路徑長度、或者在反饋路徑上增加一個FPGA ODELAY器件的方法,以實現這種額外的延時。

表1. Virtex-5與MAX5881接口的數據周期分析

圖2. 周期容限

圖3. 時序參考波形

時序分析的第二部分計算了所需要的時鐘反饋延時(表2),同時計算了與反饋延時相對應的建立和保持時間容限,或者叫做時序余量。

表2. 數據時序分析(MAX5881的引腳DELAY = 0)

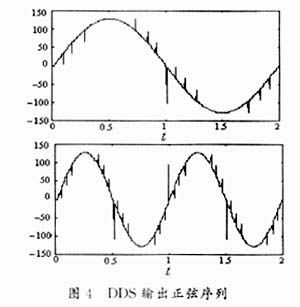

同樣地,這部分分析在各種工作頻率下重復進行。由于數據生成量太大,表格中沒有給出這些數據,而是用圖4建立容限和圖5保持容限給出了曲線示意圖。

圖4. 建立容限

圖5. 保持容限

需要注意的是,在圖4和圖5中,時鐘反饋延時基于寬工作頻率范圍(變化的fDAC)進行計算。實現方法是設置無效數據窗口的前沿,也就是在這個位置,數據開始變化為MAX5881保持時間后的下一個值。換句話說,一旦滿足了保持時間規定,FPGA就開始轉換到下一個數據值。

對于某一個特定頻率,可以使用增加保持時間容限并且減少建立時間容限的方法來平衡建立時間和保持時間容限。這是通過在時鐘反饋路徑上插入可變延時的途徑實現的。對于低頻,建立和保持時間容限足夠大,容限平衡將失去意義。

圖6. 容限平衡

介紹

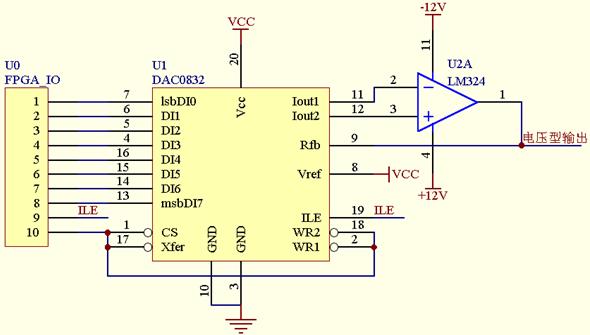

由于MAX5881 4.3Gsps下行電纜直接RF合成DAC具有寬帶特性,相比窄帶DAC,它的數據接口需要更高的工作頻率。通常,設計寬帶數據接口時,需要注意確保其工作可靠、無誤。接口架構

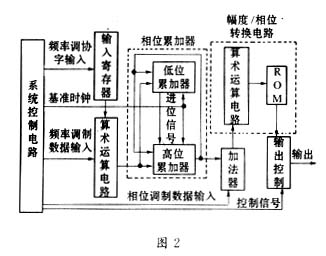

FPGA功能可以有多種不同組合,有幾種接口架構可供選擇,其中之一如圖1所示。這種架構可以支持較寬的工作頻率范圍,并且對處理過程、電壓和溫度(PVT)變化有較好的容限。本應用筆記重點討論這種架構的特征。通過數據接口的具體時序分析,突出了該架構相比其它架構的優點。

圖1. MAX5881與Xilinx Virtex-5 FPGA的接口(CLKDIV = 0,DDR數據接口架構)

時鐘

MAX5881具有獨立的模擬和數字時鐘。MAX5881為數字數據接口提供時鐘輸出。由于作為數據源的FPGA并不是數據時鐘源,所以,需要使用一個“系統同步”的數據接口1。需要注意的是,MAX5881的數據時鐘輸出DATACLKP/DATACLKN抖動非常小,原因是它直接來自于高質量的模擬時鐘CLKP/CLKN輸入。對FPGA DCM2使用外部時鐘反饋,以自動補償FPGA固有的隨溫度變化的輸出數據時鐘。設計外部時鐘反饋路徑,使其嚴格匹配MAX5881的DATACLKP/DATACLKN輸出到FPGA內部數據路徑的延時。這確保了由數字時鐘管理器(DCM)提供的時鐘補償與FPGA時鐘、數據路徑的溫度漂移相一致。使時鐘反饋信號的PCB路徑與數據路徑加上DATACLK路徑長度相等,以確保FPGA的數據輸出變化與DATACLK邊沿一致。給時鐘反饋路徑加上額外的延時,可以使數據與時鐘保持一致。設計或調整延時以確保MAX5881從數據建立到保持時間段內的數據穩定性。可以采用延長時鐘反饋信號路徑長度、或者在反饋路徑上增加一個FPGA ODELAY器件的方法,以實現這種額外的延時。

數據速率

把MAX5881的CLKDIV引腳設置為低電平,FPGA配置為雙倍率(DDR)輸出數據格式。在這種情況下,DATACLKP/DATACLKN信號的頻率是MAX5581 CLKP/CLKN引腳輸入時鐘頻率的四分之一。對于MAX5581的更新速率,CLKP/CLKN的頻率是2.0GHz。使得DATACLKP/DATACLKN的頻率為500MHz。這個500MHz的時鐘信號用來驅動FPGA的串行器(OSERDES),串行器配置為在時鐘的上升和下降沿都會輸出數據。因此FPGA輸出數據的周期是1ns (或者1.0GHz)。由于Xilinx不允許DCM (或者此種情況下的PLL)配置成外部時鐘反饋和多重輸出時鐘,配置CLKDIV = 0,可以避免生成一個雙倍頻率時鐘驅動串行器。位于FPGA最后端的數據輸出級的OSERDES器件減小了上行時鐘或OSERDES側數據輸入的頻率。這使得FPGA的布局和布線變得容易。對于MAX5581的更新速率,上行時鐘的頻率是250MHz。接口時序

表1以數據表的方式提供了數據接口的時序分析。通過兩個部分進行分析,第一部分,對接口工作頻率進行分析,稱為“數據周期分析”。這部分內容不考慮在數據周期內穩定數據的確切位置。然而,它可以確定:是否可能調整時鐘反饋延時,以確保MAX5881從數據建立到數據保持時間窗口內的數據穩定性。數據表中分析了一個工作頻率,并重復分析了其它幾個工作頻率(沒有示意),圖2所示為分析結果。同時,圖3給出了時序參考波形。表1. Virtex-5與MAX5881接口的數據周期分析

| Value | Unit | Specification | Description | Source | Notes |

| 4.300 | GHz | fDAC | MAX5881 output update rate | MAX5881 data sheet | ? |

| 0.5375 | GHz | fDATACLK = fDAC/8 | DDR interface mode | MAX5881 data sheet | ? |

| 930 | ps | tDATAPERIOD = 1/(2 × fDATACLK) | Data period | MAX5881 data sheet | ? |

| 50 | ps | tINFBOFFSET | FPGA DCM feedback phase error (peak ±) | Xilinx ds202.pdf | ? |

| 120 | ps | tPERJITT | FPGA DCM jitter (peak ±) | Xilinx ds202.pdf | ? |

| 121 | ps | dtOUTWC | Worst PVT FPGA output-to-output skew (peak-to-peak) | ".twr" post-layout static timing report from Xilinx static timing analyzer (worst-case PVT) | ? |

| 1.4 | ps | dtPCB | Board output-to-output skew | Estimate | All PCB data and data clock trace lengths matched |

| 462 | ps | dtTOTAL = (2 × tINFBOFFSET) + (2 × tPERJITT) + dtOUTWC + dtPCB | Total FPGA data output timing variance | ? | ? |

| 1100 | ps | tSETUP | MAX5881 setup time | MAX5881 data sheet | ? |

| -760 | ps | tHOLD | MAX5881 hold time | MAX5881 data sheet | ? |

| 590 | ps | tDW = tDATAPERIOD - (tSETUP + tHOLD) | MAX5881 data change window | ? | Time in clock period when data does not have to be valid and stable |

| 128 | ps | tPSL = tDW - dtTOTAL | Period timing slack | ? | Extra time between FPGA changing data; data must be stable at DAC |

圖2. 周期容限

圖3. 時序參考波形

時序分析的第二部分計算了所需要的時鐘反饋延時(表2),同時計算了與反饋延時相對應的建立和保持時間容限,或者叫做時序余量。

表2. 數據時序分析(MAX5881的引腳DELAY = 0)

| Value | Unit | Specification | Description | Source | Notes |

| 0 | ps | tDOUTNOM | FPGA clock-to-data output delay | FPGA external clock-feedback configuration | Feedback-path length equal to data-path length plus clock-path length; this centers data transitions at the clock edge |

| -170 | ps | tSUNOM = tDATAPERIOD - tSETUP - tDOUTNOM | Nominal setup margin (without dtTOTAL factor) | ? | Calculate margin without jitter, skew, and phase-error effects first; they are accounted for later |

| 760 | ps | tHLDNOM = tDOUTNOM - tHOLD | Nominal hold margin | ? | Calculate margin without jitter, skew, and phase-error effects first; they are accounted for later |

| -401 | ps | tSUABS = tSUNOM - dtTOTAL/2 | Absolute setup margin (including dtTOTAL factor) | ? | Include jitter, skew, and phase-error effects |

| 529 | ps | tHLDABS = tHLDNOM - dtTOTAL/2 | Absolute hold margin (including dtTOTAL factor) | ? | Include jitter, skew, and phase-error effects |

| -529 | ps | tDADVANCE = -tHLDABS | Delay-adjusted FPGA clock-to-data output | External clock feedback with feedback-path length equal to data-path length plus clock-path length plus tHLDABS | Place data transition immediately after tHOLD |

| 128 | ps | tSUFINAL = tSUABS - tDADVANCE | Delay-adjusted setup margin | ? | ? |

| 0 | ps | tHLDFINAL = tHLDABS + tDADVANCE | Delay-adjusted hold margin | ? | ? |

同樣地,這部分分析在各種工作頻率下重復進行。由于數據生成量太大,表格中沒有給出這些數據,而是用圖4建立容限和圖5保持容限給出了曲線示意圖。

圖4. 建立容限

圖5. 保持容限

需要注意的是,在圖4和圖5中,時鐘反饋延時基于寬工作頻率范圍(變化的fDAC)進行計算。實現方法是設置無效數據窗口的前沿,也就是在這個位置,數據開始變化為MAX5881保持時間后的下一個值。換句話說,一旦滿足了保持時間規定,FPGA就開始轉換到下一個數據值。

對于某一個特定頻率,可以使用增加保持時間容限并且減少建立時間容限的方法來平衡建立時間和保持時間容限。這是通過在時鐘反饋路徑上插入可變延時的途徑實現的。對于低頻,建立和保持時間容限足夠大,容限平衡將失去意義。

圖6. 容限平衡

其它處理過程

由于FPGA器件的靈活性,可以考慮多種設計方法。研究這些方法的具體細節超出了本篇應用筆記的范圍,這里只簡單描述其中幾種:- 使用DCM相位偏移控制輸出數據變化,而不是靠增加DCM時鐘反饋路徑的長度來增加額外延時。這種方法在軟件延時調整方面具有優勢,但同時引入了由FPGA相位偏移電路帶來的更多的時序不確定性。

- 在DCM反饋路徑中使用ODELAY器件。同樣,在軟件延時調整靈活性方面具有優勢,但也會引入更多的時序不確定性。

- 使用方法1或者方法2,但對器件進行逐個校準。MAX5881特性數據表明,在所有器件整個溫度范圍內,每個器件的數據采樣窗變化量是151ps相比于340ps。每個器件的微小時序變化可以補償FPGA時序不確定性。使用這種方法,可以減小FPGA器件間的某些時序差異。

電子發燒友App

電子發燒友App

評論