CPLD

CPLD(Complex Programmable Logic Device)復雜可編程邏輯器件,是從PAL和GAL器件發展出來的器件,相對而言規模大,結構復雜,屬于大規模集成電路范圍。是一種用戶根據各自需要而自行構造邏輯功能的數字集成電路。其基本設計方法是借助集成開發軟件平臺,用原理圖、硬件描述語言等方法,生成相應的目標文件,通過下載電纜(“在系統”編程)將代碼傳送到目標芯片中,實現設計的數字系統。

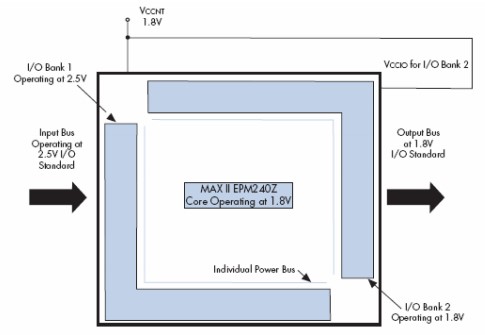

CPLD主要是由可編程邏輯宏單元(MC,Macro Cell)圍繞中心的可編程互連矩陣單元組成。其中MC結構較復雜,并具有復雜的I/O單元互連結構,可由用戶根據需要生成特定的電路結構,完成一定的功能。由于CPLD內部采用固定長度的金屬線進行各邏輯塊的互連,所以設計的邏輯電路具有時間可預測性,避免了分段式互連結構時序不完全預測的缺點。

發展歷史及應用領域

20世紀70年代,最早的可編程邏輯器件--PLD誕生了。其輸出結構是可編程的邏輯宏單元,因為它的硬件結構設計可由軟件完成(相當于房子蓋好后人工設計局部室內結構),因而它的設計比純硬件的數字電路具有很強的靈活性,但其過于簡單的結構也使它們只能實現規模較小的電路。為彌補PLD只能設計小規模電路這一缺陷,20世紀80年代中期,推出了復雜可編程邏輯器件--CPLD。此應用已深入網絡、儀器儀表、汽車電子、數控機床、航天測控設備等方面。

器件特點

它具有編程靈活、集成度高、設計開發周期短、適用范圍寬、開發工具先進、設計制造成本低、對設計者的硬件經驗要求低、標準產品無需測試、保密性強、價格大眾化等特點,可實現較大規模的電路設計,因此被廣泛應用于產品的原型設計和產品生產(一般在10,000件以下)之中。幾乎所有應用中小規模通用數字集成電路的場合均可應用CPLD器件。CPLD器件已成為電子產品不可缺少的組成部分,它的設計和應用成為電子工程師必備的一種技能。

如何使用

CPLD是一種用戶根據各自需要而自行構造邏輯功能的數字集成電路。其基本設計方法是借助集成開發軟件平臺,用原理圖、硬件描述語言等方法,生成相應的目標文件,通過下載電纜(“在系統”編程)將代碼傳送到目標芯片中,實現設計的數字系統。

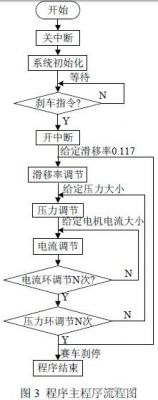

這里以搶答器為例講一下它的設計(裝修)過程,即芯片的設計流程。CPLD的工作大部分是在電腦上完成的。打開集成開發軟件(Altera公司 Max+pluxII)→畫原理圖、寫硬件描述語言(VHDL,Verilog)→編譯→給出邏輯電路的輸入激勵信號,進行仿真,查看邏輯輸出結果是否正確→進行管腳輸入、輸出鎖定(7128的64個輸入、輸出管腳可根據需要設定)→生成代碼→通過下載電纜將代碼傳送并存儲在CPLD芯片中。

7128這塊芯片各管腳已引出,將數碼管、搶答開關、指示燈、蜂鳴器通過導線分別接到芯片板上,通電測試,當搶答開關按下,對應位的指示燈應當亮,答對以后,裁判給加分后,看此時數碼顯示加分結果是否正確,如發現有問題,可重新修改原理圖或硬件描述語言,完善設計。設計好后,如批量生產,可直接復制其他CPLD芯片,即寫入代碼即可。如果要對芯片進行其它設計,比如進行交通燈設計,要重新畫原理圖、或寫硬件描述語言,重復以上工作過程,完成設計。這種修改設計相當于將房屋進行了重新裝修,這種裝修對CPLD來說可進行上萬次。

AD574

AD574是美國核擬器件公司Analog Devices) 生產的12 位逐次逼近型快速A/D 轉換器。其轉換35us,轉換誤差為土0.05%,是前我國應用廣泛,價格適中的A/D轉換器。其內部含三態電路,可直接與各種微處理器連接,且無須附加邏輯接口電路,便能與CMOS 及TTL 電平兼容。內部配置的高精度參考電壓源和時鐘電路,使它不需要任何外部電路和時鐘信號,就能實現A/D轉換功能,應用非常方便。

利用CPLD實現AD574控制器的設計

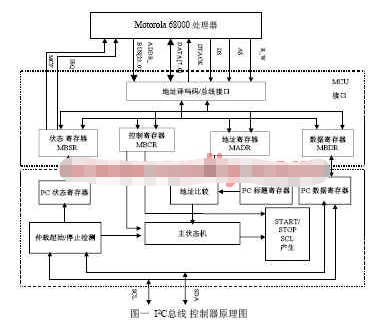

基于PCI總線的汽車電子系統對傳感器的信號進行采樣分析和處理時,均需要利用A/D轉換模塊。本文選用AD574芯片實現汽車電子系統信號調理板上傳感器信號的A/D轉換。

傳感器采集的模擬信號在信號調理板卡上經過放大、濾波后,通過AD574進行A/D轉換后,經PCI總線讀取到MCU中進行分析處理。設計中通過應用VerilogHDL硬件可編程語言在CPLD器件上實現對AD574的控制,節省了MCU的指令執行時間,提高讀寫速度,增強了可靠性和穩定性。

1.AD574工作原理

1.1AD574結構及特性

AD574是美國模擬數字公司推出的單片高速12位逐次比較型A/D轉換器,內置雙極性電路構成的混合集成轉換芯片,具有外接元件少、功耗低、精度高等特點,同時具有自動校零和自動極性轉換功能,只需外接少量的阻容器件即可構成一個完整的A/D轉換器。

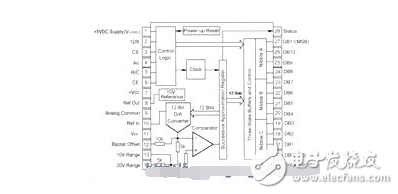

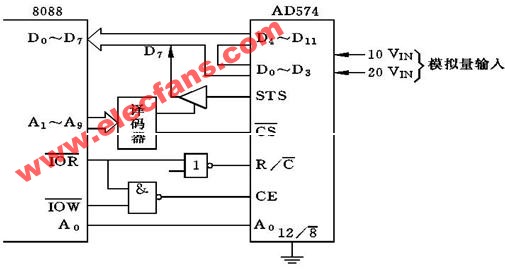

AD574內部結構及外部引腳如下圖所示。

AD574的基本特點和參數如下:AD574帶有內部采樣保持的12位逐次比較型模/數轉換器;轉換速率達25μs,總線訪問時間最大為150ns;非線性誤差小于±1/2LBS或±1LBS;數據可采用12位或8位丙種模式并行輸出;四種單極或雙極電壓輸入范圍分別為±5V、±IOV、0V~10V和0V~20V;采用雙電源供電方式,模擬電路電壓為±l2V或者±l5V,數字電路電壓為±5V。

1.2AD574引腳功能及時序控制

AD574的邏輯控制需要用到以下端口:數據輸出位選擇輸入端12/8、片選信號輸入端CS、讀/轉換狀態輸入端R/C、操作使能端CE、位尋址/短周期轉換選擇輸入端AO以及轉換狀態輸出端STS。

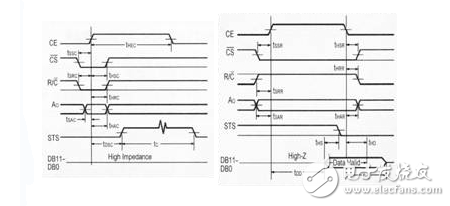

當CE=1且CS=0同時滿足時,AD574開始正常工作。AD574處于工作狀態時,R/C=0時,開始AID轉換;當R/C=1時,讀出數據。數據輸出位選擇輸入端12/8和AO端用來控制啟動轉換的方式和數據輸出格式。當AO=0時,啟動轉換方式按完整的12位AID轉換方式進行;當AO=1時,按8位A/D轉換方式進行。當R/C=1,AD574處于數據狀態,此時AO和數據輸出位選擇輸入端12/8控制數據輸出的格式。當12/8=1時,數據以12位并行輸出;當12/8=0時,數據以8位分兩次輸出;且當AO=0時,輸出A/D轉換數據的高8位;AO=1時輸出A/D轉換數據的低4位,轉換數據的低四位占一個字節的高半字節,低半字節補零。

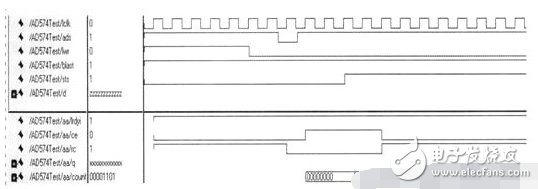

AD574的工作時序分別如下圖所示。

1.3AD574與PCI的接口時序

系統設計中AD574與PCI接口芯片PCI9052相連進行數據傳輸。AD574的轉換控制及讀取數據控制信號均采自PCI9052的引腳,轉換后的數據在PCI9052的控制下通過PCI總線傳輸到MCU中進行分析與處理。通過CPLD設計實現PCI9052對AD574的邏輯控制和時序控制,對應的時序如圖4所示。

時序圖中ADS#、BLAST、LRDYi和LCLK均為PCI總線接口芯片PCI9052的信號引腳。ADS#是PCI總線上發起一次訪問的地址鎖存引腳,用于控制AD574的采樣時間;BLAST為PCI總線上一次訪問的最后一個數據期,用于控制AD574的數據讀取;LRDYi為從設備準備引腳,有效則表明PCI9052可以開始對本地端設備進行讀寫數據,文中用于控制AD574的數據轉換完成的有效信號,以便開始讀取數據;LCLK為PCI9052產生的一個局部時鐘信號,用于控制時序邏輯。

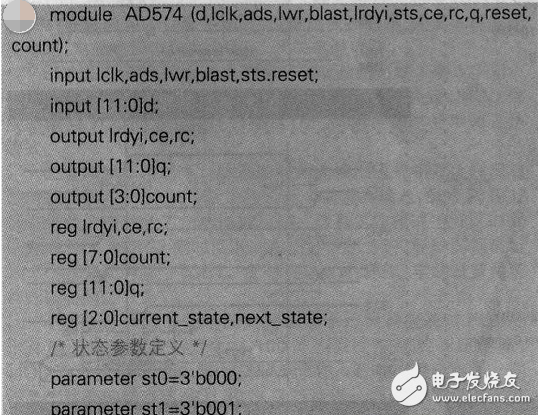

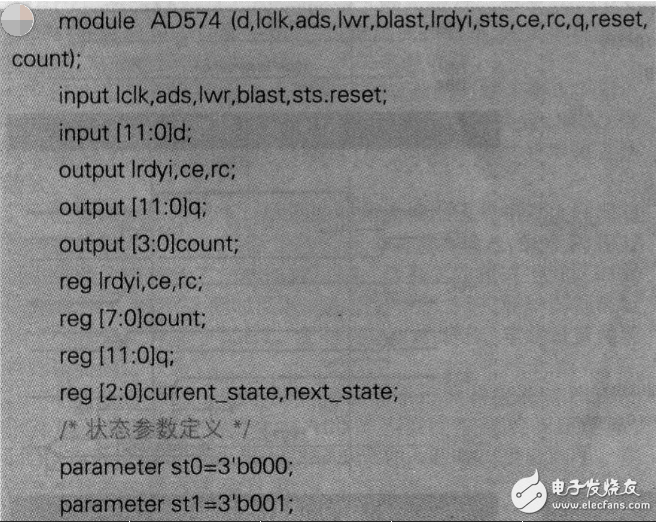

2CPLD設計與實現基于VerilogHDL硬件描述語言實現的ADC574采樣控制設計源程序如下:

代碼中信號定義與圖 2時序圖中引腳對應,同時設計了一個計數器用于控AD574的時序,以滿足AD574的轉換精度及讀取要求。

QUARTus 11軟件為可編程片上系統(SOPC)設計提供了一個工具齊全、功能強大的設計環境。在根據需要選擇好CPLD器件系列后,采用Veilog HDL語言輸入方式編寫控制組合邏輯代碼和測試激勵代碼,利用 Quartus 11 軟件白帶的工具分析綜合代碼,進行布線、布局、資源分配以及分析時序、波形仿真。Quartus11還為第三方 EDA工具軟件提供了友好的接口,可以直接在Quartus 11 中調用 Modelsim軟件進行仿真。

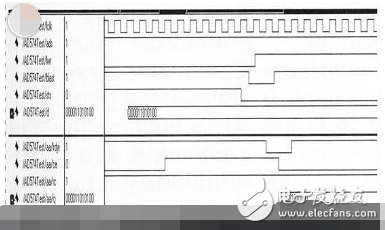

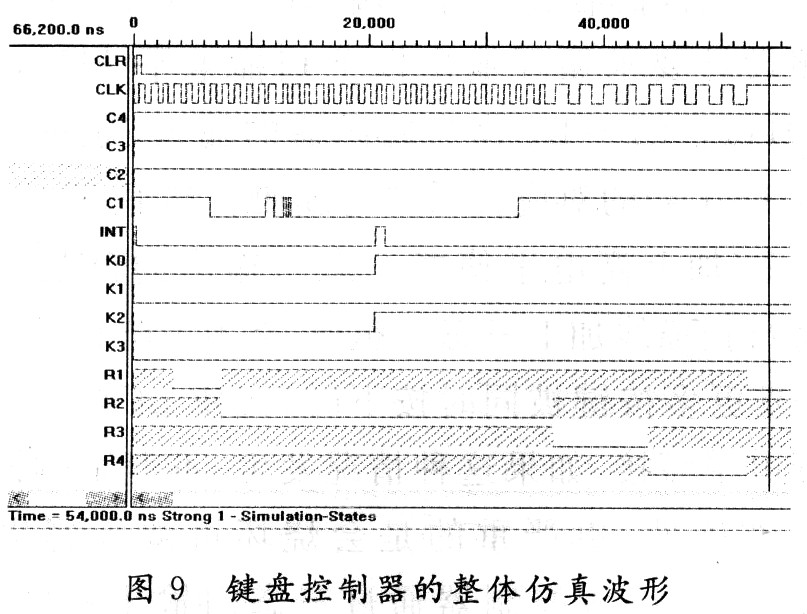

利用 Quartus 11 6.0 和 Modelsim6.1 軟件系統在MAX3000A 系列可編程器件上使用了 50%左右的資源實現了對AD574 的采樣、AID 轉換及數據讀取的控制。本文在 Mod-elsim6.1 軟件中進行仿真的結果分別如下圖所示。

經過驗證,電路能順利、方便地控制AD574 的工作和運行,轉換過程和結果均符合AD574的時序邏輯和精度要求。

3. 結 語

利用 CPLD技術實現邏輯和時序的控制,在硬件電路上簡化了設計的復雜度,基于CPLD 的可編程特點,可以在不改變硬件電路整體結構的情況下對設計電路進行改造、升級和維護;在軟件程序上減少了操作指令,一定程度上提高了數據處理和讀取的速度。

電子發燒友App

電子發燒友App

評論