隨著社會(huì)經(jīng)濟(jì)的發(fā)展和生活物質(zhì)水平的提高,人們對(duì)于精神世界的追求也越來(lái)越高。該設(shè)計(jì)理念源于提高人們的生活幸福指數(shù)。在傳統(tǒng)意義上,人們往往用沖印出來(lái)的相片來(lái)記錄生活中的美好瞬間。然而伴隨電子行業(yè)的發(fā)展,包括數(shù)碼相機(jī),高像素智能內(nèi)的大量電子產(chǎn)品大行其道,足以用數(shù)碼形式將其取代。據(jù)統(tǒng)計(jì),世界上那個(gè)70%以上照片都是數(shù)碼照片,年輕一族更是喜歡以數(shù)碼形式記錄他們的生活,并且分享在網(wǎng)絡(luò)上。數(shù)碼相框同時(shí)還可以將靜態(tài)圖片提升為動(dòng)態(tài)的相冊(cè),攜帶方便,儲(chǔ)存時(shí)間長(zhǎng)遠(yuǎn),滿足于人們的需求,同時(shí)也會(huì)是一種節(jié)約型,環(huán)保低碳型的構(gòu)想。

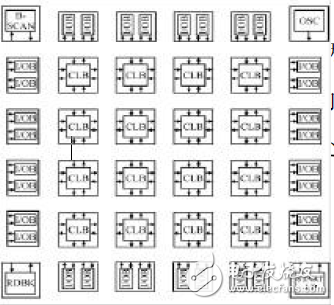

一個(gè)典型的FPGA 是有幾個(gè)部分構(gòu)成的,首先是邏輯塊(LogicBlock),Altera 公司將其稱之為邏輯陣列快(LAB)Xilinx 公司將其稱為可配置邏輯塊(CLB)。LAB 由稱之為L(zhǎng)E(Logic Element)的基本單元構(gòu)成,CLB 由稱之為L(zhǎng)C(Logic Cell)的基本單元構(gòu)成。這些就是FPGA 的邏輯資源,還有一部分是散落在各個(gè)邏輯塊之間地內(nèi)部連線,它們好比是PCB 板上的導(dǎo)線,將FPGA 內(nèi)部地各個(gè)邏輯相連接,起點(diǎn)和終點(diǎn)都是IOB(I/O Block)。另一部分就是IOB 了,IOB 是FPGA的外部物理接口,類似IC 的各引腳,當(dāng)然這里是根據(jù)用戶需要自己可以任意定義的。如今的FPGA 的IOB 已經(jīng)很強(qiáng)大, 從基本的LVTTL/LVCOMS 接口到PCI/LVDS/RSDS 甚至各種各樣的差分接口,F(xiàn)PGA內(nèi)部的I/O 實(shí)際上是分組的,但是每一組都可以靈活配置,改變上拉下拉電阻,調(diào)解驅(qū)動(dòng)電流大小,兼容5V,3.3V,2.5V,1.8V 甚至1.5V,可以滿足不同的電器特性,不同的I/O 接口物理特性以及外部硬件電路對(duì)輸入輸出信號(hào)的各種匹配要求。目前I/O 可以達(dá)到的頻率也愈來(lái)愈高,通過(guò)特定的技術(shù)數(shù)據(jù)讀取速率甚至可以達(dá)到2Gbps 現(xiàn)在越來(lái)越多的工程師喜歡FPGA,強(qiáng)大的I/O 特性也是一種原因吧。

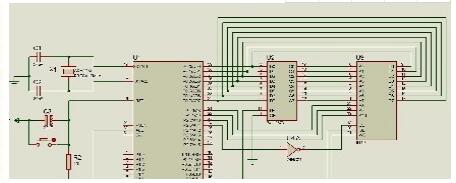

圖2-1 典型的FPGA內(nèi)部結(jié)構(gòu)圖

I/O 兼容恐怕是大勢(shì)所趨。設(shè)計(jì)IOB 的概念和技術(shù)還有很多,這里不做介紹了。還有一部分就是FPGA 內(nèi)部的功能模塊,是制造商根據(jù)實(shí)際需要放置在FPGA 內(nèi)部的。比如數(shù)字時(shí)鐘管理模塊即DCM,Xilinx 公司的FPGA 全都具有這種功能。比如相位環(huán)路鎖定。PLL 需要一個(gè)外部時(shí)鐘輸入(晶振),經(jīng)過(guò)內(nèi)部處理后(包括分頻和倍頻)可以提供在頻率和相位上都比較穩(wěn)定的一定范圍內(nèi)的時(shí)鐘。還有不得不提的內(nèi)部不占用邏輯資源的塊RAM。RAM 塊可用作為單口RAM、雙口RAM、內(nèi)容地址存儲(chǔ)器以及FIFO(first in first out)等常用存儲(chǔ)器甚至ROM,移位寄存器。這對(duì)于小量數(shù)據(jù)緩存很有用,強(qiáng)化了FPGA的應(yīng)用性。在選擇FPGA 時(shí),芯片內(nèi)部塊RAM 的資源多少也是衡量的一個(gè)重要因素。單獨(dú)塊RAM 的容量為18kbit 寬為18Bit、深度為1024,可以根據(jù)實(shí)際需要改變其位寬和深度,但有兩點(diǎn)限制:首先就是修改后塊RAM 的容量(位寬深度)不能大于單片塊RAM 容量;而且位寬最大不能超過(guò)36Bit,可以將多片塊RAM 聯(lián)起來(lái)形成內(nèi)存更大的RAM,此時(shí)只受限于芯片內(nèi)塊RAM 的數(shù)量,而不再受上面兩條原則約束。不過(guò)在Quartus 中,具體操作起來(lái)很方便。還有底層內(nèi)嵌功能單元包括內(nèi)嵌專用硬核如乘法器等。它對(duì)于數(shù)字信號(hào)的運(yùn)算處理提供極大的便利。

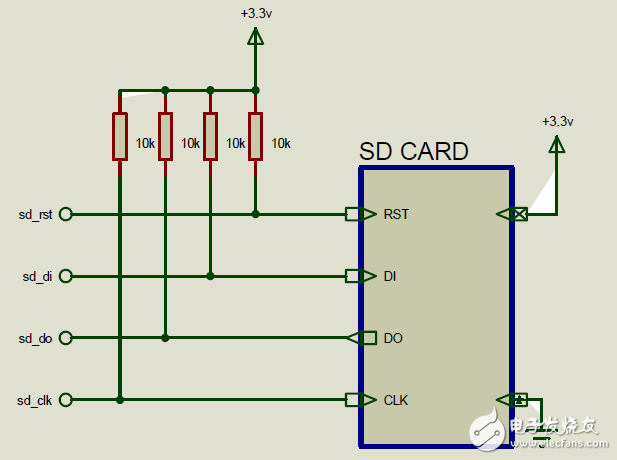

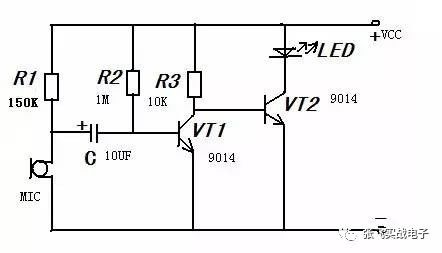

SPI 接口控制電路

圖4-1 SPI模式連接圖

該工程模塊的SPI 接口四條信號(hào)線分別定spi_cs_n,spi_clk,spi_miso 和spi_mosi。其中spi_cs_n 是數(shù)據(jù)控制使能信號(hào),當(dāng)要對(duì)芯片進(jìn)行操作時(shí),此信號(hào)低電平有效。也就是說(shuō)在同一條主線上可以連接多個(gè)SPI。spi_clk是SPI 同步時(shí)鐘信號(hào),數(shù)據(jù)信號(hào)在該時(shí)鐘的控制下進(jìn)行逐位傳輸。spi_miso 和spi_mosi 是主從機(jī)進(jìn)行通信的數(shù)據(jù)信號(hào),spi_miso即主機(jī)的輸入或者說(shuō)是從機(jī)的輸出spi_mosi 即主機(jī)的輸出或者說(shuō)是從機(jī)的輸入。

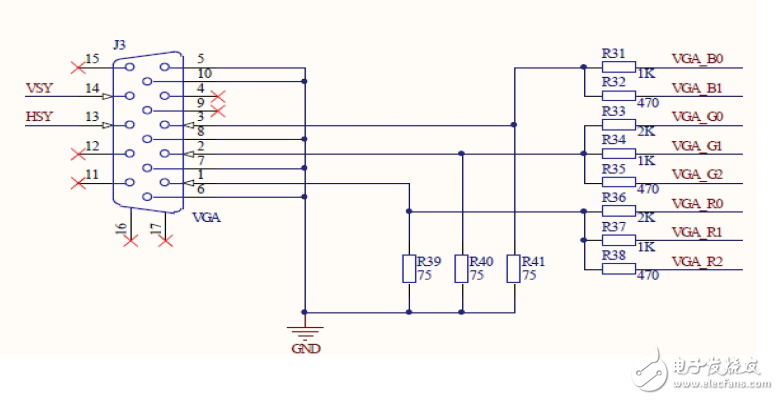

VGA 顯示驅(qū)動(dòng)模塊

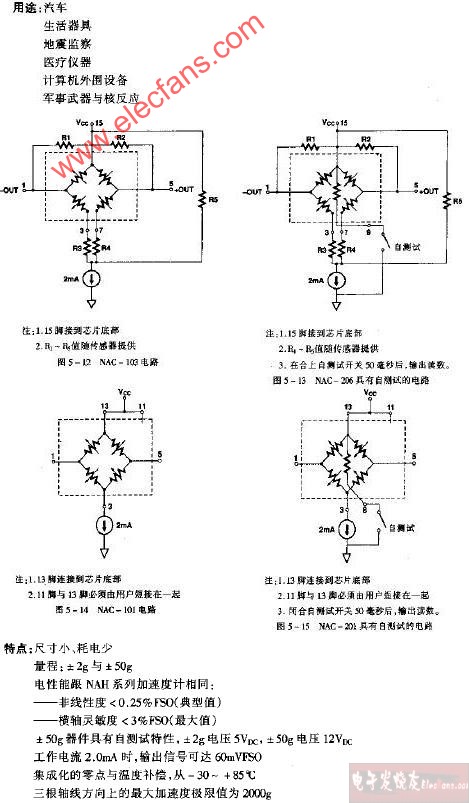

標(biāo)準(zhǔn)VGA 一共有15 針,真正用到的接口不多,只有5 個(gè),場(chǎng)同步信號(hào)和列同步信號(hào)是為了讓VGA 接收部分知道過(guò)來(lái)的數(shù)據(jù)是對(duì)應(yīng)哪一行哪那一列。還有三原色信號(hào),本課題硬件三原色信號(hào)通過(guò)連接不同的電阻后直接與I/O 接口相連(可理解為簡(jiǎn)易的DA 轉(zhuǎn)換),這樣就可以顯示256 色了。內(nèi)部VGA 與FPGA 接口如圖7-1 所示。

圖7-1 VGA 內(nèi)部簡(jiǎn)化DA

電子發(fā)燒友網(wǎng)技術(shù)編輯點(diǎn)評(píng)分析:

FPGA 器件應(yīng)用是繼單片機(jī)之后,當(dāng)今地嵌入式系統(tǒng)開發(fā)應(yīng)用中最最熱門的關(guān)鍵技術(shù)之一,并且隨著制造工藝水平的不斷提高,成本的不斷下降,F(xiàn)PGA 甚至大有替代專用ASIC 的趨勢(shì)。FPGA 使用Verilog 或VHDL 等硬件描述語(yǔ)言編程。系統(tǒng)工程所有功能全部使用FPGA 來(lái)完成,內(nèi)容包括SD 卡的讀取控制,圖片解碼,VGA 驅(qū)動(dòng)顯示等等,采用的是SF—EP1開發(fā)板,該板FPGA 使用EP1C3T144C8,配置PLL 電源電路,SD 接口,1 個(gè)256 色的VGA 通用接口,SDRAM 等。支持AS 及JTAG 配置方式,軟件平臺(tái)使用Quartus Ⅱ 9.1,從而完成10 幅800*600 的BMP 圖片循環(huán)顯示。

大家如有問(wèn)題,歡迎在評(píng)論處討論。

——電子發(fā)燒友網(wǎng)整理,轉(zhuǎn)載請(qǐng)注明出處!

----------------------------------------

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論