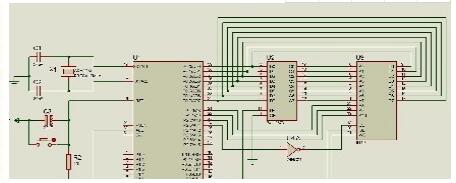

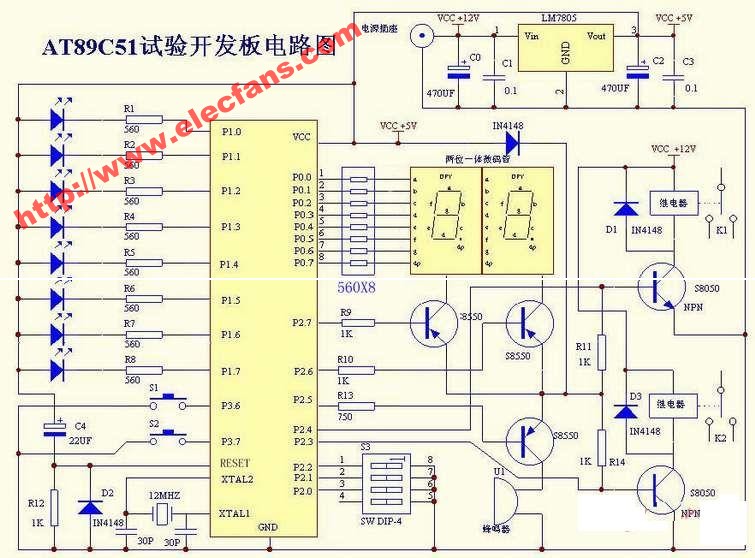

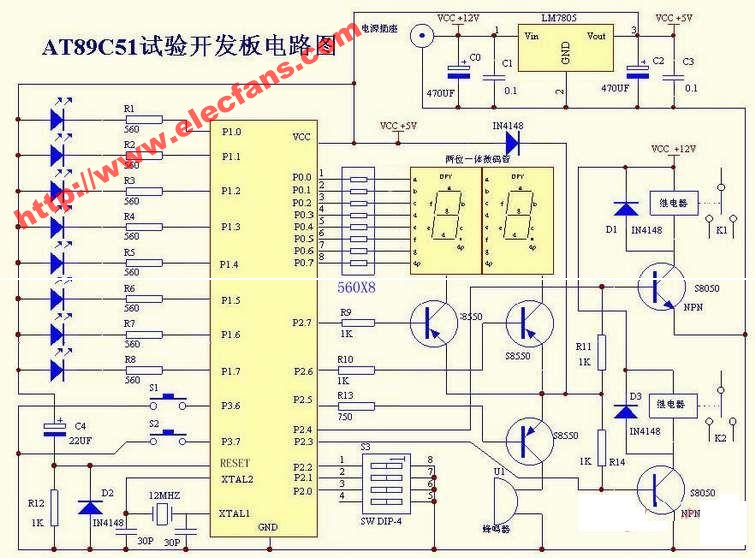

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。FPGA的開發相對于傳統PC、單片機的開發有很大不同。FPGA以并行運算為主,以硬件描述語言來實現;相比于PC或單片機(無論是馮諾依曼結構還是哈佛結構)的順序操作有很大區別,也造成了FPGA開發入門較難。目前國內有專業的FPGA外協開發廠家,開發展基本電路如下:

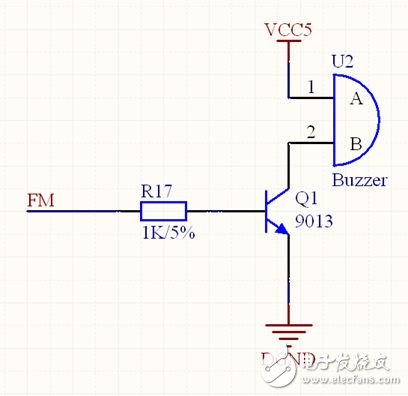

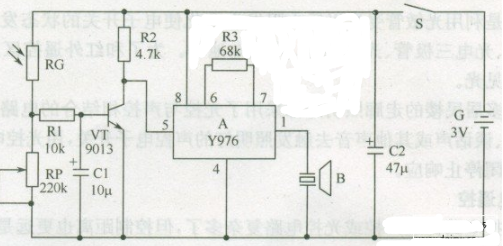

蜂鳴器電路如圖3.47所示。FM信號由FPGA的I/O口控制。當FM為高電平時,Q1的BE導通,則CE導通,蜂鳴器的5V和GND形成回路,發出聲音。當FM為低電平時,Q1的BE斷開,則CE斷開,蜂鳴器的5V和GND斷開,因此沒有電流流過蜂鳴器,蜂鳴器便不發聲。在后面的實驗中,我們可以使用PWM信號,即以固定的時高時低的電平控制Q1的導通與否,然后達到蜂鳴器的時斷時開,人耳聽到的便是不同頻率的聲響。

圖3.47 蜂鳴器驅動電路

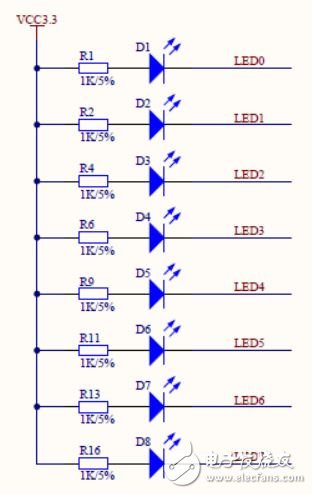

8個LED指示燈的電路如圖3.48所示,他們公共端接電源3.3V,另一端連接FPGA的I/O口。若輸出高電平,LED熄滅;若輸出低電平,則LED點亮。這8個LED的接口是與數碼管的段選信號復用的。

圖3.48 8個LED指示燈電路

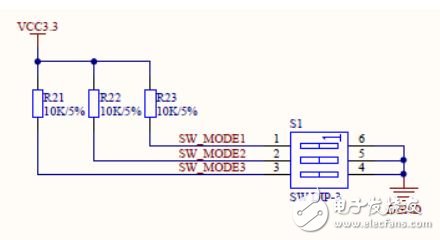

3位的撥碼開關電路如圖3.49所示。

圖3.49 撥碼開關電路

如圖3.50,我們可以對照實物,默認3個撥碼開關應該都是撥向左側(即1、2、3標記側),在電路圖上就是VCC3.3上拉一側。就是說,默認情況下,3個連接FPGA的I/O口的信號SW_MODE1、SW_MODE2、SW_MODE3均為高電平。若撥碼開關被撥到右側(即標記ON側),則采集到的輸入就是低電平了。

圖3.50 撥碼開關實物照片

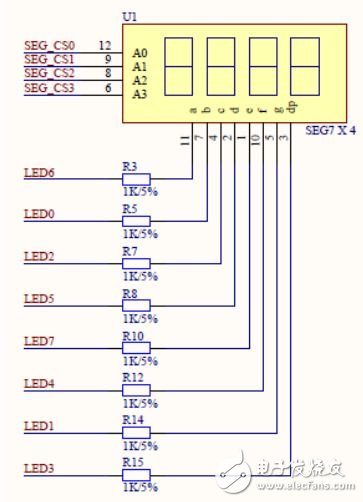

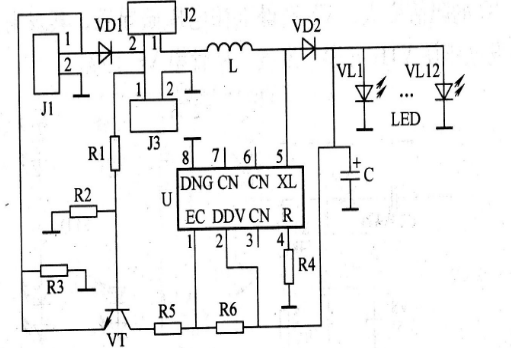

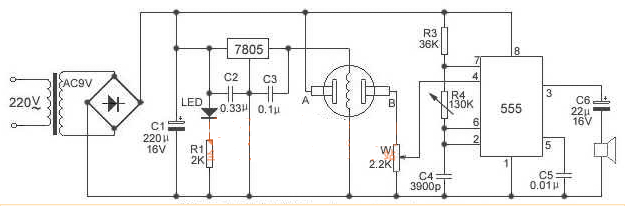

數碼管電路如圖3.51所示。SEG_CS0、SEG_CS1、SEG_CS2、SEG_CS3這4個信號對應控制數碼管4位顯示的片選信號,低電平有效,若4個片選信號都為0,則4位數碼管都能點亮顯示。LED0-7則也被復用為數碼管的段選信號,控制一個數碼管的對應段LED的亮滅狀態,這一組信號對于4位的數碼管是共用的。在實際控制時,我們一般會分時點亮需要顯示的各個位數碼管,只要時間控制得合理,人眼是很容易被“蒙騙”的,我們很容易就能看到4個不同的數字顯示在數碼管上。

圖3.51 數碼管驅動電路

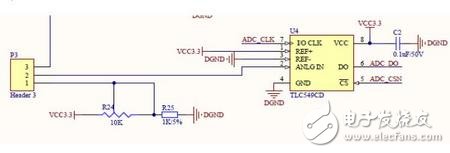

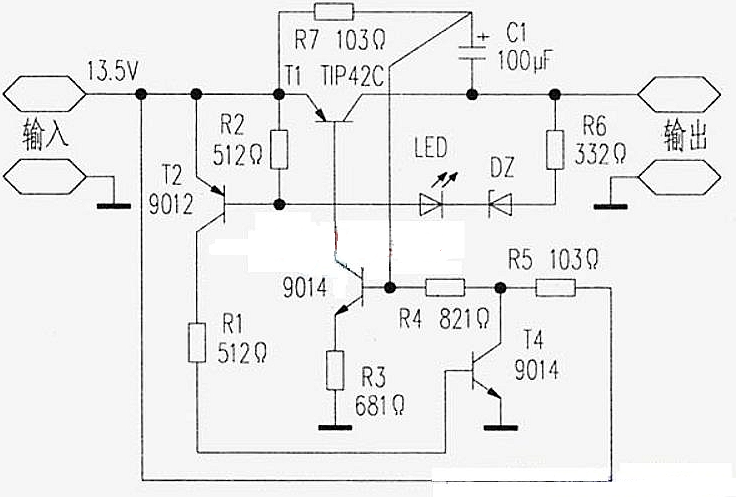

A/D芯片的電路如圖3.52所示。它通過一個單向(從A/D芯片到FPGA)數據傳輸的SPI接口與FPGA相連。FPGA通過這組SPI接口讀取當前模擬電壓值。為了得到不同的模擬電壓值,我們的板子在A/D芯片的模擬輸入端設置了一個3.3V的分壓電阻,當跳線帽連接了P3的1-2引腳時,調節可變電阻R24的阻值便能改變當前A/D采樣的數據。跳線帽若連接P3的2-3引腳,則AD芯片的輸入模擬電壓來自于D/A芯片的當前輸出。

圖3.52 A/D芯片驅動電路

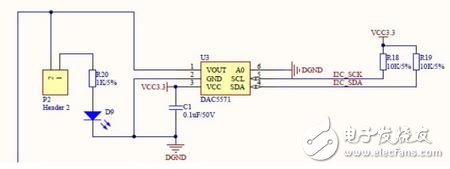

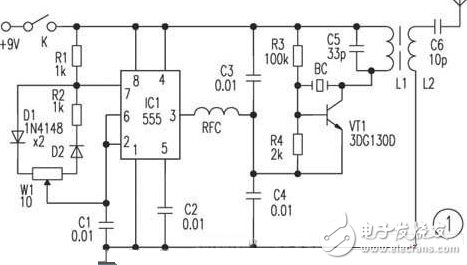

D/A轉換電路如圖3.53所示。這個D/A芯片通過I2C接口與FPGA連接,FPGA通過這組I2C接口輸出數據,相應D/A芯片的VOUT輸出模擬電壓值。若跳線帽連接P2的1-2引腳,則不同的模擬電壓值輸出驅動D9指示燈呈現不同的亮度。

圖3.53 D/A芯片驅動電路

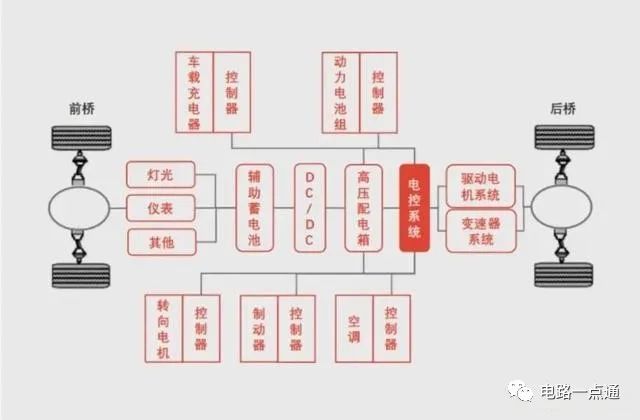

FPGA(現場可編程邏輯器件)產品的應用領域已經從原來的通信擴展到消費電子、汽車電子、工業控制、測試測量等廣泛的領域。而應用的變化也使FPGA產品近幾年的演進趨勢越來越明顯:一方面,FPGA供應商致力于采用當前最先進的工藝來提升產品的性能,降低產品的成本;另一方面,越來越多的通用IP(知識產權)或客戶定制IP被引入 FPGA中,以滿足客戶產品快速上市的要求。此外,FPGA企業都在大力降低產品的功耗,滿足業界越來越苛刻的低功耗需求。

電子發燒友App

電子發燒友App

評論