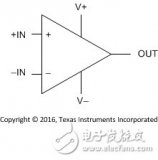

TLV3501管腳/引腳配置:

SO—8:腳1:NC

腳2:反相輸入端

腳3:同向輸入端

腳4:負電源輸入端

腳5:NC

腳6:輸出端

腳7:正電源輸入端

腳8:關斷信號控制端

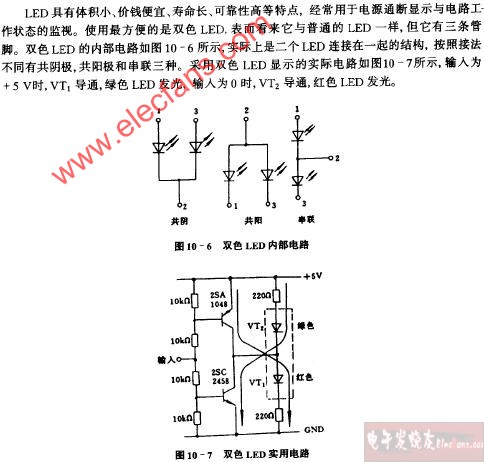

對于SOT23-6封裝由上圖可以看出引腳1是由定向的包裝標記。 SO-8比SOT23-6封裝多了兩個NC引腳,NC引腳為空腳,沒有內部的電路連接。

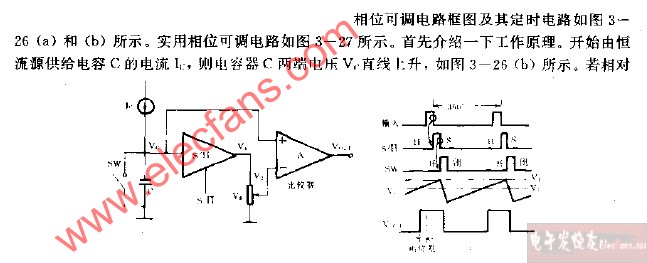

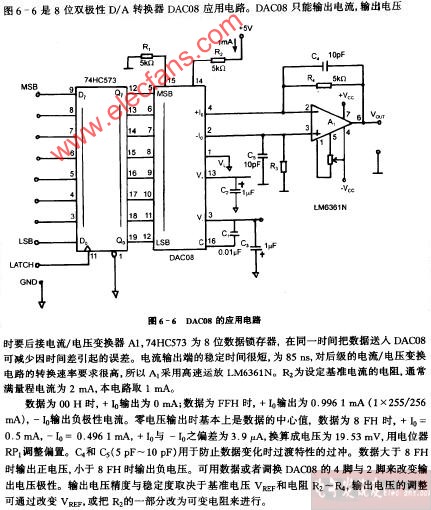

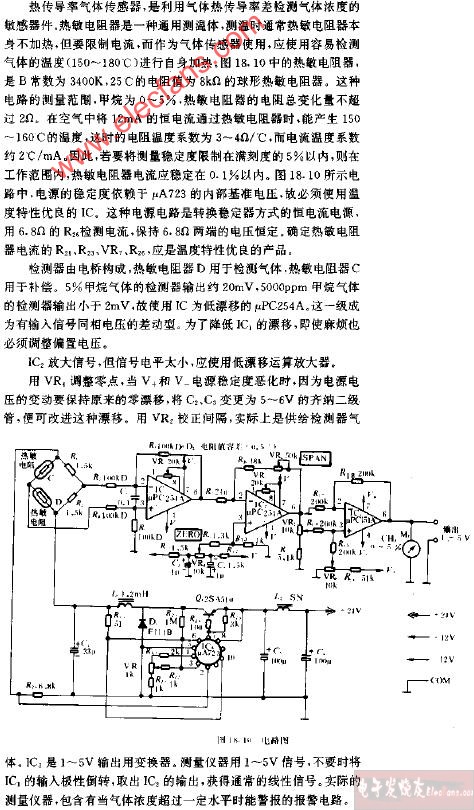

TLV3501應用電路:

TLV3501和TLV3502均配備高速響應,包括內部的滯后,以提高抗噪性能與擴展0.2V超出電源軌的輸入共模范圍為6mV。

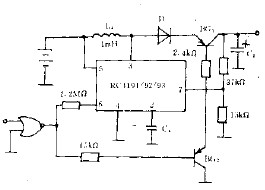

關斷

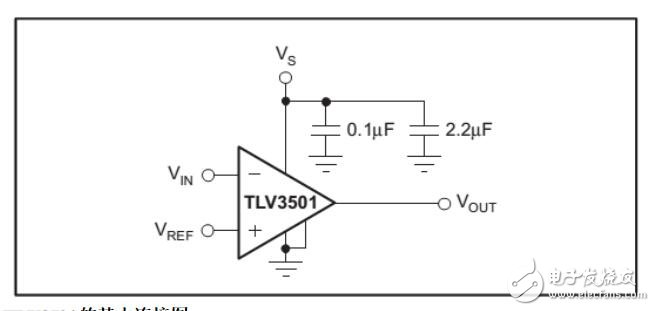

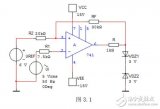

一個停機引腳允許器件進入空閑狀態時,它是不使用。當關斷引腳為高電平時,芯片的電流大約為2μA,輸出變為高阻抗。當關斷引腳為低電平時,TLV3501是有效的。當不使用TLV3501關機功能,只需連接關斷引腳到最負電源,如圖1。大約需要100ns的走出來的關斷模式。該TLV3502不具備關斷功能。

TLV3501應用電路圖

工作電壓

TLV3501比較器用于指定從+2.7V至+5.5 V單電源(或±1.35V雙電源至±2.75V)在-40°C至+125°C的溫度范圍內時芯片運行低于這個范圍時不是特定的性能。

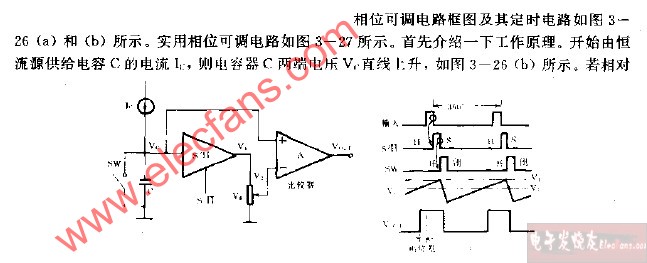

增加外部遲滯

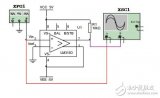

該TLV350x擁有強勁的性能與良好的布局使用性。然而,比較器輸入具有指定的偏移電壓(±5mV的)范圍內的小抗干擾能力。對于緩慢移動的或有噪聲的輸入信號時,比較器輸出可以顯示多個開關作為輸入信號移動的開關閾值。在這種應用中,TLV350x的內部遲滯的可能為6mV或更大。在更大的抗噪性需要的情況下,外部滯后可通過添連接少量的反饋到正輸入。圖2顯示了用于引入額外的滯后為25mV,共計31mV滯后5V單電源供電時的典型拓撲。總滯后是由下式

切換比較器的輸出所需要的轉變電壓的值,通過增大閾值區域,從而降低噪聲干擾。

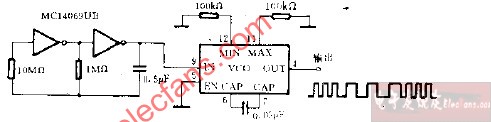

過電壓保護

芯片的輸入會通過“靜電外釋”二極管,如果輸入電壓超過電源約300mV時將受到保護。瞬時電壓大于電源300mV是可以的,可以通過串聯一個小的電阻到芯片,將輸入電流限制在10mA,如圖3。

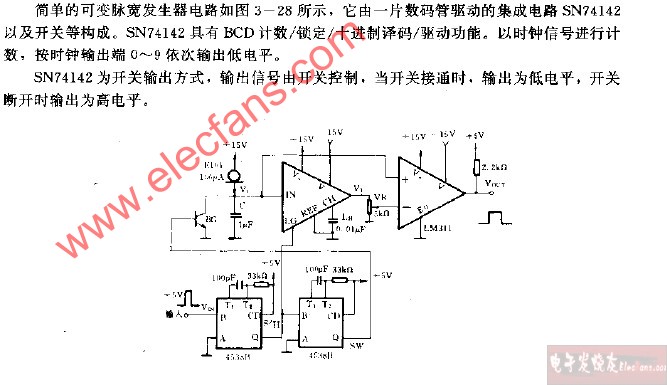

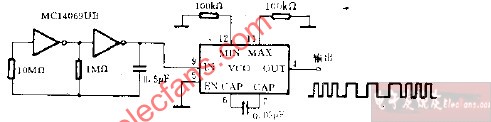

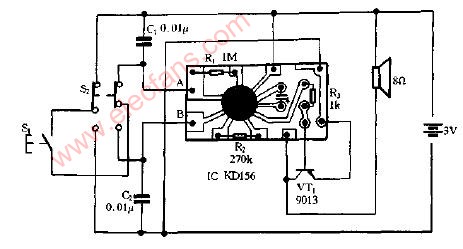

TLV350x可以很容易地配置為簡單和廉價的弛張振蕩器。在圖4中,R2的網絡設置在三分之一到三分之二的跳閘閾值。因為這是一個高頻電路,電阻器的值是相當低,以最小化電容的影響。三分之一的V +的三分之二之間的正輸入端候補取決于輸出是否低或高。充電時間(或放電)是0.69R1C。因此,該期間是1.38R1C。為62pF和圖4中所示1kΩas,輸出被計算為10.9MHz。這種電路的一個實施振蕩在9.6MHz。寄生電容和元件容差講解理論與實際性能之間的差異

PCB布局

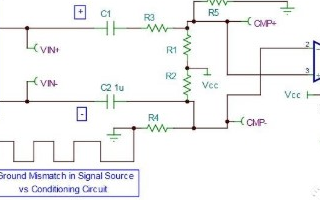

對于任何高速比較器或放大器,正確的設計和印刷電路板(PCB)布局可以讓芯片達到最佳性能。有源輸入如果增加多余電容或不正確的接地,會限制高速比較器的最大性能。從信號源到比較器的輸入電阻最小化是必要的,以便最大限度地減少整個電路的傳播延遲。隨著輸入電容的源電阻產生的RC濾波器,延遲電壓變化在輸入,并降低了高頻信號的振幅該TLV350x隨著從輸入引腳的電容至地的結果在幾個電容皮法。

用于電源旁路電容的位置和類型是高速比較器的關鍵。建議的2.2μF鉭電容器不需要像靠近器件為0.1μF的電容,并且可以與其他設備共享。該2.2μF電容緩沖對紋波電源線和0.1μF的電容提供高頻時轉換為比較器的開關。 在高頻電路中,對于直流在相同的電位快速的上升和下降電壓差可以看做一個瞬態開關,為了減少這種影響,一個接地平面通常被用來減小電路板內的電壓電位差。一個接地平面具有降低對電路板寄生電容的影響的優點,通過提供一種更可取的路徑的電流流過。有超過一個接地平面上的信號跡線,在高頻率的返回電流(在接地平面)的傾向右下的信號路徑流動。接地平面(如簡單的通孔引線和通孔)增加平面的電感,使得在較高頻率上它不那么有效。在地平面上進行必要的休息過孔應隨機分布。

電子發燒友App

電子發燒友App

評論