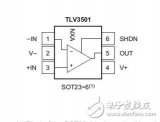

本文以TLV3501滯回比較器電路設計為示例,簡單為您講解滯回比較器電路設計的方法與思路,希望對您設計比較器電路有所幫助。

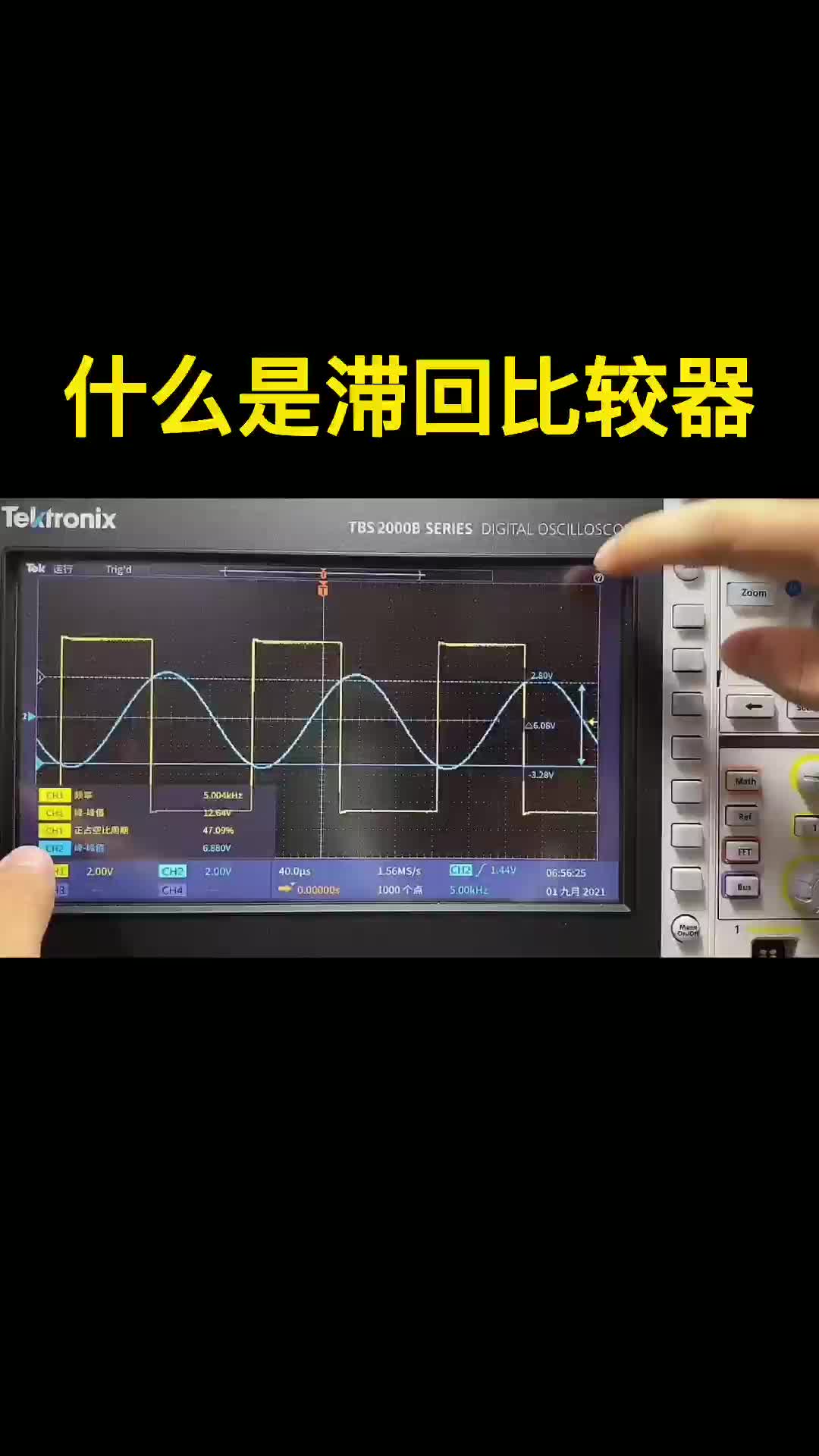

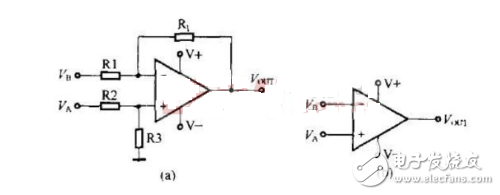

什么是滯回比較器?

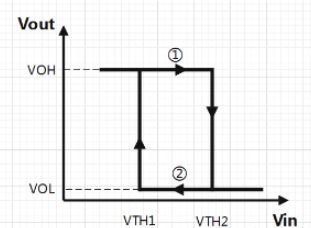

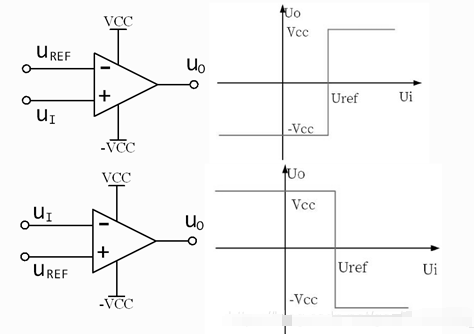

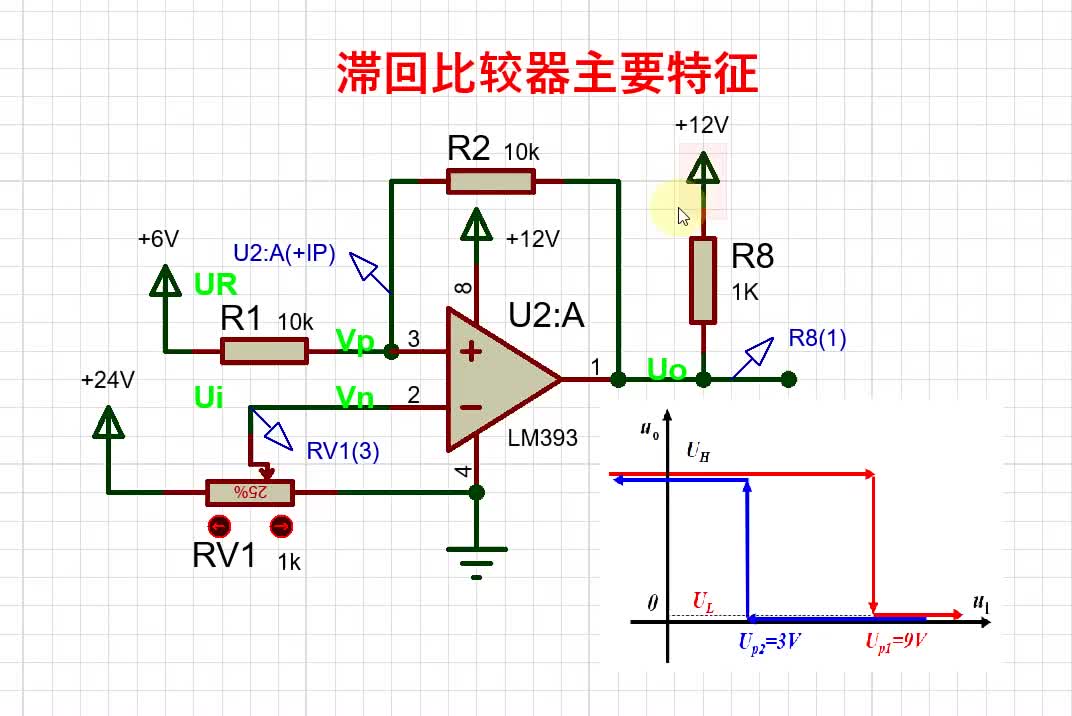

滯回比較器:又稱施密特觸發器,其抗干擾能力強,如果輸入電壓受到 干擾或噪聲的影響,在門限電平上下波動,而輸出電壓不會在高、低兩個電平間反復的跳動。

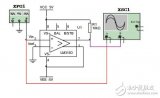

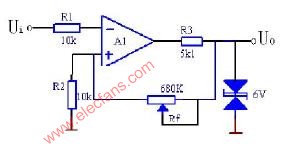

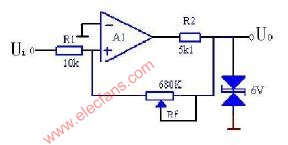

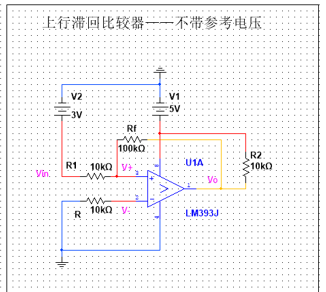

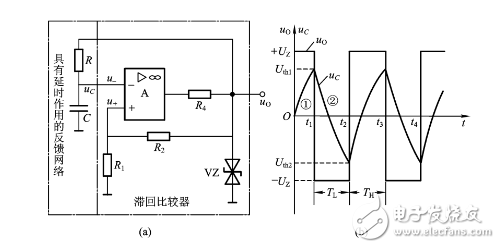

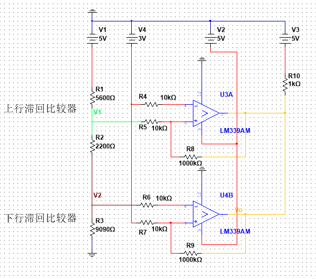

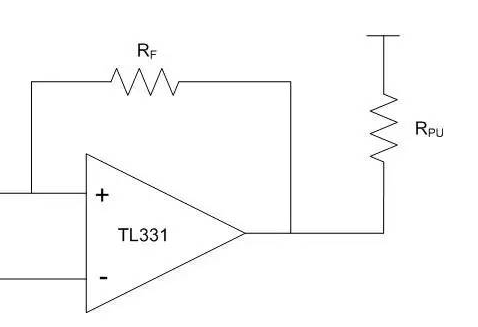

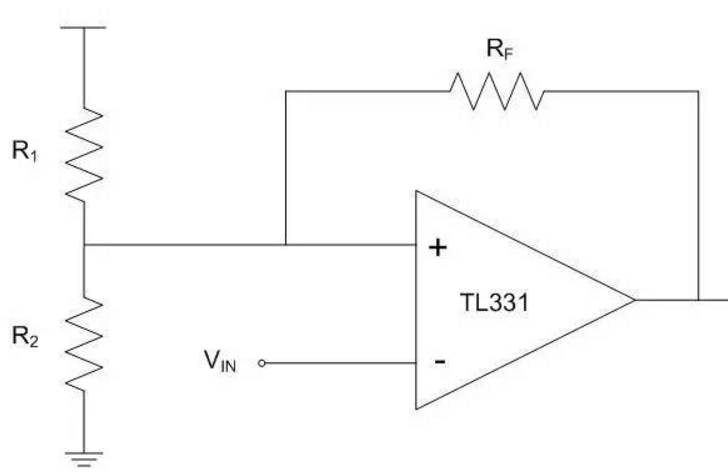

滯回比較器電路圖:

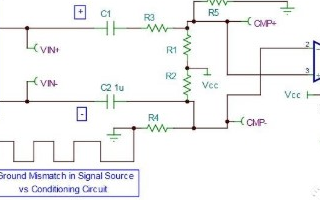

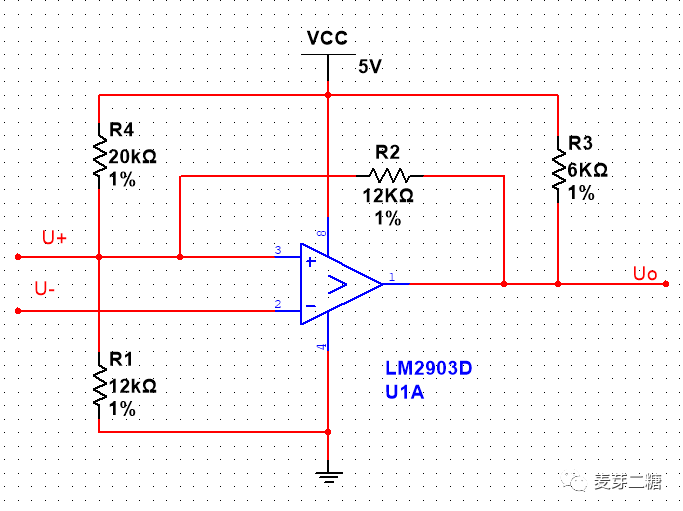

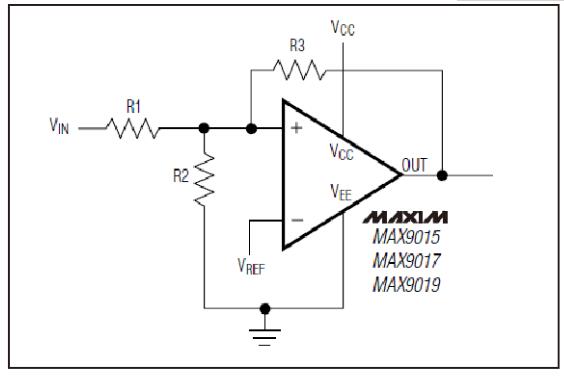

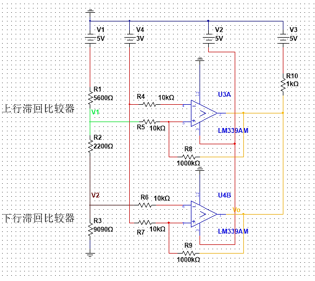

滯回比較器電路設計理論分析及計算:

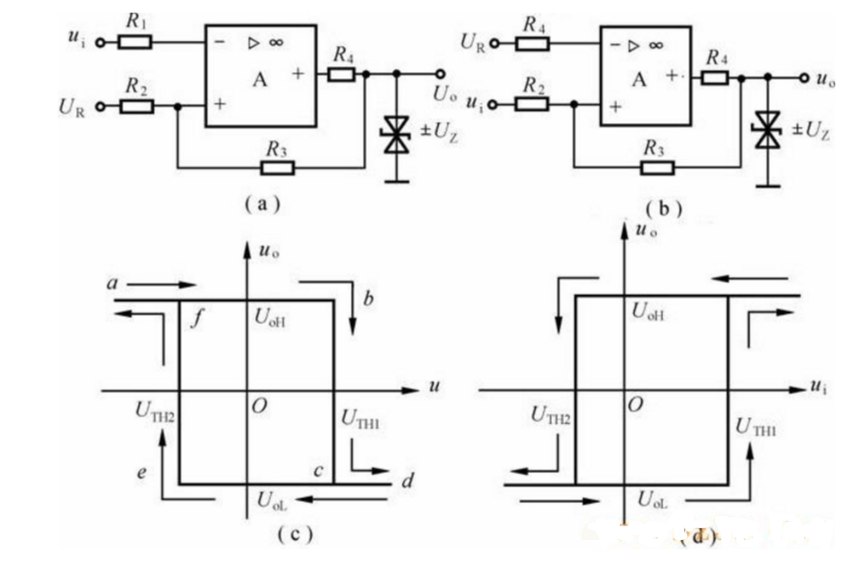

輸入電壓UI經電阻R1加在集成運放的反向輸入端,參考電壓UREF經電阻R2接在同向輸入端,此外從輸入端通過電阻RF引回同向輸入端。電阻R和背靠背穩壓管VDZ的作用是限幅,將輸出電壓的幅度限制在±UZ。

利用疊加原理可求得同向輸入端的電位為:

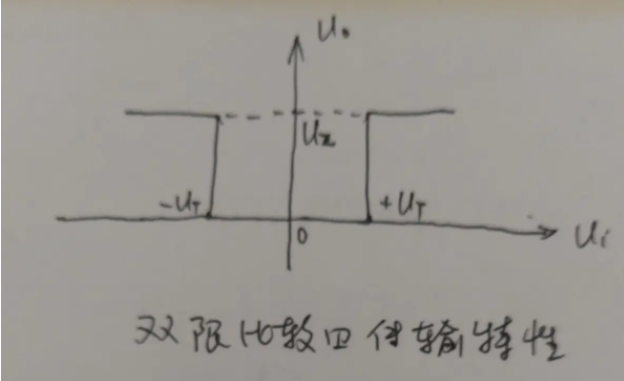

若原來U0=+UZ,當UI逐漸增大時,使U0從+UZ跳變為-UZ所需的門限電平用UT+表示,由上式知

若原來的U0=-UZ,當UI逐漸減小,使U0從-UZ跳變為+UZ所需的門限電平用UT-表示,則

由R=30kOhm,R2=20kOhm,UREF=6V,帶入以上公式可以得到,UT+=5V,UT-=2V,即當UI增大時,在UI=5V時U0發生跳變,而當UI減小時,則在U0=2V時發生跳變。輸出波形為矩形波。

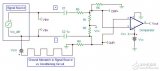

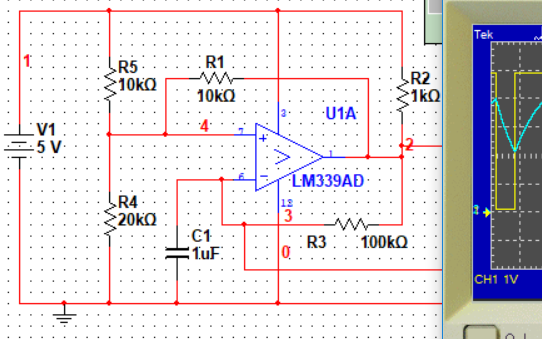

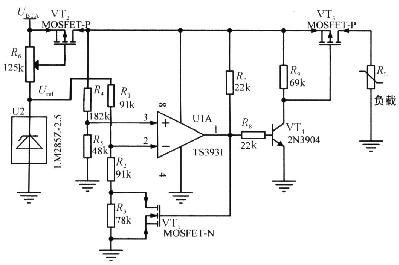

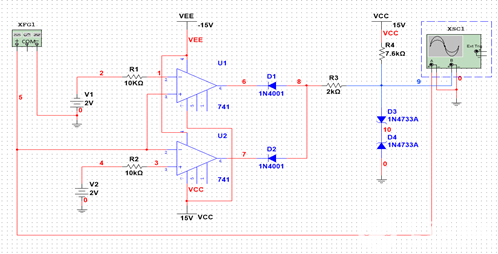

滯回比較器設計仿真結果分析,如下所示:

仿真分析:由RF=30kOhm,R2=20kOhm,UREF=6V,帶入公式(1)(2)(3)可以得到,UT+ =5V,UT- =2V,即當UI增大時,在UI=5V時U0發生跳變,而當UI減小時,則在U0=2V時發生跳變。輸出波形為矩形波

得出結論:滯回比較器效果顯著,所測得數值與理論計算數值誤差在實驗范圍之內,是有效的實驗。

?

電子發燒友App

電子發燒友App

評論