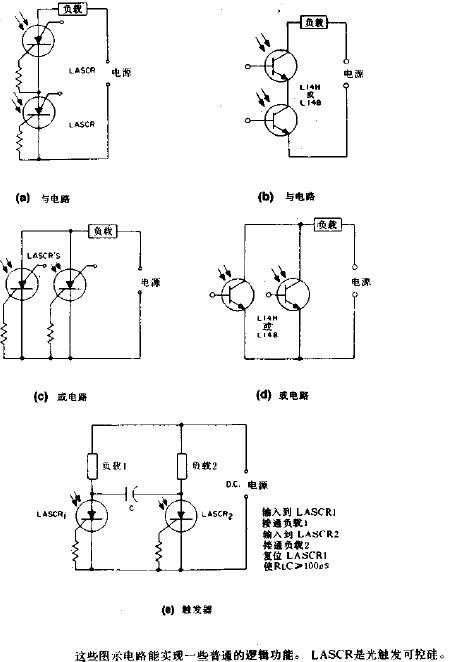

光觸發(fā)邏輯電路圖

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)>電子技術(shù)應(yīng)用>電子技術(shù)>電路圖>光電開關(guān)電子電路圖>光觸發(fā)邏輯電路圖

相關(guān)推薦

830

830

2914

2914

757

757

7

7 719

719 16

16 55

55 28

28 4638

4638

22685

22685 48178

48178 29485

29485 4

4 5279

5279

211899

211899

104785

104785

51593

51593

120321

120321

89189

89189

59977

59977

67979

67979

19808

19808

47

47 13

13 114

114 3573

3573 3505

3505 4371

4371 2788

2788 2413

2413

16998

16998 59

59 71

71 86

86 12354

12354

7022

7022

2503

2503

3156

3156

2423

2423 22

22

評(píng)論