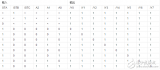

用兩個全加器構成二一十進制相減器

電子發燒友App

電子發燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網>電子技術應用>電子技術>電路圖>信號處理電子電路圖>用兩個全加器構成二一十進制相減器

相關推薦

0

0 2

2 11018

11018

1

1 15

15 53586

53586

34099

34099

2536

2536

33292

33292 12524

12524

20964

20964 4157

4157

2650

2650 2050

2050 14957

14957

65775

65775

53651

53651

44957

44957

145644

145644

52599

52599

137363

137363

28

28 37

37 12142

12142 23684

23684 5522

5522 8495

8495 1940

1940

3559

3559

評論