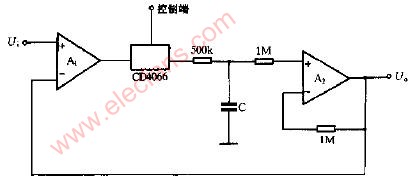

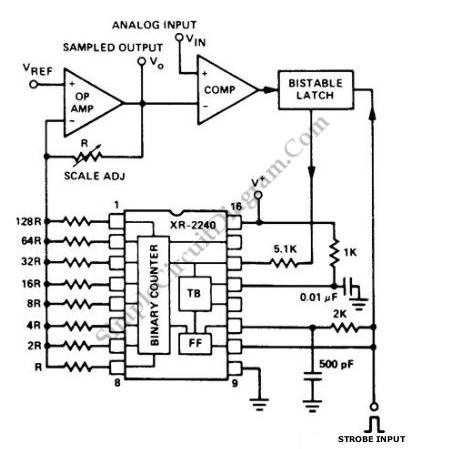

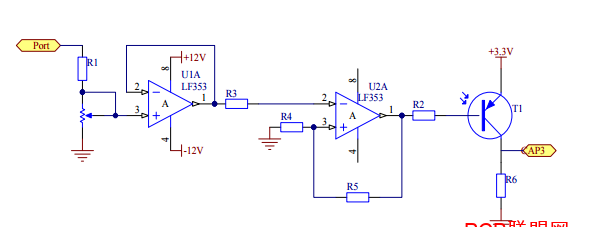

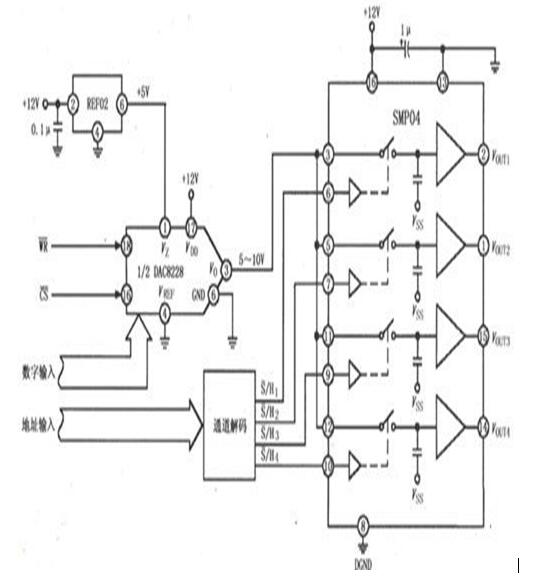

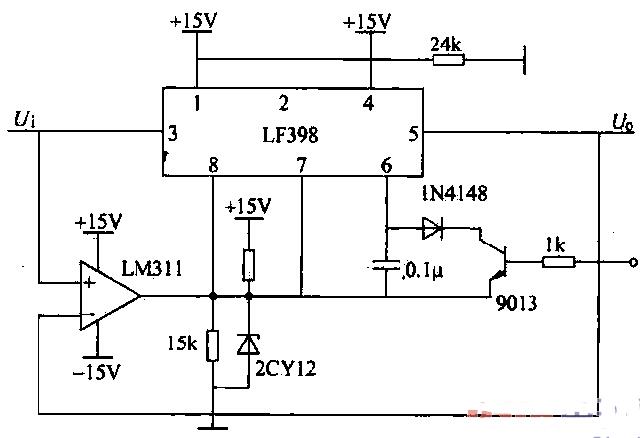

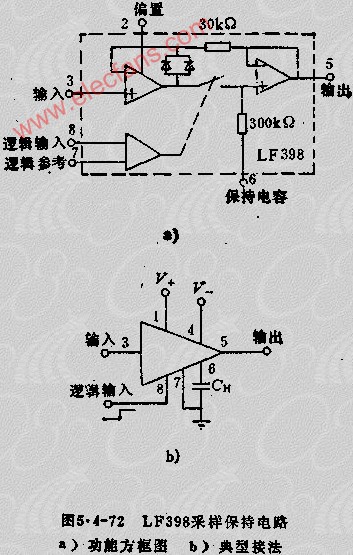

采樣信號保持電路圖

電子發燒友App

電子發燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網>電子技術應用>電子技術>電路圖>數字電路圖>采樣信號保持電路圖

相關推薦

84

84

444

444

7961

7961

1220

1220

13735

13735

93057

93057

4076

4076

4101

4101

48

48 2929

2929

62

62 64

64 21846

21846

1992

1992

3709

3709

評論