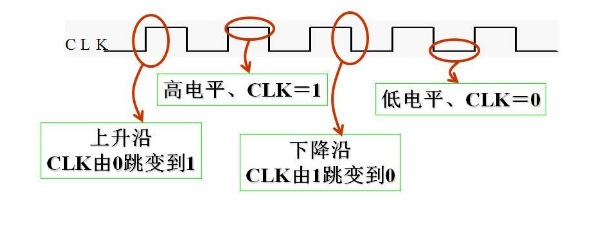

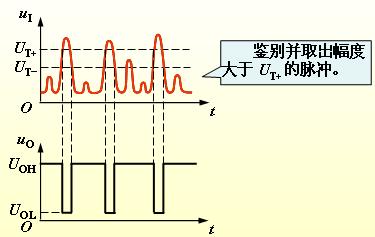

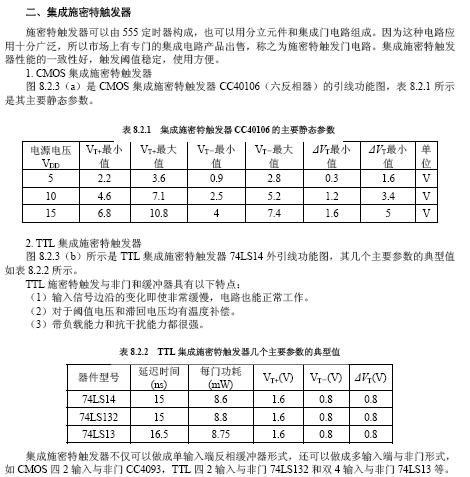

CMOS觸發器在CP邊沿的工作特性研究

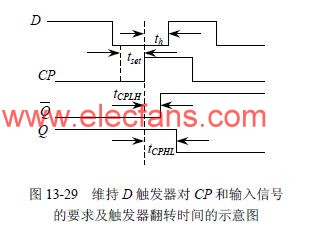

?對時鐘脈沖(簡稱CP)邊沿時間的要求,是觸發器品質評價的重要指標之一。觸發器只有在CP邊沿陡峭(短的邊沿時間)的條件下工作,才能保證其可靠性。文獻[1]指出,CMOS電路的基本觸發單元是由傳輸門和或非門組成的主從結構,輸入的數據由傳輸門引導,因此,對時鐘脈沖的上升時間和下降時間就有一定的要求。但文獻[l]對CMOS觸發器在CP邊沿的工作模式沒有進行深人研究,留下了兩個有待探索的問題:一是CP邊沿時間過長,觸發器會出現什么異常現象及為什么會出現這種現象;二是為保證觸發器正常工作,CP邊沿時間不能超過多少,它與觸發器參數的關系及計算與測量方法。這些問題的回答都依賴于觸發器在CP邊沿工作特性的研究。為此,采用標準CMOS CD4000系列、高速CMOS 74HC和74HCT系列中有關型號的觸發器為實驗樣品,觀察CP邊沿時間過長時出現的異常現象,研究異常現象出現的原因,提出CMOS觸發器在CP邊沿工作的電路模型,探索觸發器正常工作時CP邊沿時間與觸發器參數的關系,從而使文獻[1]的有關論述更加具體、深化、正確,這對CMOS觸發器的正確使用、研制和提高產品質量都有一定的理論指導意義。

??? 1 CMOS觸發器的結構與工作原理

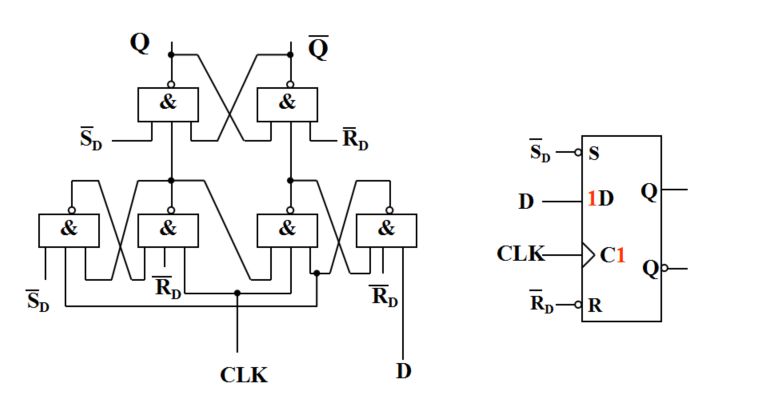

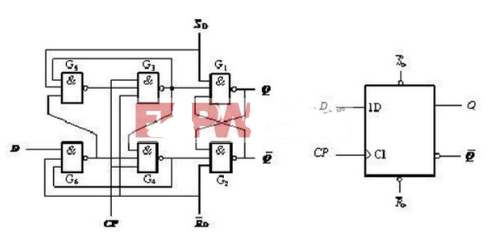

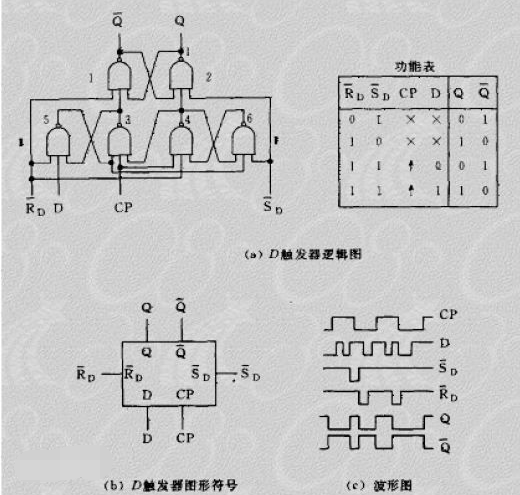

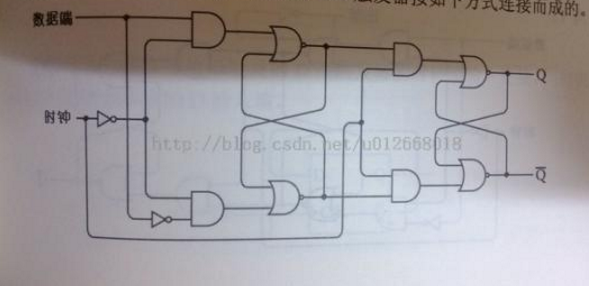

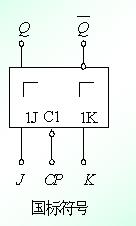

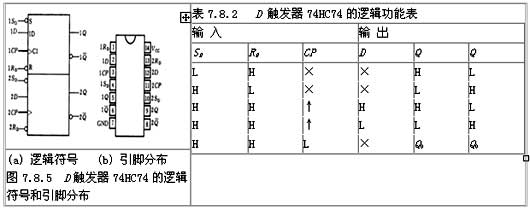

??? CMOS D觸發器足主-從結構形式的一種邊沿觸發器,CMOS T型觸發器、JK觸發器、計數單元、移位單元和各種時序電路都由其組成,因此儀以CMOS D觸發器為例進行說明。

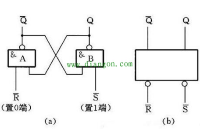

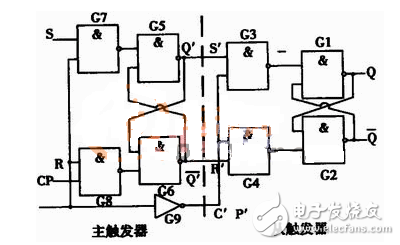

????

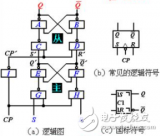

??? 圖1是用CMOS傳輸門和反相器構成的D觸發器,反相器G1、G2和傳輸門TG1、TG2組成了主觸發器,反相器G3、G4和傳輸門TG3、TG4組成了從觸發器。TG1和TG3分別為主觸發器和從觸發器的輸入控制門。反相器G5、G6對時鐘輸入信號CP進行反相及緩沖,其輸出CP和CP′作為傳輸門的控制信號。根據CMOS傳輸門的工作原理和圖中控制信號的極性標注可知,當傳輸門TG1、TG4導通時,TG2、TG3截止;反之,當TG1、TG4截止時,TG2、TG3導通。

????

??? 當CP′=0,CP′=1時,TG1導通,TG2截止,D端輸入信號送人主觸發器中,使Q′=D,Q′=D,但這時主觸發器尚未形成反饋連接,不能自行保持。Q′、Q′跟隨D端的狀態變化;同時,由于TG3截止,TG4導通,所以從觸發器形成反饋連接,維持原狀態不變,而且它與主觸發器的聯系被TG3切斷。

??? 當CP′的上升沿到達(即CP′跳變為1,CP′下降為0)時,TG1截止,TG2導通,切斷了D信號的輸入,由于G1的輸入電容存儲效應,G1輸入端電壓不會立即消失,于是Q′、Q′在TG1截止前的狀態被保存下來;同時由于TG3導通、TG4截止,主觸發器的狀態通過TG3和G3送到了輸出端,使Q=Q′=D(CP上升沿到達時D的狀態),而Q=Q′=D。

??? 在CP′=1,CP′=0期間,Q=Q′=D,Q=Q′=D的狀態一直不會改變,直到CP′下降沿到達時(即CP′跳變為0,CP′跳變為1),TG2、TG3又截止,TG1、TG4又導通,主觸發器又開始接收D端新數據,從觸發器維持已轉換后的狀態。

??? 可見,這種觸發器的動作特點是輸出端的狀態轉換發生在CP′的上升沿,而且觸發器所保持的狀態僅僅取決于CP′上升沿到達時的輸入狀態。正因為觸發器輸出端狀態的轉換發生在CP′的上升沿(即CP的上升沿),所以這是一個CP上升沿觸發的邊沿觸發器,CP上升沿為有效觸發沿,或稱CP上升沿為有效沿(下降沿為無效沿)。若將四個傳輸門的控制信號CP′和CP′極性都換成相反的狀態,則CP下降沿為有效沿,而上升沿為無效沿。下面以CP上升沿為有效觸發沿進行分析。

???

??? 2 觸發器在CP邊沿的工作特性研究

??? 2.1 觸發器在CP邊沿工作狀況的實驗觀察

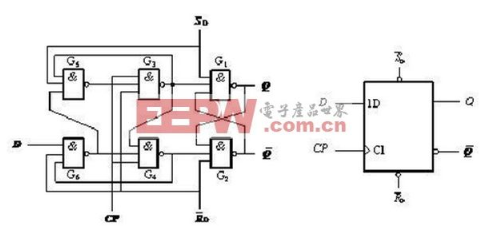

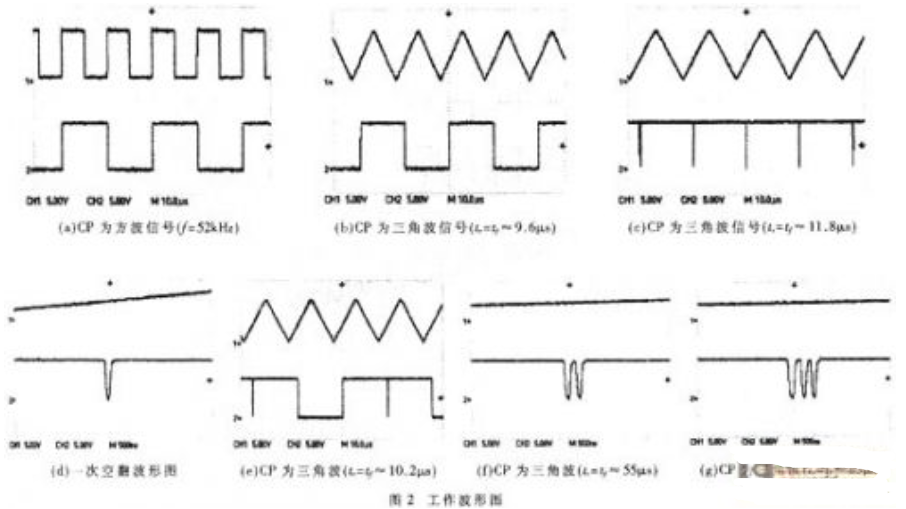

??? 把CMOS D觸發器CD4013接成計數工作方式(D端與Q端連接,即D=Q),工作電源電壓VDD=10V,由函數發生器DF1641D輸出的信號作為時鐘端輸入信號CP,用數字存儲示波器TDS1000(帶寬60MHz)同時觀察觸發器時鐘端和輸出端波形,如圖2所示,稱之為工作波形圖。

??? 圖2(a)所示是CP為頻率f=52kHz,幅度Um=10V的方波信號時所觀察到的工作波形圖(圖中上方是CP信號,下方為輸出信號,以下同)。由圖可見,對應于每一CP信號有效沿(上升沿),輸出狀態翻轉一次,計數工作正常。將上述CP信號轉變為同頻率的三角波,它的上升沿和下降沿作為CP的上升沿和下降沿,則CP邊沿時間tr=tf≈9.6μs,這時工作波形如圖2(b)所示,可見輸出波形沒有發生變化,在對應于CP上升沿某一時刻,輸出狀態翻轉一次。

??? 增大CP上升時間(調節信號頻率即可),在tr=tf≈11.8μs時,工作波形如圖2(c)所示,輸出波形在CP上升沿出現了一次空翻,即從高電平翻轉為低電平,又從低電平翻轉為高電平的兩次翻轉。若將示波器時間坐標擴展20倍,該空翻波形如圖2(d)所示。

??? 在調節CP上升時間使觸發器輸出波形由正常計數狀態向一次空翻變化時,還出現了圖2(e)所示的過渡狀態,這是在CP上升時間為tr≈10.2μs瞬間捕捉(采樣)到的工作波形圖。由圖可見,對應于CP第1個和第4個上升沿輸出空翻一次,出現異常現象。而對于第2、3、5個CP上升沿,輸出只翻轉一次,屬正常工作狀態。

??? 繼續增大CP上升時間,對應CP上升沿還會出現圖2(f)、圖2(g)所示的波形圖以及更多次空翻現象,事實上,輸出已出現振蕩現象。

??? 在對其他CMOS觸發器如CD4027(JK觸發器)、高速CMOS觸發器74HC73(JK觸發器)、74HC74(D觸發器)、74HC107(JK觸發器)和74HCT107(JK觸發器)的實驗中,也出現了類似的現象。即若CP邊沿時間過長,對應于CP有效沿,觸發器輸出狀態會出現振蕩現象,一次空翻只是一次振蕩而已,而在CP無效沿,輸出狀態不會出現異常現象。

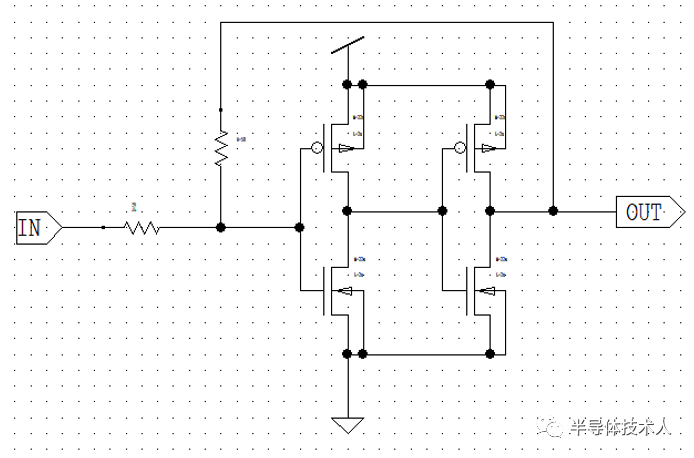

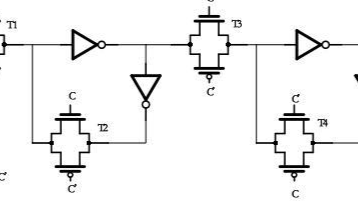

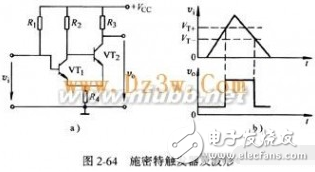

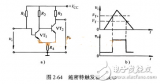

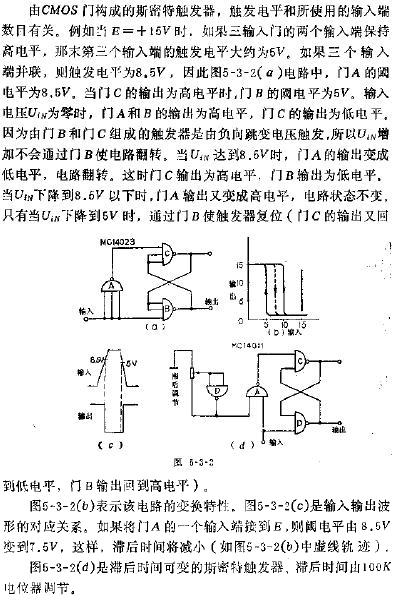

??? 2.2 傳輸門在CP邊沿的共同導通現象

??? CMOS傳輸門電路結構如圖3所示。它是由增強型NMOS管T1和PMOS管T2的源極和漏極分別相接而成,其連接處就是傳輸門的輸入端V1和輸出端V0,PMOS管襯底接工作電源電壓VDD,NMOS管襯底接地,電壓0伏,加在兩管柵極的是一對互補的控制信號C和C,它們的極性變換控制傳輸門輸入端與輸出端之間的導通與截止。

??? 通常傳輸門中NMOS管開啟電壓VTN和PMOS管的開啟電壓VTP大小相等,即VTN=|VTP|=VT,且工作電源電壓VDD>VTN+|VTP|。當C=0,c=1時,NMOS管和PMOS管的柵極和襯底之間電壓均為零,源極和漏極之間不存在導電溝道,兩管均截止,V1和V0之間是斷開的。在C由0開始上升的過程中,當它上升到NMOS管的開啟電壓VTN時,相應的C則要由高電平VDD下降同樣的幅度,即下降為VDD-|VTP|。這時NMOS管和PMOS管均開始導通。所以圖1中TG2、TG3在CP′上升到VTN時便會開始導通,盡管TG1、TG4所加的控制信號與TG2、TG3是反相的,但這時它們的NMOS管和PMOS管的柵極對襯底的電壓還在開啟電壓之上(因為VDD>VTN+|VTP|),TG1、TG4還是處于導通狀態,直到CP′上升到VDD-|VTP|(相應的CP′下降到VTN)時,TG1、TG4才會截止。可見CP′上升過程中,存在TG1、TG4和TG2、TG3共同導通的工作狀態,共同導通的時間是CP′由VTN上升到(VDD-|VTP|)所經歷的時間。

???

??? 對CP′下降過程作同樣分析可知,在CP′下降過程中,也會出現TG1、TG4和TG2、TG3共同導通的現象,共同導通的時間是CP′從(VDD-|VTP|)下降到VTN所經歷的時間。

??? 圖1中傳輸門TG1、TG4和TG2、TG3在CP上升時共同導通時間tonr可由圖4示意說明。圖中CP是觸發器時鐘端輸入信號上升沿波形,設其為線性上升,上升時間為tr。CP′和CP′分別為在CP作用下,G5、G6輸出的折線近似波形,VTH是它們的閾值電壓,通常近似為電源電壓VDD的一半,即VTH≈1/2VDD。設反相器轉換區電壓大小為△V,由于它們的傳輸特性在閾值電壓處有非常陡峭的變化,所以在CP上升過程中,當它小于(VTH-0.5△V)時,即未進入轉換區時,CP′、CP′幾乎不變。而CP電壓處在轉換區內,CP′和CP′均會急劇變化,當CP電壓上升到VTH+0.5△V以后,則CP′、CP′又幾乎不變。所以圖4中曲線CP′和CP′采用了折線近似,它們的轉折點分別為CP上升到VTH-0.5△V的t1時刻和上升到VTH+0.5△V的t2時刻,故CP′的下降時間和CP′的上升時間都等于CP在轉換區內所經歷的時間  。

。

??? VTH和VTP表示傳輸門中NMOS管和PMOS管的開啟電壓,由前面分析可知,CP上升過程中,TG1、TG4和TG2、TG3共同導通的時間是CP′由VTH升到(VDD-|VTP|)所經歷的時間,也等于CP′由(VDD-|VTP|)下降到VTN的時間,故共同導通時間為tonr:?

????

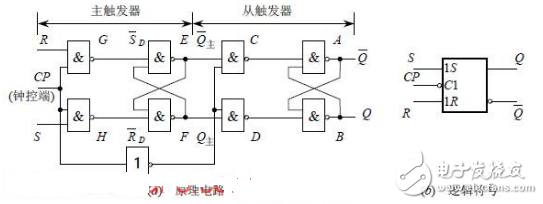

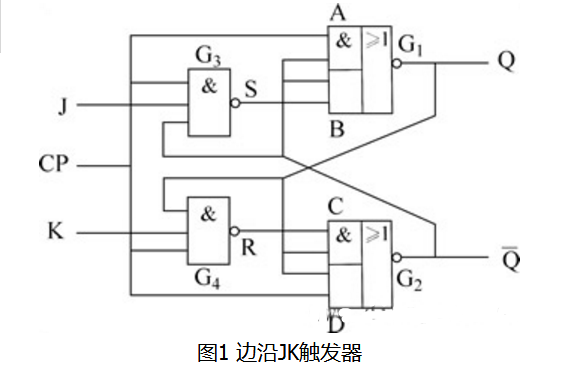

??? 2.3 觸發器在CP邊沿的工作特性

??? 2.3.1 在CP上升沿的工作特性

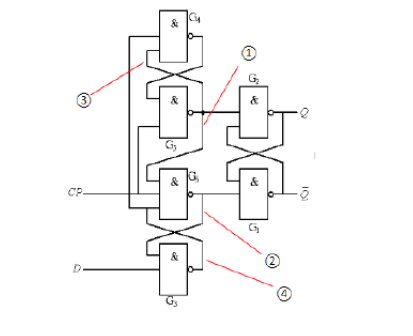

????

??? 圖1中CP′=0,CP′=1時,TG3斷開,TG4導通。若Q′=1,Q=0,則表示反相器G1中的PMOS管導通,而NMOS管截止;反相器G4中的PMOS管截止,NMOS管導通。采用MOS管的開關等效電路,則主、從觸發器之間的等效電路如圖5所示。圖中和Ron(P)是G1中PMOS管的導通電阻,Ron(N)是G4中NMOS管的導通電阻,a、b點分別為G2、G3的輸入端,C2、C3是其輸入電容,RTG3、RTG4是傳輸門TG3、TG4的導通電阻,開關K1、k4則表示其工作狀態。

??? 文獻[3]表明,觸發器最簡單的版圖布局結構選取所有器件有相同的寬長比W/L,所以Ron(P)≈Ron(N)≈RTG3≈RTG4=R,C2≈C3=C,在CP′上升沿傳輸門共同導通時間階段tonr內,主、從觸發器間的等效電路如圖6所示。這是一個含有兩個同類儲能元件的二階電路,固有頻率只可能是兩個不相等的負實根,電路的響應是欠阻尼的,利用拉普拉斯變換,可以求得a、b兩點電壓分別為:?

????

??? 式中T=RC是反相器G1~G4中MOS管的導通電阻與輸入電容的乘積。

??? 可以畫出ua(t)和ub(t)的波形如圖7所示。式(3)和圖7(a)表明,在tonr期間,門G2的輸入電壓大于閾值電壓,且在邏輯1區,從而通過G2的輸出保證G1中PMOS管導通。式(4)和圖7(b)表明,G3的輸入電壓將趨向閾值電壓0.5VDD,一旦該電壓進入閾值電壓附近的轉換區范圍內,則G3被偏置在放大工作狀態,對輸入信號起放大作用。目前生產的CD4000系列和74HC系列的CMOS電路都采用帶緩沖級的結構,線性增益很高,干擾信號或電路內部的噪聲擾動會被放大并經G4又反饋到G3輸入端,形成強烈的正反饋過程。因而出現了圖2中的異變現象,直到CP′繼續上升,傳輸門的共同導通時間結束,TG4截止(圖6中K4斷開)時為止。

??? 在Q′=0,Q=1的條件下進行同樣的分析,可得到類似的結果,這時:

????

??? 式(5)所表示的G2輸入電壓小于閾值電壓,在邏輯0區,從而通過G2的輸出保證G1中NMOS管的導通,使Q′=0;而式(6)所表示的G3輸入電壓也會趨向閾值電壓0.5VDD,使輸出出現異變現象。

???

??? 2.3.2 在CP下降沿的工作特性

??? 在CP′=1,CP′=0時,TG3導通,TG4截止,主、從觸發器之間工作的等效電路如圖8所示。這時G4的輸出總是等于G3的輸入,即截止的傳輸門TG4輸出端與輸入端之間的信號相等。所以在CP下降沿,傳輸門TG4開始導通(圖中K4閉合)時,會使G3的輸出鎖定,而TG3的繼續導通對輸出不產生影響。這就是說,在CP下降沿,傳輸門的共同導通狀態不會引起觸發器輸出狀態的異常變化。

???

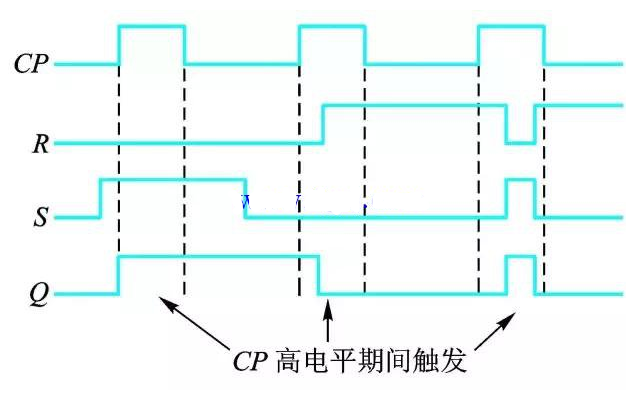

??? 2.3.3 觸發器對CP邊沿時間的要求

??? 要使觸發器在CP上升沿不出現異變現象,則要求G3的輸入電壓ub(t)變化到轉換區之前,傳輸門TG4必須截止。測試表明,轉換區電壓△V=(0.01~0.05)VDD,這就要求ub(t)變化到穩態值0.5VDD的95%~99%之前,傳輸門共同導通時間結束,TG4截止。在式(4)ub(t)表達式中,第二項指數函數的時間常數比第三項小得多,故在ub(t)趨向轉換區時,其變化規律主要由第三項指數函數的時劇常數1.39T決定。所以要求傳輸門的共同導通時間tonr為:

???

??? 本實驗測得tr應小于010.2μs,理論計算與實驗測試取得了比較吻合的結果。

??? 對于有效觸發沿是CP下降沿的CNOS觸發器,同樣分析可得要求CP下降時間tf為:

????

???

??? 3 結論與說明

??? (1) CMOS觸發器在CP邊沿會出現傳輸門共同導通的工作狀態,這種工作狀態會導致觸發器在CP有效觸發沿產生輸出狀態振蕩的異變現象。

??? (2) 為了使觸發器在CP觸發沿不產生異變現象,保證其正常的工作狀態,應對CP觸發沿提出時間要求,它除與器件自身參數有關外,還與工作電源電壓VDD有關,式(8)、式(9)表明了這種關系。

??? (3) 觸發器在CP信號無效觸發沿不會出現輸出狀態的異變現象,從這個角度講,對CP信號無效觸發沿不存在時間要求,但CP邊沿時間大,電路的功耗也大,所以也應同樣加以限制。

電子發燒友App

電子發燒友App

評論