用幾片74HC138組成多線譯碼器你知道怎么做嗎?32線的呢?本文將為你介紹使用74HC138組成32線譯碼器的方法。

74HC138

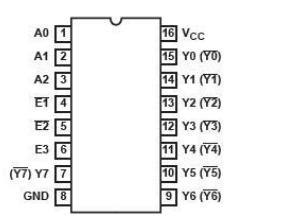

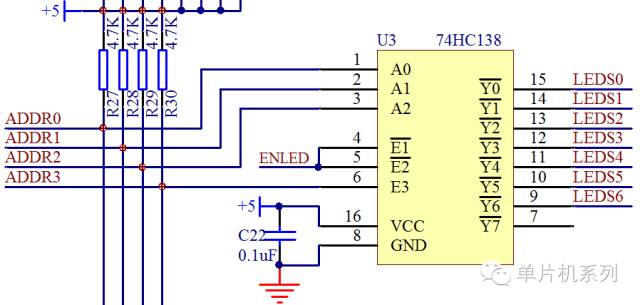

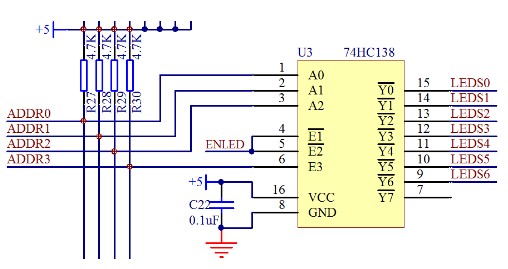

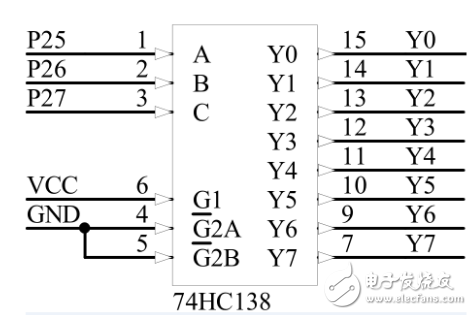

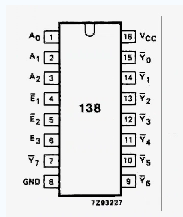

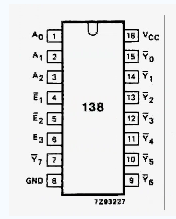

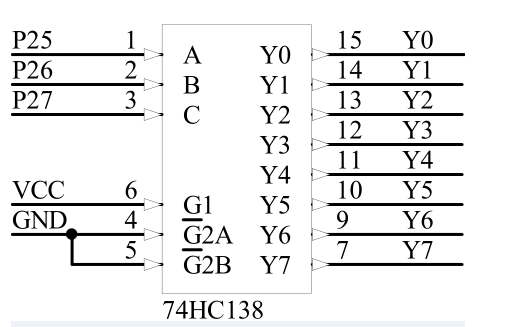

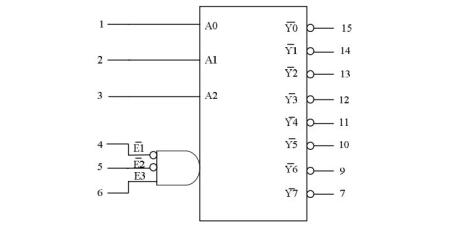

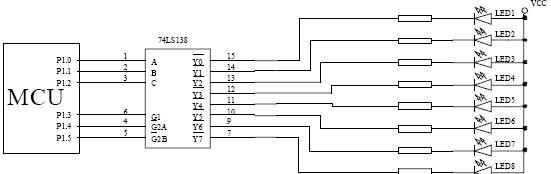

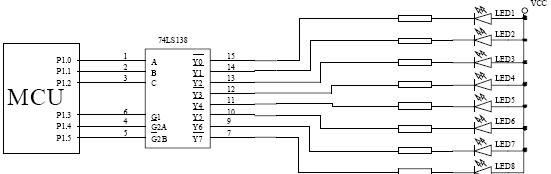

74HC138是一款高速CMOS器件,74HC138引腳兼容低功耗肖特基TTL(LSTTL)系列。74HC138譯碼器可接受3位二進制加權地址輸入(A0, A1和A2),并當使能時,提供8個互斥的低有效輸出(Y0至Y7)。

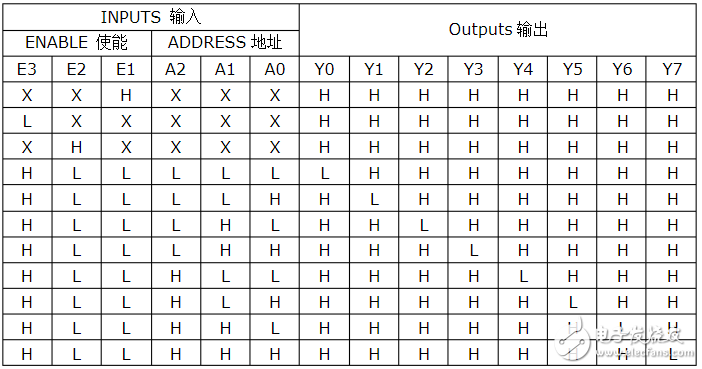

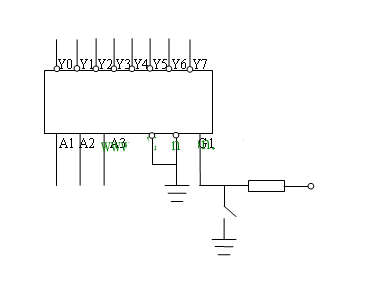

74HC138譯碼器可接受3位二進制加權地址輸入(A0, A1和A2),并當使能時,提供8個互斥的低有效輸出(Y0至Y7)。74HC138特有3個使能輸入端:兩個低有效(E1和E2)和一個高有效(E3)。除非E1和E2置低且E3置高,否則74HC138將保持所有輸出為高。利用這種復合使能特性,僅需4片74HC138芯片和1個反相器,即可輕松實現并行擴展,組合成為一個1-32(5線到32線)譯碼器。任選一個低有效使能輸入端作為數據輸入,而把其余的使能輸入端作為選通端,則74HC138亦可充當一個8輸出多路分配器,未使用的使能輸入端必須保持綁定在各自合適的高有效或低有效狀態。其邏輯真值表如下圖:

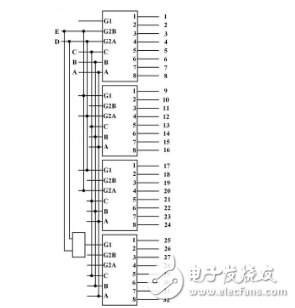

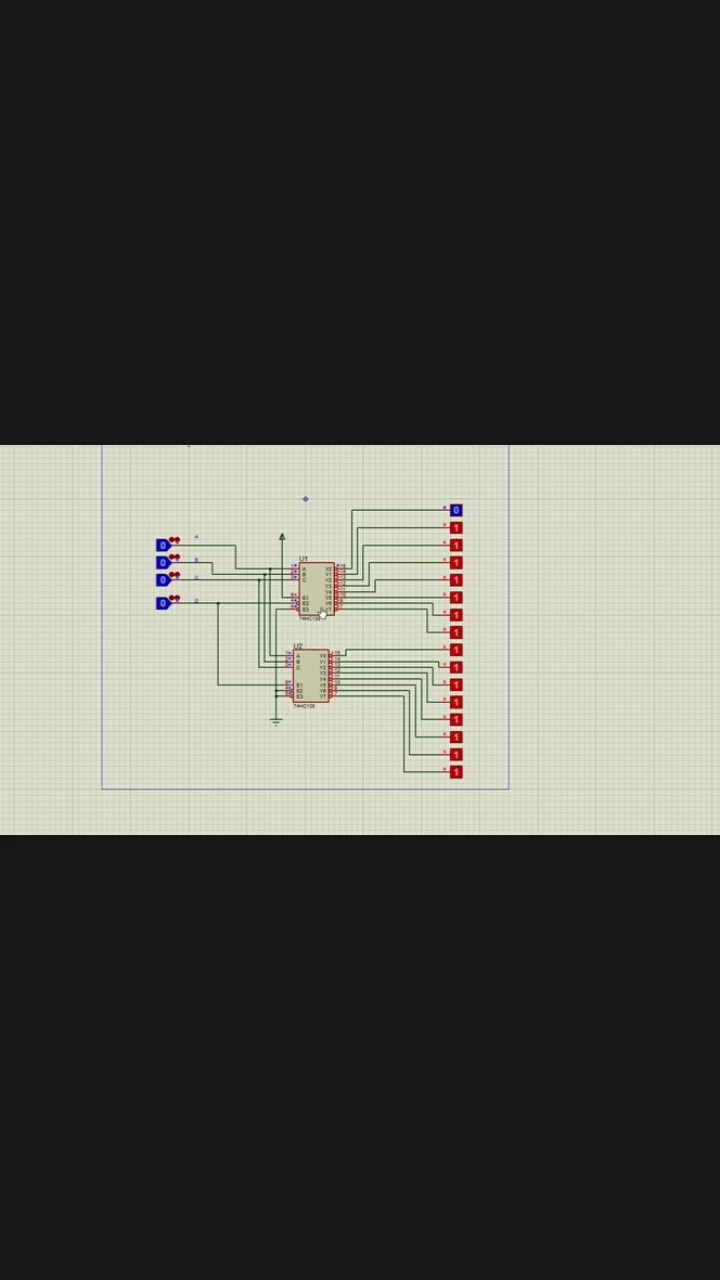

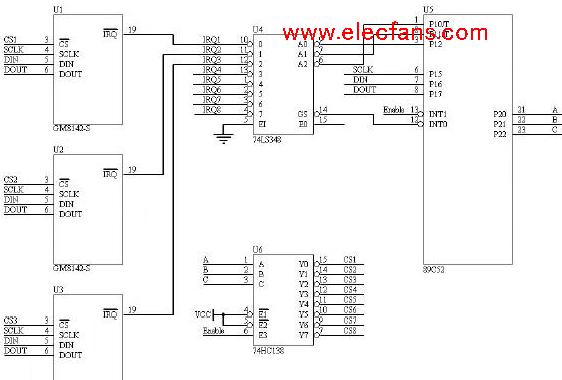

74HC138組成32線譯碼器方法

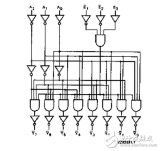

74HC138特有3個使能輸入端:兩個低有效(E1和E2)和一個高有效(E3)。除非E1和E2置低且E3置高,否則74HC138將保持所有輸出為高。利用這種復合使能特性,僅需4片74HC138芯片和1個反相器,即可輕松實現并行擴展,組合成為一個1-32(5線到32線)譯碼器。

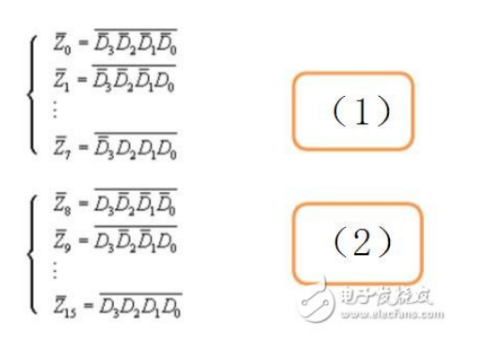

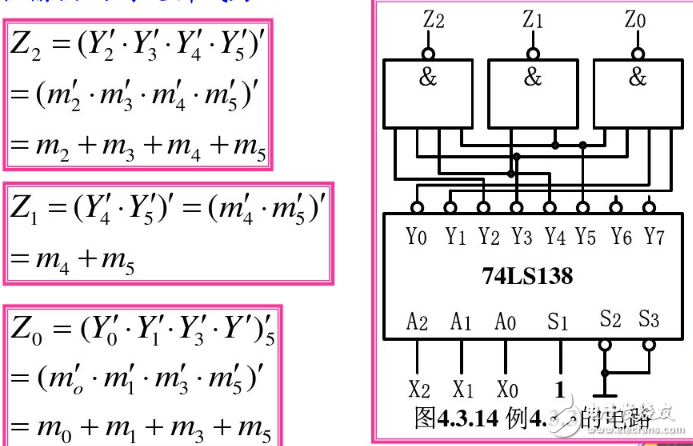

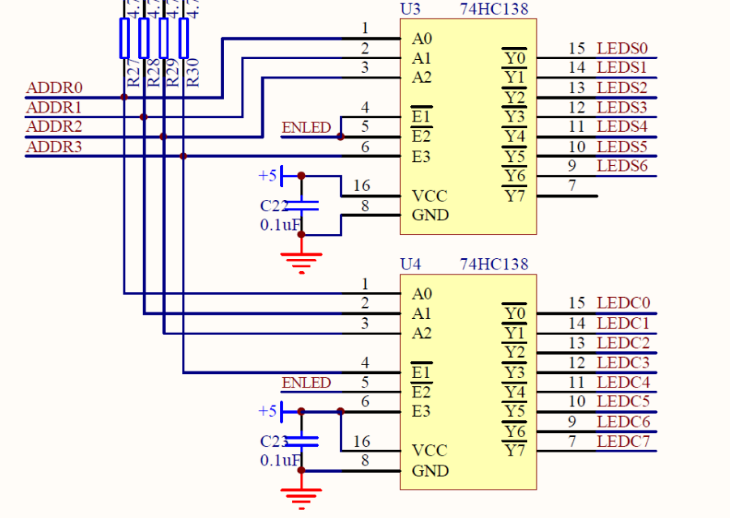

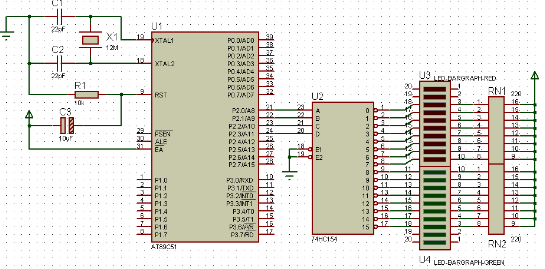

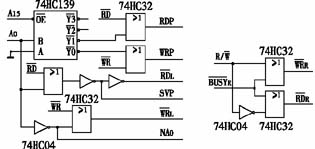

利用×138(1)的控制端S1’、S2’與×138(2)的控制電路S1相連,接入四位輸入D0、D1、D2、D3的最高為A3可以完成譯碼器的擴展。取第(1)片74HC138的和作為它的第四個地址輸入端(在同一個時間令),取第(2)片的作為它的第四個地址輸入端(在同一個時間令),取兩片的,并將第(1)片的和接至,將第(2)片的接至,如圖2-3所示,于是得到兩片74HC138的輸出分別為:

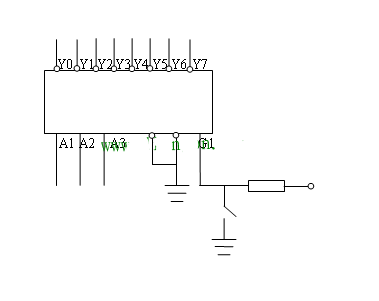

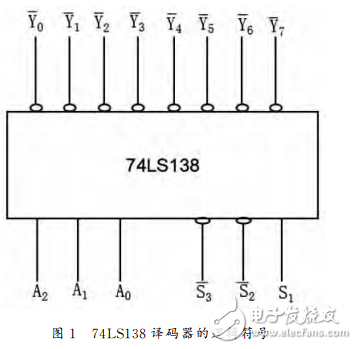

74HC138真值表

數據字節順序,D3 D2 D1 D0,通過真值表,我們可以發現,用四個74HC138組合成32線譯碼器原理關鍵在于D3

當D3 = 0時,(1)被選中,使能,(2)未被選中,全部輸出H,也即Y8~Y15全部為H,D0~D2控制Y0~Y7的低電平輸出位。1號是16位數據的低字節,2號是16位數據的高字節。高字節默認為0XFF,低字節由1號控制,顯示Y0-Y7;

當D3 = 1時,(2)被選中,使能,(1)未被選中,全部輸出H,也即Y0~Y7全部為H,D0~D2控制Y8~Y15的低電平輸出位。1號是16位數據的低字節,2號是16位數據的高字節。低字節默認為0XFF,高字節由2號控制,顯示Y8-Y15。

引腳說明

12:Gnd電源地(ground (0 V))

18-19:使能輸入端(enable inputs (acTIve LOW))

20-23地址輸入端(address inputs)

24:VCC電源正(posiTIve supply voltage)

地址/全能輸入對應輸出表

功能真值表注意:

H = 高電平(HIGH voltage level)

L = 低電平(LOW voltage level)

X = 任意電平(don’t care)

只要控制端G1、G2任意一個為高電平,A、B、C、D任意電平輸入都無效

上圖表明時第(1)片74HC138工作而第(2)片74LS138禁止,將的0000~0111這8個代碼譯成8個低電平信號。而式(2)表明時,第(2)片74HC138工作,第(1)片74LS138禁止,將的1000~1111這8個代碼譯成8個低電平信號,依次類推。這樣就用四個3線-8線譯碼器擴展成一個32線的譯碼器了

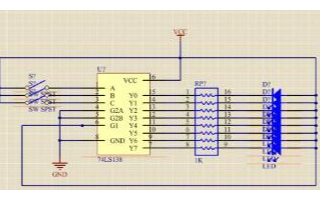

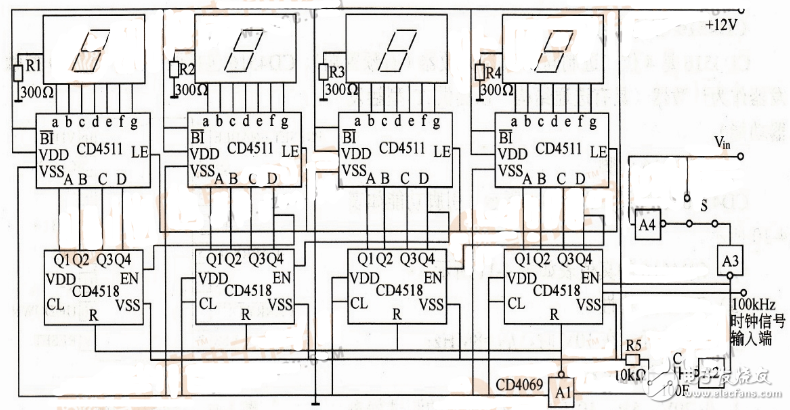

74HC138組成32線譯碼器的電路圖

結語

關于74HC138組成32線譯碼器的方法就介紹到了,希望本文能夠對你有所幫助,如有不足之處歡迎指正。

電子發燒友App

電子發燒友App

評論