基于DSP+FPGA的實(shí)時(shí)視頻采集系統(tǒng)設(shè)計(jì)

0 引言

圖像是自然生物或人造物理的觀測(cè)系統(tǒng)對(duì)世界的記錄,是以物理為載體,以介質(zhì)來(lái)

2010-01-11 10:15:46 535

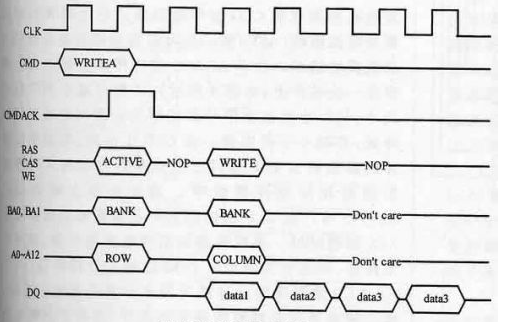

535 本文介紹了一種基于FPGA的用于高分辨率視頻圖像處理的SDRAM控制器的設(shè)計(jì)方法。通過(guò)設(shè)置SDRAM的工作狀態(tài),使其工作在猝發(fā)模式。在視頻時(shí)序信號(hào)控制下,用多行連續(xù)的SDRAM存儲(chǔ)空間,存取視頻

2014-02-10 14:10:21 3023

3023

在高速實(shí)時(shí)或者非實(shí)時(shí)信號(hào)處理系統(tǒng)當(dāng)中,使用大容量存儲(chǔ)器實(shí)現(xiàn)數(shù)據(jù)緩存是一個(gè)必不可少的環(huán)節(jié),也是系統(tǒng)實(shí)現(xiàn)中的重點(diǎn)和難點(diǎn)之一。SDRAM(同步動(dòng)態(tài)隨機(jī)訪問(wèn)存儲(chǔ)器)具有價(jià)格低廉、密度高、數(shù)據(jù)讀寫(xiě)速度快的優(yōu)點(diǎn)

2018-01-18 07:21:00 7964

7964

設(shè)計(jì)了一種基于FPGA的實(shí)時(shí)視頻圖像采集處理電路系統(tǒng)。采用FPGA作為整個(gè)系統(tǒng)的控制和圖像數(shù)據(jù)處理中心。DDR2 SDRAM為高速儲(chǔ)存模塊核心器件,CMOS 7670為視頻圖像采集器件。

2018-02-10 02:43:55 19311

19311

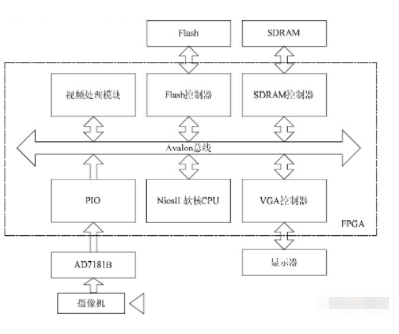

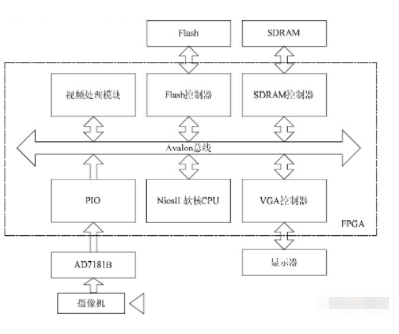

本文中設(shè)計(jì)的視頻監(jiān)控系統(tǒng)的基本構(gòu)成是現(xiàn)場(chǎng)實(shí)時(shí)采集圖像的攝像機(jī)、視頻解碼芯片AD7181B、視頻D/A 芯片ADC7123、VGA 控制器、Flash、SDRAM 控制器及控制核心NiosIICPU

2020-12-30 09:48:37 780

780

SDRAM控制器用戶(hù)手冊(cè)主要內(nèi)容包括功能特點(diǎn)、整體框圖、工作原理、信號(hào)定義、參數(shù)介紹、GUI 調(diào)用、接口時(shí)序等。主要用于幫助用戶(hù)快速了解高云半導(dǎo)體 SDRAM 控制器的產(chǎn)品特性、特點(diǎn)及使用方法。

2022-10-08 07:48:27

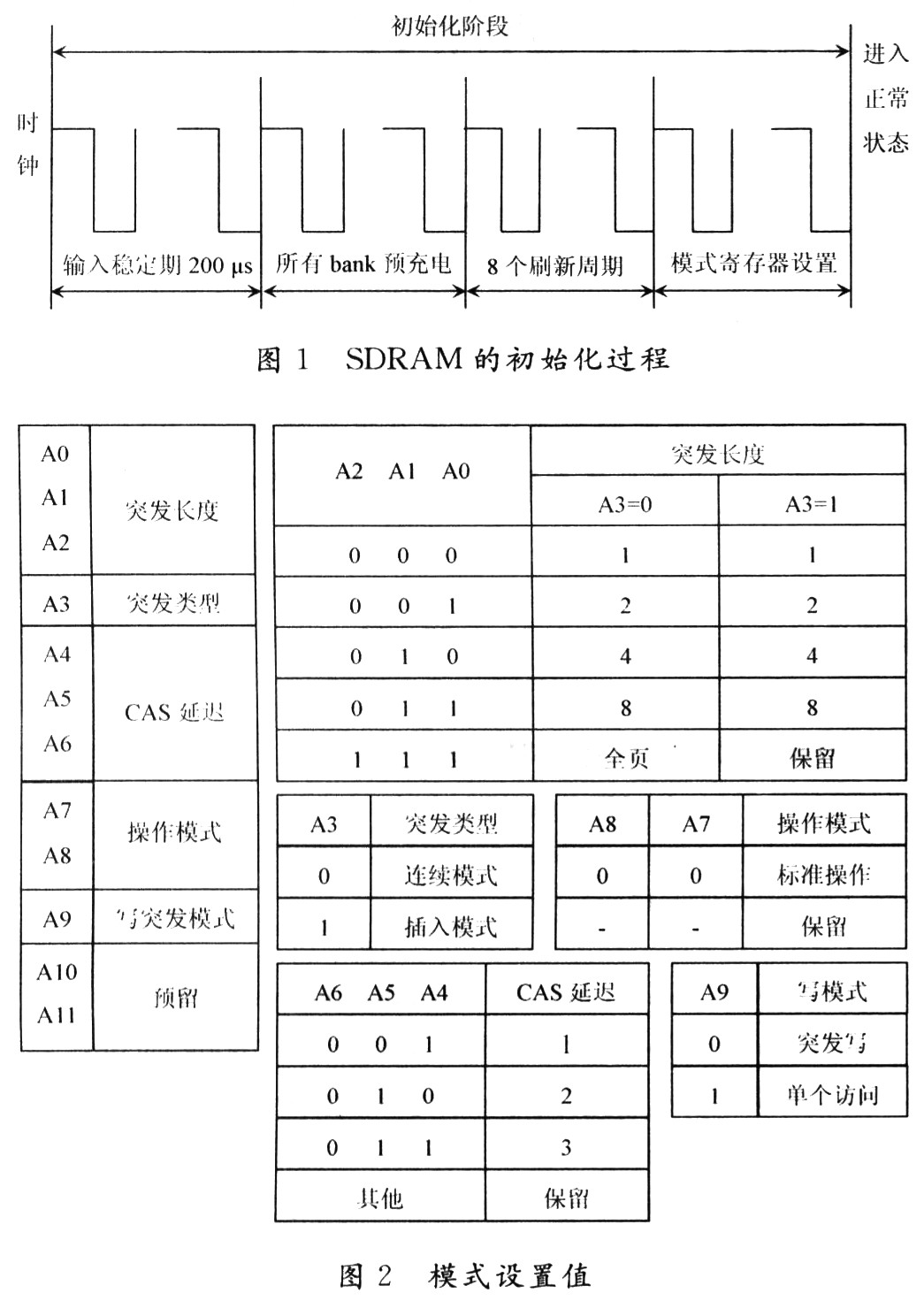

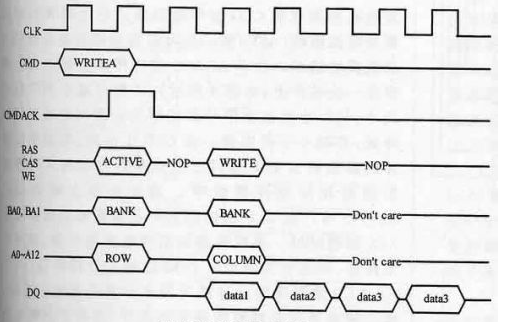

SDRAM的介紹及設(shè)計(jì)應(yīng)用在信息處理中,特別是實(shí)時(shí)視頻圖像處理中,通常都要對(duì)實(shí)現(xiàn)視頻圖像進(jìn)行處理,而這首先必須設(shè)計(jì)大容量的存儲(chǔ)器,同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器SDRAM雖然有價(jià)格低廉、容量大等優(yōu)點(diǎn),但因

2009-11-13 11:37:08

SDRAM的基本工作原理是什么SDRAM的基本讀寫(xiě)操作步驟是什么一種簡(jiǎn)單的通用SDRAM控制器的實(shí)現(xiàn)

2021-05-10 06:26:44

PrimeCell SDRAM控制器是一款符合高級(jí)微控制器總線架構(gòu)(AMBA)的片上系統(tǒng)(SoC)外圍設(shè)備,由ARM開(kāi)發(fā)、測(cè)試和許可。

PrimeCell SDRAM控制器將SDRAM連接到嵌入式SoC ASIC和ASSP。

2023-08-02 18:13:06

積、支持多種嵌入式操作系統(tǒng)(如WinCE、Linux)、集成多種外設(shè)(如I2C控制器、LCD控制器等)等優(yōu)點(diǎn),廣泛應(yīng)用于手持設(shè)備等。WinCE操作系統(tǒng)具有內(nèi)核可剪裁、實(shí)時(shí)性好、支持多種通信、模塊化

2019-08-06 08:30:15

DDR_SDRAM控制器的VHDL代碼已經(jīng)測(cè)試

2016-08-24 16:49:35

TMS320VC5509 為核心的數(shù)據(jù)采集處理系統(tǒng),通過(guò)對(duì)FIFO、SDRAM 和TMS320VC5509 DMA 控制器的介紹,分別給出了具體的接口電路硬件設(shè)計(jì)和實(shí)際軟件的代碼示例。關(guān) 鍵 詞

2009-04-28 10:47:02

本次發(fā)布三例 SDRAM 控制器參考設(shè)計(jì)及 IP Core Generator 支持調(diào)用SDRAM 控制器 IP。 1. 32-bit SDRAM Controller for device

2022-10-08 07:59:17

應(yīng)用PXI做實(shí)時(shí)系統(tǒng)(8196控制器)時(shí)的問(wèn)題。 問(wèn)題:應(yīng)用PXI做實(shí)時(shí)系統(tǒng)(8196控制器),在MAX中傳完軟件后,下位機(jī)上顯示transferring control

2009-05-26 09:13:04

`申請(qǐng)理由:視頻采集前端控制器,負(fù)責(zé)采集視頻信息并保存本地,聯(lián)網(wǎng)后,將本地保存信息上傳管理中心。公司之前采用工控機(jī)方案,成本較高,申請(qǐng)?jiān)摦a(chǎn)品,擬評(píng)估新方案可行性。項(xiàng)目描述:我公司主要面向公安交管做

2016-05-05 10:39:53

在這一講中,Kevin先帶著大家了解一下我們這一套視頻教程《SDRAM那些事兒第一季—輕松設(shè)計(jì)SDRAM控制器》中所要講的這個(gè)項(xiàng)目。這個(gè)項(xiàng)目總的來(lái)講,就是設(shè)計(jì)一個(gè)簡(jiǎn)單的SDRAM控制器,PC機(jī)通過(guò)

2017-05-08 22:14:21

,我們就來(lái)完成讀模塊,然后對(duì)這個(gè)SDRAM控制器稍加完善就可以應(yīng)用到項(xiàng)目中了。對(duì)于讀模塊的設(shè)計(jì):與寫(xiě)模塊一致,只需要將寫(xiě)模塊復(fù)制一份稍加修改就可以了。在此不做贅述!!!如有疑問(wèn),請(qǐng)觀看配套視頻教程進(jìn)行

2017-05-08 22:28:13

到第七講,我們就已經(jīng)把SDRAM控制器的部分全部都完成了。雖然SDRAM控制器的部分完成好了,但是咱們的項(xiàng)目還沒(méi)完,我們還需要將串口部分和控制器部分聯(lián)合起來(lái),形成一個(gè)可以通過(guò)串口發(fā)送命令控制

2017-05-08 22:31:58

第五講介紹完仲裁機(jī)制之后,相信很多朋友都在想,仲裁模塊寫(xiě)好了,那寫(xiě)模塊、讀模塊等與SDRAM相關(guān)操作的模塊應(yīng)該怎么寫(xiě)代碼呢?是的,在學(xué)習(xí)完仲裁機(jī)制之后只是相當(dāng)于給SDRAM控制器建立了一個(gè)框架,這個(gè)

2017-05-08 22:25:30

的SDRAM控制器哦!!!!自己也是一時(shí)興起,看到很多技術(shù)類(lèi)的微信公眾號(hào),所以自己也開(kāi)通了微信公眾號(hào)【開(kāi)源騷客】(微信號(hào):OpenSoc)微信公眾號(hào),主要是用來(lái)分享一些不適合博文寫(xiě)出來(lái)的東西,博文可能大家

2017-05-08 22:20:54

視頻(串口控制SDRAM的讀寫(xiě))。隨后,將給大家介紹該項(xiàng)目中各個(gè)模塊的功能劃分。讓大家也可以輕松設(shè)計(jì)出一款完全為自己定制的SDRAM控制器。項(xiàng)目演示視頻這個(gè)項(xiàng)目總的來(lái)講,就是設(shè)計(jì)一個(gè)簡(jiǎn)單的SDRAM

2016-10-16 23:04:43

使用Verilog實(shí)現(xiàn)基于FPGA的SDRAM控制器

2012-08-20 19:35:27

摘要:本文基于atmega16微處理器和AVRX嵌入式實(shí)時(shí)操作系統(tǒng)設(shè)計(jì)并完成了水秋千的嵌入式控制器.為實(shí)現(xiàn)高級(jí)控制策略和非線性控制理論研究提供了一個(gè)能夠運(yùn)行多任務(wù)的實(shí)驗(yàn)平臺(tái)/通過(guò)移植和裁剪,嵌入式

2009-04-27 21:41:48

的模擬視頻信號(hào)包括圖像信號(hào)、行與場(chǎng)消隱信號(hào)、行與場(chǎng)同步信號(hào)等七種信號(hào)。傳統(tǒng)的視頻采集系統(tǒng)由A/D轉(zhuǎn)換電路、控制邏輯電路、數(shù)據(jù)緩存電路、地址發(fā)生器、地址譯碼電路等構(gòu)成,此類(lèi)設(shè)計(jì)有電路復(fù)雜、芯片繁多、開(kāi)發(fā)

2008-08-29 10:34:55

的應(yīng)用價(jià)值。 4.2.系統(tǒng)的時(shí)序設(shè)計(jì)。 CMOS圖像傳感器結(jié)構(gòu)簡(jiǎn)單,內(nèi)部集成度高,因此僅需很少的外部控制信號(hào)即可完成視頻圖像的采集輸出 本系統(tǒng)時(shí)序采用VHDL硬件描述語(yǔ)言設(shè)計(jì),其核心部分為一個(gè)

2018-11-01 17:23:19

基于FPGA和視頻解碼芯片的實(shí)時(shí)圖像采集系統(tǒng)設(shè)計(jì)

2017-12-26 16:51:49

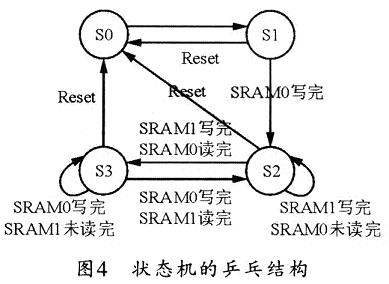

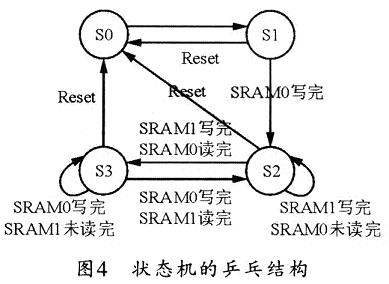

基于FPGA和視頻解碼芯片的實(shí)時(shí)圖像采集系統(tǒng)設(shè)計(jì),介紹了CCD圖像傳感器和ADV7181B解碼芯片的I2C配置原理。給出了乒乓緩存的原理與實(shí)現(xiàn)方法,同時(shí)給出了ADV7181B與FPGA等芯片組成視頻處理電路的設(shè)計(jì)和FPGA的程序?qū)崿F(xiàn)方法。

2017-11-17 13:59:48

。DDR的時(shí)序與SDRAM是相似的,學(xué)好SDRAM后,理解DDR2和DDR3就非常容易了。2、至簡(jiǎn)設(shè)計(jì)代碼實(shí)現(xiàn)(附錄部分代碼)下面是使用至簡(jiǎn)設(shè)計(jì)法實(shí)現(xiàn)的SDRAM控制器,該控制器使用了四段式狀態(tài)機(jī),其他信號(hào)

2017-08-02 17:43:35

本文針對(duì)自行研制的基于TMS320DM642(以下簡(jiǎn)稱(chēng)DM642)DSP的視頻處理板卡,使其在C64x系列DSP的實(shí)時(shí)操作系統(tǒng)DSP/BIOS的環(huán)境下運(yùn)行,實(shí)現(xiàn)基于類(lèi)/微驅(qū)動(dòng)模型的視頻采集驅(qū)動(dòng)程序,并進(jìn)一步描述采用EDMA(增強(qiáng)的直接存儲(chǔ)器存取控制器)的數(shù)字視頻圖像信號(hào)的實(shí)時(shí)傳輸。

2021-06-08 07:05:13

本文提出了一種基于FPGA的SDRAM控制器的設(shè)計(jì)方法,并用Verilog給于實(shí)現(xiàn),仿真結(jié)果表明通過(guò)該方法設(shè)計(jì)實(shí)現(xiàn)的控制器可以在FPGA芯片內(nèi)組成如圖1所示的SDRAM接口,從而使得系統(tǒng)用戶(hù)對(duì)SDRAM的操作非常方便。

2021-04-15 06:46:56

基于FPGA的SDRAM控制器包括哪些部分呢?如何去實(shí)現(xiàn)一種基于FPGA的SDRAM控制器設(shè)計(jì)呢?

2021-11-04 06:47:44

SDRAM控制器基本操作原理是什么?如何去設(shè)計(jì)并實(shí)現(xiàn)一種SDRAM控制器?

2021-06-07 06:01:39

如何解決SDRAM控制器設(shè)計(jì)刷新的問(wèn)題?

2021-11-04 07:20:02

本文針對(duì)自行研制的基于TMS320DM642(以下簡(jiǎn)稱(chēng)DM642)DSP的視頻處理板卡,使其在C64x系列DSP的實(shí)時(shí)操作系統(tǒng)DSP/BIOS的環(huán)境下運(yùn)行,實(shí)現(xiàn)基于類(lèi)/微驅(qū)動(dòng)模型的視頻采集驅(qū)動(dòng)程序,并進(jìn)一步描述采用EDMA(增強(qiáng)的直接存儲(chǔ)器存取控制器)的數(shù)字視頻圖像信號(hào)的實(shí)時(shí)傳輸。

2021-06-08 06:07:33

本文針對(duì)自行研制的基于TMS320DM642(以下簡(jiǎn)稱(chēng)DM642)DSP的視頻處理板卡,使其在C64x系列DSP的實(shí)時(shí)操作系統(tǒng)DSP/BIOS的環(huán)境下運(yùn)行,實(shí)現(xiàn)基于類(lèi)/微驅(qū)動(dòng)模型的視頻采集驅(qū)動(dòng)程序,并進(jìn)一步描述采用EDMA(增強(qiáng)的直接存儲(chǔ)器存取控制器)的數(shù)字視頻圖像信號(hào)的實(shí)時(shí)傳輸。

2021-06-08 06:03:19

,這種靜態(tài)的圖像已無(wú)法滿(mǎn)足人們對(duì)視頻信息的要求。隨著人們對(duì)視頻數(shù)據(jù)的要求越來(lái)越高,高清晰、實(shí)時(shí)性視頻數(shù)據(jù)量越來(lái)越大,視頻的實(shí)時(shí)處理難度也在逐漸增大。

2019-08-12 08:16:32

國(guó)內(nèi)普遍采用TM320系列的DSP器件作為永磁同步電機(jī)控制系統(tǒng)的主控制器,因CPU負(fù)載過(guò)重導(dǎo)致系統(tǒng)實(shí)時(shí)性降低的問(wèn)題日益顯著。采用具有并行工作特性的FPGA器件作為主控制器能夠提高系統(tǒng)實(shí)時(shí)性。因此,我們具體該怎么設(shè)計(jì)呢?

2019-08-14 08:02:56

我移植網(wǎng)上的一個(gè)sdram vga的代碼到ep4ce6e22c8n開(kāi)發(fā)板上,它里面的sdram控制器是tequan寫(xiě)的,但是我移植后,卻得不到代碼要的效果,sdram讀寫(xiě)出來(lái)的數(shù)據(jù)有錯(cuò),調(diào)了好久也

2014-04-03 16:23:55

DDR SDRAM在嵌入式系統(tǒng)中有哪些應(yīng)用?DDR SDRAM的工作方式有哪幾種?怎樣去設(shè)計(jì)DDR SDRAM控制器?

2021-04-30 07:04:04

本文設(shè)計(jì)了一種基于DSP+FPGA的實(shí)時(shí)視頻采集系統(tǒng)。

2021-06-07 06:39:43

SDRAM控制器的主要特點(diǎn)是什么?SDRAM控制器的狀態(tài)流程是怎樣的?SDRAM控制器有哪些功能?

2021-06-26 07:35:01

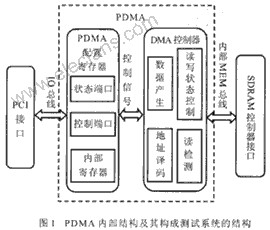

用什么方法去測(cè)試SDRAM控制器的性能?PDMA的結(jié)構(gòu)及工作原理是什么?RTL仿真的順序是什么?

2021-04-08 06:19:50

本帖最后由 upmcu 于 2012-7-28 15:07 編輯

截圖:LED顯示控制系統(tǒng)中SDRAM控制器的設(shè)計(jì).pdf基于FPGA的DDR2+SDRAM數(shù)據(jù)存儲(chǔ)研究.pdf基于FPGA

2012-07-28 14:40:53

轉(zhuǎn)載▼網(wǎng)上有很多的SDR SDRAM控制器的代碼,但都是基于burst1/2/4/8模式下的,這種模式下傳輸高速的相機(jī)數(shù)據(jù)還是有點(diǎn)拮據(jù)的,所以花了幾天把這些模式改造成了頁(yè)突發(fā)模式。我的這個(gè)控制器模型

2014-09-03 00:08:33

SDRAM(同步動(dòng)態(tài)存儲(chǔ)器)是一種應(yīng)用廣泛的存儲(chǔ)器,具有容量大、數(shù)據(jù)讀寫(xiě)速度快、價(jià)格低廉等優(yōu)點(diǎn),特別適合那些需要海量存儲(chǔ)器的應(yīng)用領(lǐng)域,例如視頻方面。那么有誰(shuí)知道,高速SDRAM控制器的視頻有哪些嗎?

2019-08-09 06:23:43

傳統(tǒng)的實(shí)時(shí)網(wǎng)絡(luò)監(jiān)控系統(tǒng)是通過(guò)視頻采集卡在PC 機(jī)上構(gòu)建網(wǎng)絡(luò)視頻。提出了網(wǎng)絡(luò)數(shù)字視頻監(jiān)控系統(tǒng), 其系統(tǒng)硬件以ARM9 處理器S3C2410 為核心, 包含F(xiàn)lash、SDRAM、USB 攝像頭、網(wǎng)絡(luò)控制器

2009-04-21 23:39:04 57

57 提出了一種在HDTV SOC 系統(tǒng)中實(shí)現(xiàn)多模塊共享存儲(chǔ)單元的高效SDRAM 控制器。通過(guò)利用合理的請(qǐng)求仲裁、Full Page 讀寫(xiě)、指令與數(shù)據(jù)分離、指令緩存和前后相關(guān)處理等機(jī)制,實(shí)現(xiàn)了高吞吐

2009-08-14 16:09:14 13

13 簡(jiǎn)要介紹了SDRAM工作原理并認(rèn)真研究了Altera提供的SDRAM控制器,根據(jù)實(shí)際系統(tǒng)使用需要加以修改簡(jiǎn)化,設(shè)計(jì)了對(duì)修改后控制器進(jìn)行操作的狀態(tài)機(jī)。采用全頁(yè)突發(fā)讀寫(xiě)模式,每次讀/寫(xiě)

2009-12-26 17:02:56 70

70 基于RTP的實(shí)時(shí)視頻傳輸系統(tǒng):實(shí)時(shí)視頻流技術(shù)在可視電話(huà)、遠(yuǎn)程教育、視頻點(diǎn)播等方面得到廣泛應(yīng)用。網(wǎng)絡(luò)實(shí)時(shí)視頻系統(tǒng)一般分為4 大模塊:采集子系統(tǒng)、編碼壓縮子系統(tǒng)、傳輸控制

2009-12-29 23:56:19 56

56 DDR2 SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設(shè)計(jì)方法!詳述了其基本結(jié)構(gòu)和設(shè)計(jì)思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 本文采用Altera 公司的Stratix 系列FPGA 實(shí)現(xiàn)了一個(gè)三端口非透明型SDRAM 控制器,該控制器面向用戶(hù)具有多個(gè)端口,通過(guò)輪換優(yōu)先級(jí)的設(shè)計(jì)保證了多個(gè)端口平均分配SDRAM的帶寬且不會(huì)降

2010-03-03 14:37:14 11

11 簡(jiǎn)要介紹了SDRAM工作原理并認(rèn)真研究了Altera提供的SDRAM控制器,根據(jù)實(shí)際系統(tǒng)使用需要加以修改簡(jiǎn)化,設(shè)計(jì)了對(duì)修改后控制器進(jìn)行操作的狀態(tài)機(jī)。采用全頁(yè)突發(fā)讀寫(xiě)模式,每次讀/寫(xiě)后自動(dòng)

2010-07-21 17:31:37 38

38 本文介紹了DDR3 SDRAM 的基本特點(diǎn)和主要操作時(shí)序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設(shè)計(jì)方法。詳述了控制器基本結(jié)構(gòu)和設(shè)計(jì)思想,分析了各模塊功能與設(shè)計(jì)注意事項(xiàng),并

2010-07-30 17:13:55 30

30 摘要: 介紹了SDRAM的存儲(chǔ)體結(jié)構(gòu)、主要控制時(shí)序和基本操作命令,并且結(jié)合實(shí)際系統(tǒng),給出了一種用FPGA實(shí)現(xiàn)的通用SDRAM控制器的方案。

關(guān)鍵詞:

2009-06-20 12:51:58 834

834

摘 要:介紹了SDRAM的特點(diǎn)和工作原理,提出了一種基于FPGA的SDRAM控制器的設(shè)計(jì)方法,使用該方法實(shí)現(xiàn)的控制器可非常方便地對(duì)SDRAM進(jìn)行控制。

關(guān)鍵

2009-06-20 13:04:51 2075

2075 基于FPGA的高速SDRAM控制器的視頻應(yīng)用

0 引言 SDRAM(同步動(dòng)態(tài)存儲(chǔ)器)是一種應(yīng)用廣泛的存儲(chǔ)器,具有容量大、數(shù)據(jù)讀寫(xiě)速度快、價(jià)格低廉等優(yōu)點(diǎn),特別適

2009-11-04 09:56:20 847

847 基于DSP+FPGA的實(shí)時(shí)視頻采集系統(tǒng)設(shè)計(jì)

0 引言

圖像是自然生物或人造物理的觀測(cè)系統(tǒng)對(duì)世界的記錄,是以物理為載體,以介質(zhì)來(lái)記錄信息的

2009-12-16 10:20:55 576

576

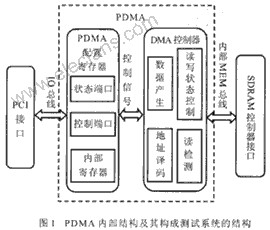

我們?cè)O(shè)計(jì)了一個(gè)PDMA(Programmable Direct Mem o ry Access)用于測(cè)試SDRAM控制器的性能。在SoC中,SDRAM控制器往往跟多個(gè)IP模塊(圖形處理單元,音頻處理單元等)交換數(shù)據(jù),采用多個(gè)PDMA通道

2010-07-02 18:31:41 1655

1655

本方案設(shè)計(jì)的是基于IP網(wǎng)絡(luò)的實(shí)時(shí)視頻采集、處理及傳輸系統(tǒng)。整個(gè)系統(tǒng)在嵌入式軟硬件構(gòu)架上實(shí)現(xiàn),無(wú)需其它設(shè)備協(xié)助就能獨(dú)立完成通用目的視頻應(yīng)用,比如視頻監(jiān)控和網(wǎng)絡(luò)視頻會(huì)議。

2011-08-19 15:13:06 2400

2400 SDRAM存儲(chǔ)芯片擁有快速讀寫(xiě)的性能,可以應(yīng)用以回波模擬系統(tǒng)作為數(shù)據(jù)高速緩存器。SDRAM芯片是由SDRAM控制器控制的, SDRAM控制器有嚴(yán)格的控制時(shí)序和工作狀態(tài),可以使用有限狀態(tài)機(jī)理論

2011-10-24 15:08:05 0

0 通過(guò)設(shè)計(jì)基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等單片機(jī)和DSP等微處理器的外部連接SDRAM,增加系統(tǒng)的存儲(chǔ)空間。

2012-02-16 17:06:47 45

45 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設(shè)計(jì)VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 38

38 高速圖像存儲(chǔ)系統(tǒng)中SDRAM控制器的實(shí)現(xiàn)

2016-08-29 15:02:03 10

10 基于VHDL的SDRAM控制器的實(shí)現(xiàn)

2017-01-22 13:43:27 12

12 DDR2SDRAM控制器在機(jī)載顯控系統(tǒng)中的應(yīng)用_孫少偉

2017-03-19 11:26:54 1

1 EPM1240的SDRAM控制器的設(shè)計(jì)

2017-10-31 08:24:31 21

21 的像素大小。在存儲(chǔ)模塊中,SDRAM的工作時(shí)鐘和視頻采集系統(tǒng)的時(shí)鐘不同,為解決讀寫(xiě)時(shí)鐘不同步的問(wèn)題,采用異步FIFO實(shí)現(xiàn)跨時(shí)鐘域的同步化,同時(shí)采用了兩片SDRAM實(shí)現(xiàn)乒乓緩存設(shè)計(jì),對(duì)SDRAM控制器各個(gè)模塊分別進(jìn)行Modelsim仿真驗(yàn)證,得出正確結(jié)果,可以滿(mǎn)足系統(tǒng)的整體要求。

2017-11-17 01:28:55 3704

3704

控制器用戶(hù)接口設(shè)計(jì)方案。該控制器用戶(hù)接口已經(jīng)在Xilinx 公司的VC707 開(kāi)發(fā)板上通過(guò)了功能驗(yàn)證,并成功的被應(yīng)用到高速圖像數(shù)據(jù)采集系統(tǒng)中。

2017-11-17 14:14:02 3290

3290

在很多通信芯片及系統(tǒng)的開(kāi)發(fā)中,常常需要用到存儲(chǔ)容量大、讀寫(xiě)速度快的存儲(chǔ)器。在各種隨機(jī)存儲(chǔ)器件中,SDRAM的價(jià)格低、體積小、速度快、容量大,是比較理想的器件。但是,與SRAM相比較,SDRAM的控制

2017-11-28 19:51:26 5

5 隨著大規(guī)模集成電路和高速、低功耗、高密度存儲(chǔ)技術(shù)的發(fā)展,SDRAM動(dòng)態(tài)存儲(chǔ)器因容量大、速度快、價(jià)格低廉等優(yōu)點(diǎn),現(xiàn)已成為PC內(nèi)存的主流。然而SDRAM存儲(chǔ)器內(nèi)部控制邏輯十分復(fù)雜,時(shí)序要求也非常嚴(yán)格,因此需要設(shè)計(jì)專(zhuān)門(mén)的SDRAM控制器來(lái)實(shí)現(xiàn)系統(tǒng)對(duì)SDRAM的訪問(wèn)。

2018-04-30 10:58:00 5070

5070

實(shí)現(xiàn)數(shù)據(jù)的高速大容量存儲(chǔ)是數(shù)據(jù)采集系統(tǒng)中的一項(xiàng)關(guān)鍵技術(shù)。本設(shè)計(jì)采用Altera 公司Cyclone系列的FPGA 完成了對(duì)DDR SDRAM 的控制,以狀態(tài)機(jī)來(lái)描述對(duì)DDR SDRAM 的各種時(shí)序

2019-08-14 08:00:00 3401

3401

設(shè)計(jì)了一種基于FPGA的視頻實(shí)時(shí)采集系統(tǒng), 視頻數(shù)據(jù)通過(guò)視頻解碼器、雙口RAM、內(nèi)存控制器, 然后存入片外SDRAM中。根據(jù)視頻處理算法的要求和SDRAM的特點(diǎn), 對(duì)視頻數(shù)據(jù)的存儲(chǔ)格式及讀寫(xiě)時(shí)序進(jìn)行了優(yōu)化, 提高了系統(tǒng)的數(shù)據(jù)傳輸速率, 能夠滿(mǎn)足后續(xù)視頻處理系統(tǒng)的需要。

2018-10-18 17:25:35 7

7 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA讀寫(xiě)SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文主要包括了:FPGA讀寫(xiě)SDRAM的實(shí)例,SDRAM控制器核心介紹,系列SDRAM數(shù)據(jù)手冊(cè)

2018-12-25 08:00:00 56

56 數(shù)據(jù)流數(shù)據(jù)量大、實(shí)時(shí)性要求高的特點(diǎn),采用流模式傳輸,將視頻采集數(shù)據(jù)通過(guò)DMA從存儲(chǔ)資源緊張的片內(nèi)緩存區(qū)搬運(yùn)至片外sDRAM幀緩沖區(qū),實(shí)現(xiàn)圖像的高速傳輸。 利用SoPC(System on Programmable Chip)片上可編程系統(tǒng)技術(shù),將處理器、多口SDRAM控制器、D

2019-02-02 22:35:01 193

193 關(guān)鍵詞:SDRAM , 嵌入式 , 時(shí)序控制 , 視頻系統(tǒng) 在高速數(shù)字視頻系統(tǒng)應(yīng)用中,使用大容量存儲(chǔ)器實(shí)現(xiàn)數(shù)據(jù)緩存是一個(gè)必不可少的環(huán)節(jié)。SDRAM就是經(jīng)常用到的一種存儲(chǔ)器。 但是,在主芯片

2019-02-10 00:12:01 220

220 。本文針對(duì)視頻數(shù)據(jù)流數(shù)據(jù)量大、實(shí)時(shí)性要求高的特點(diǎn),采用流模式傳輸,將視頻采集數(shù)據(jù)通過(guò)DMA從存儲(chǔ)資源緊張的片內(nèi)緩存區(qū)搬運(yùn)至片外SDRAM幀緩沖區(qū),實(shí)現(xiàn)圖像的高速傳輸。 利用SoPC(System on Programmable Chip)片上可編程系統(tǒng)技術(shù),將處理器、多口SDRAM控制器、

2019-03-02 07:58:02 696

696

接口,在響應(yīng)控制輸入前會(huì)等待一個(gè)時(shí)鐘信號(hào),這樣就能和計(jì)算機(jī)的系統(tǒng)總線同步。時(shí)鐘被用來(lái)驅(qū)動(dòng)一個(gè)有限狀態(tài)機(jī),對(duì)進(jìn)入的指令進(jìn)行管線(Pipeline)操作。接下來(lái)由專(zhuān)注于代理銷(xiāo)售SDRAM、SRAM

2020-07-24 14:25:27 719

719 針對(duì)SDRAM 操作繁瑣的問(wèn)題,在對(duì)SDRAM 存儲(chǔ)器和全頁(yè)突發(fā)式操作進(jìn)行研究的基礎(chǔ)上,提出一種簡(jiǎn)易SDRAM 控制器的設(shè)計(jì)方法。該設(shè)計(jì)方法充分利用全頁(yè)式高效率存取的優(yōu)點(diǎn),對(duì)SDRAM 進(jìn)行配置、全頁(yè)突發(fā)式讀寫(xiě)時(shí),操作方便。在實(shí)現(xiàn)sDRAM 的快速批量存儲(chǔ)方面,具有良好的應(yīng)用價(jià)值。

2020-12-18 16:13:18 6

6 的設(shè)計(jì)方法。結(jié)合實(shí)際系統(tǒng),設(shè)計(jì)給出了使用FPGA實(shí)現(xiàn) SDRAM控制器的硬件接口,在 Altera公司的主流FPGA芯片EPlC6Q240C8上,通過(guò)增加流水級(jí)數(shù)和將輸出觸發(fā)器布置在IO單元中,該控制器可達(dá)到185MHz的頻率。

2021-01-26 15:30:52 13

13 1.SDRAM使用越來(lái)越廣泛。

2.SDRAM具有存儲(chǔ)容量大,速率快的特點(diǎn)。

3.SDRAM對(duì)時(shí)序要求嚴(yán)格,需要不斷刷新保持?jǐn)?shù)據(jù)。

.FPGA在電子設(shè)計(jì)中的廣泛應(yīng)用,使用十分靈活利用FPGA來(lái)設(shè)計(jì)自己的 SDRAM控制器。

2021-03-05 14:49:00 10

10 本文首先分析了DDR SDRAM的基本特征,并提出了相應(yīng)的解決方案詳細(xì)介紹了基于J EDEC DDR SDRAM規(guī)范的DDR SDRAM控制器設(shè)計(jì)方案。該控制器采用Verilog HDL硬件描述語(yǔ)言實(shí)現(xiàn),并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 在FPGA視頻圖像處理系統(tǒng)中,經(jīng)常需要使用到SDRAM作為視頻圖像緩存。SDRAM控制器可以分為上電初始化,自動(dòng)刷新,讀操作和寫(xiě)操作這四個(gè)部分,他們之間的轉(zhuǎn)換可以通過(guò)狀態(tài)機(jī)來(lái)控制。下面分別實(shí)現(xiàn)這幾個(gè)部分。

2021-04-19 09:46:24 3459

3459

基于HDMI的全高清實(shí)時(shí)視頻采集與圖像處理系統(tǒng)

2021-06-23 12:00:46 24

24 ,SDRAM的控制邏輯復(fù)雜,使用很不方便。 為了解決這個(gè)矛盾,需要設(shè)計(jì)專(zhuān)用的SDRAM控制器,使系統(tǒng)用戶(hù)象使用SRAM一樣方便的使用SDRAM是十分必要的。考慮到控制器的通用性,本文提出了一種通用的SDRAM控制器的 Verilog設(shè)計(jì),并給出了實(shí)現(xiàn)結(jié)果。 1 SDRAM的工作原理

2021-06-30 09:16:47 2346

2346

實(shí)時(shí)視頻SDRAM控制器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

2022-12-30 09:21:26 3

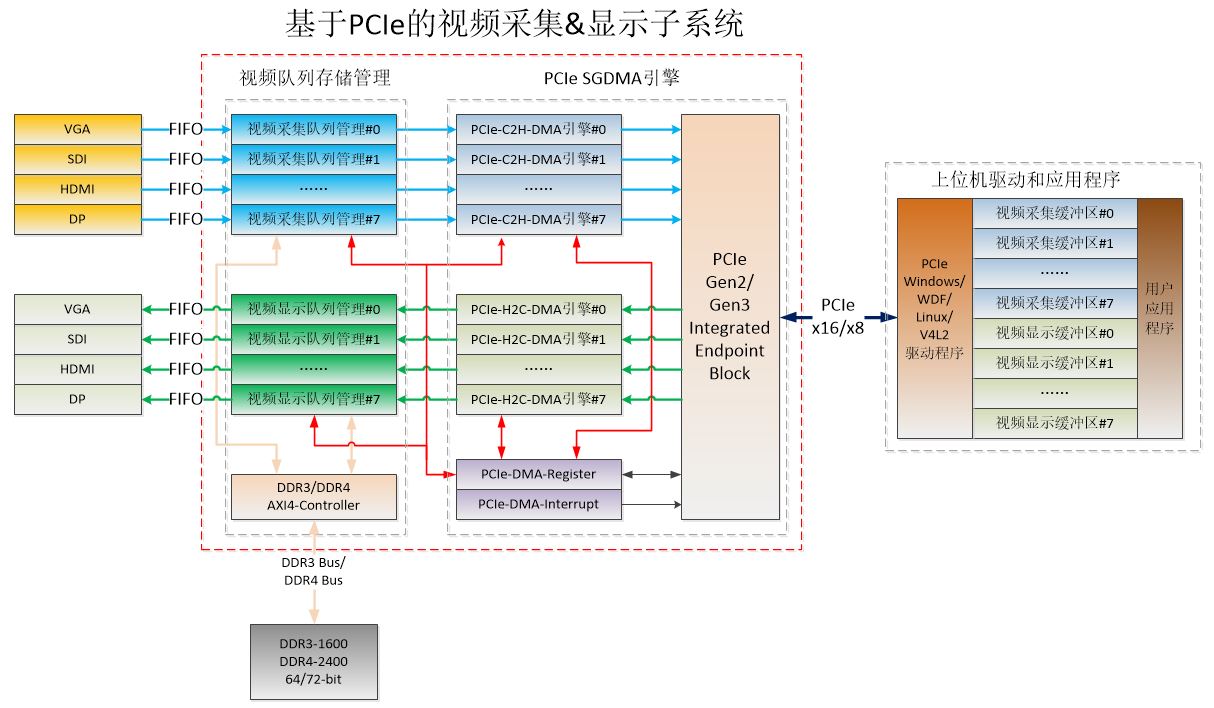

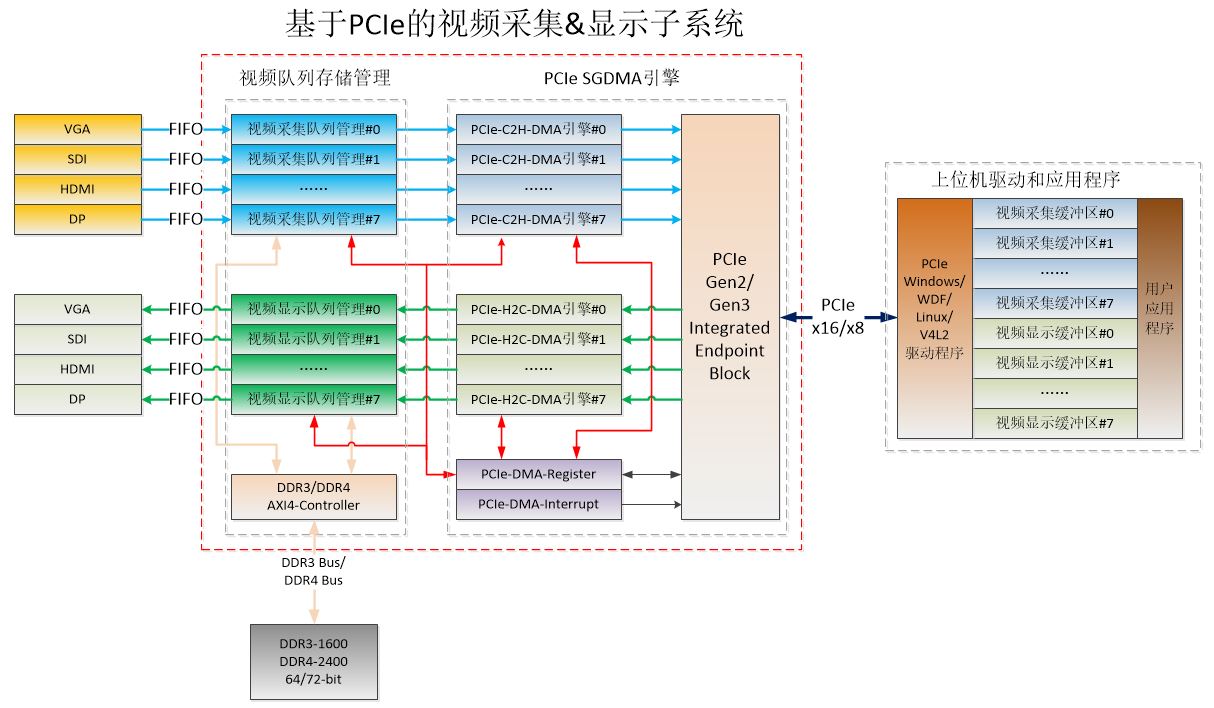

3 視頻采集與顯示子系統(tǒng)可以實(shí)時(shí)采集多路視頻信號(hào),并存儲(chǔ)到視頻采集隊(duì)列中,借助高效的硬實(shí)時(shí)視頻幀出入隊(duì)列管理和PCIe C2H DMA引擎,將采集到的視頻幀實(shí)時(shí)傳遞到上位機(jī)采集緩沖區(qū)。在超帶寬視頻采集

2024-02-22 20:05:39 115

115

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論