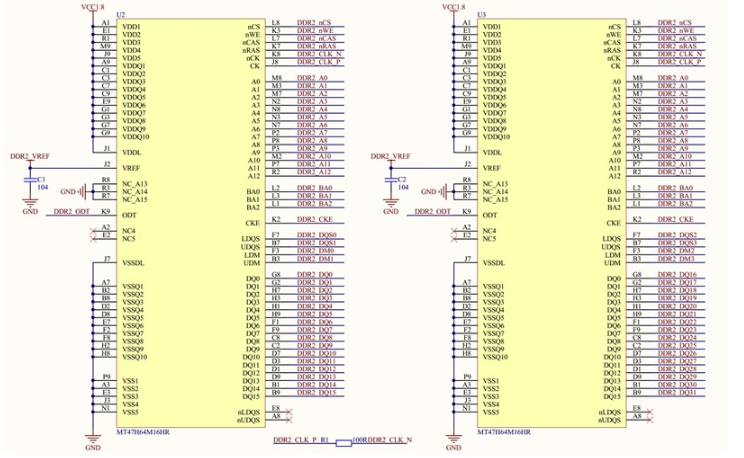

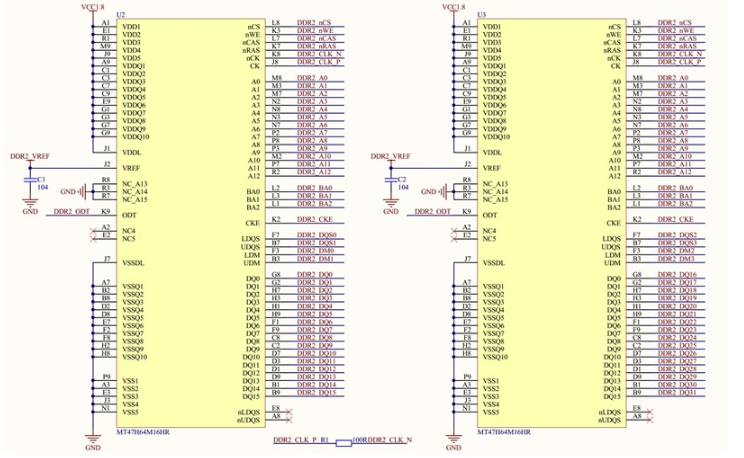

每片DDR2存儲器的容量為1Gb,兩片DDR2芯片組合,得到總?cè)萘繛?Gb。單DDR2存儲器為16bit,兩片存儲器共用控制線和地址線,數(shù)據(jù)線并列,即組成了32位的2Gb存儲模組。

2020-08-21 15:09:00 5493

5493

描述Arduino DUE SODIMM(DDR2 規(guī)格)DDR2 SODIMM 封裝中的 Arduino DUE

2022-09-13 06:46:33

如圖中,ARM的DDR2接口與DDR2數(shù)據(jù)接口為什么不是D0對D0....D15對D14呢?在RK的平板方案中也見過這種接法,想問一下這樣的話處理器是如何傳數(shù)據(jù)的?

2022-04-20 09:34:41

我想用s3c2450外接128MB的DDR2內(nèi)存,就是說用兩片64MB的DDR2拼一下。 請問高手應該怎樣連接? 謝謝

2022-06-22 12:01:49

我在XPS中進行硬件設計時添加了DDR2 ip內(nèi)核,因為代碼很大而導致內(nèi)存錯誤。但在未來的計劃中,我遇到了布局錯誤。我已將ddr2包裝器的ucf文件復制粘貼到system.ucf文件中以消除一些錯誤

2020-06-18 10:36:34

嗨,DDR2內(nèi)存型號的最低頻率是多少?我們可以嘗試低于125 Mhz的DDR2內(nèi)存型號嗎?問候 - sampath

2020-05-27 09:24:15

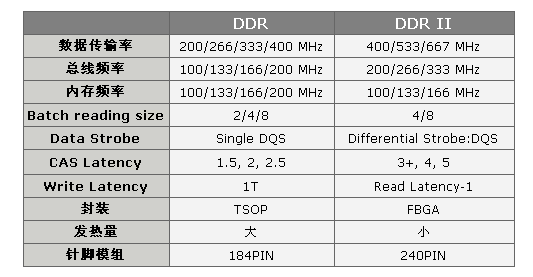

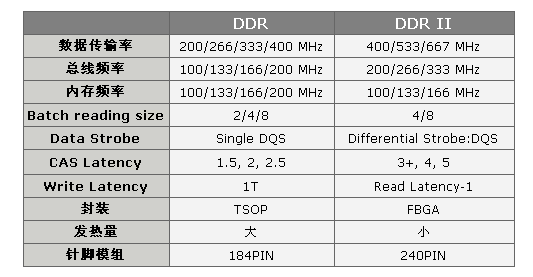

從上表可以看出,在同等核心頻率下,DDR2的實際工作頻率是DDR的兩倍。這得益于DDR2內(nèi)存擁有兩倍于標準DDR內(nèi)存的4BIT預讀取能力。

2019-08-08 07:11:44

1、 在讀數(shù)據(jù)時,打開主控端的ODT,關閉DDR2端的 ODT;而在寫數(shù)據(jù)時,則相反;數(shù)據(jù)線空閑時,則關閉兩端的ODT。2、 對于DDR2 800,設置寄存器,使主控端和DDR2端的ODT阻值為50

2019-05-30 08:10:00

DDR2時鐘線走線規(guī)則a)時鐘線包括MEM_CLKOUT#0、MEM_CLKOUT0、MEM_CLKOUT#1、MEM_CLKOUT1,MEM_CLKOUT#2、MEM_CLKOUT2

2015-02-03 14:13:44

本次設計中CPU的封裝為BGA844-SOC-Y,DDR2的封裝為FBGA84,DDR2的控制總線采用星形連接,使用的PCB軟件為AltiumDesigner10

2019-07-30 06:29:28

DDR2設計原理 DDR2 designBasic knowledge? Source Sync Bus Analysis? On-Die Terminations (ODT)? Slew Rate

2009-11-19 09:59:04

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

求一DDR2接口設計代碼

2013-04-24 10:00:36

[size=14.3999996185303px]我有個ARM的板子,DDR2和NAND的數(shù)據(jù)線是復用的,這樣PCB走線的時候,除了原來DDR2高速信號走線阻抗和等長以外,還需要特別注意什么嗎。NAND的線長是不是不算入DDR2總的線長中。

2016-10-10 17:09:28

本帖最后由 芯航線跑堂 于 2016-12-19 00:25 編輯

AC6102 DDR2測試工程本文檔介紹AC6102上DDR2存儲器基于Verilog代碼的測試過程。AC6102上使用了2

2016-12-15 14:43:40

最近在做ddr2方面的東西,需要仿真ddr2,可是一直沒有頭緒。xx_example_top_tb仿真不知道是對是錯,網(wǎng)上說的外掛美光ddr2 模型的仿真方法,沒有具體講解。哪位大蝦能夠指點一二哇,不甚感激!

2016-06-29 15:50:28

DR2與DDR有哪些區(qū)別?DDR3與DDR2的區(qū)別是什么?

2021-10-26 06:15:07

大家好,我們可以在這里討論使用DDR2 / DDR3內(nèi)存與FIFO(我的好奇心)的差異/優(yōu)點/缺點。以上來自于谷歌翻譯以下為原文Hi All, Can we discuss here

2019-02-14 06:14:38

本次發(fā)布 Gowin DDR2 Memory Interface IP 參考設計及 IP CoreGenerator 支持調(diào)用 Gowin DDR2 Memory Interface IP

2022-10-08 07:25:25

Gowin DDR2 Memory Interface IP用戶指南主要內(nèi)容包括 IP 的結構與功能描述、端口說明、時序說明、配置調(diào)用、參考設計等。主要用于幫助用戶快速了解 Gowin DDR2 Memory Interface IP 的產(chǎn)品特性、特點及使用方法。

2022-10-08 07:08:19

IBIS Models for DDR2 Analysis 仿真

2012-03-16 16:52:07

TI專家、各位朋友:

??????? 目前在用一個OMAPL138的板子,板子是自己設計的,DDR2是ISSI的 IS43DR16640A,大小為64M*16bit,我在GEL中配置的它。測試的時候

2018-06-21 03:36:51

有人用Xilinx ISE的mig生成ddr2,然后進行調(diào)試的嗎?如果選擇了內(nèi)含pll,頂層時鐘怎么連接

2014-09-15 19:14:41

[資訊] DRAM挺過7月 有望旺到后年動態(tài)隨機存取內(nèi)存(DRAM)價格年初以來維持強勢,但封測廠強調(diào),7月爾必達新增產(chǎn)能是否可以去化是重要觀察期,一旦能順利消化,DRAM產(chǎn)業(yè)榮景將能持續(xù)到明、后年

2010-05-10 10:51:03

; is not a bus or arrayError (12014): Net "DDR2:DDR2U|mem_dq[15]", which fans out to "DDR2

2014-03-18 19:55:04

quartus ii 調(diào)用DDR2 IP核時無法生成 ( 已經(jīng)完成破解獲得ddr2的license)

2017-02-07 17:29:25

在DDR2 MIG的使用時,想把DDR2封裝成一個FIFO使用,但是有些問題不是太明白。在MIG的User Interface接口中,提供給控制器的數(shù)據(jù)是上升沿和下降沿的拼接,一個周期提供兩個數(shù)據(jù)到

2015-03-29 18:41:43

1、從工作平率上說:首先接口就全部不同 電壓不同 頻率的計算方法不同 SDR的頻率就是外頻 133=133 DDR的頻率就是外頻的2倍 133=266 DDR2的頻率就是外頻的4倍 133=533

2014-12-30 14:35:58

1、從工作平率上說:首先接口就全部不同 電壓不同 頻率的計算方法不同 SDR的頻率就是外頻 133=133 DDR的頻率就是外頻的2倍 133=266 DDR2的頻率就是外頻的4倍 133=533

2014-12-30 14:36:44

本文和設計代碼由FPGA愛好者小梅哥編寫,未經(jīng)作者許可,本文僅允許網(wǎng)絡論壇復制轉(zhuǎn)載,且轉(zhuǎn)載時請標明原作者。Altera DDR2控制器使用IP的方式實現(xiàn),一般很少自己寫控制器代碼。ddr

2020-02-25 18:33:00

1. 嵌入式的內(nèi)存內(nèi)存的發(fā)展從DRAM到廣泛使用的SDRAM,到之后一代的DDR(或稱DDR1),然后是DDR2和DDR3進入大眾市場,2015年開始DDR4進入消費市場。單片機領域中,使用較多

2021-12-17 07:44:44

Self-Refresh功能),達到省電目的。 3.容量更大:更多的Bank數(shù)量,依照JEDEC標準,DDR2應可出到單位元元4Gb的容量(亦即單條模塊可到8GB),但目前許多DRAM廠商的規(guī)劃,DDR2生產(chǎn)

2011-12-13 11:29:47

與DDR2供給吃緊帶動整體平均售價上揚。而在整體DRAM廠DRAM營收排行中(包含代工),2006年第二季仍以三星(Samsung)居首,市占率高達24.8%,其次為由英飛凌(Infineon)所獨立出來

2008-05-26 14:43:30

最近在設計一個需要連接DDR2 SDRAM的FPGA小系統(tǒng),由于是第一次在使用SDRAM,在硬件連接時就遇到一個很糾結的問題——引腳的連接。看了幾種參考設計,發(fā)現(xiàn)有兩種說法:1、DDR2的數(shù)據(jù)(DQ

2017-09-25 17:51:50

小弟最近使用DDR2的IP核的時候,發(fā)現(xiàn)在新建完成的時候有個警告:ddr2_pht.v exit but should have been created by IPToolbench。正是這個警告

2017-03-09 22:50:15

在與SDRAM相同的總線時鐘頻率下達到更高的數(shù)據(jù)傳輸率。雖然DDR2和DDR一樣,都采用相同采樣方式進行數(shù)據(jù)傳輸,但DDR2擁有兩倍于DDR的預讀取系統(tǒng)命令數(shù)據(jù)的能力。也就是說,在同樣100MHz

2011-05-03 11:31:09

Xilinx公司發(fā)布的SP6,V6系列的FPGA中的DDR2的IP核是一大改變。它由原來的軟核變?yōu)榱擞埠耍伺e讓開發(fā)DDR2變的簡單,因為不需要太多的時序調(diào)試,當然也帶來了麻煩,這是因為當DDR2

2015-03-16 20:21:26

嗨!我正在尋找Spartan-3A / 3ANFPGA入門KitBoard用戶指南(UG334)。具體來說第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因為例如這個內(nèi)存

2019-07-31 06:18:10

GPM模型在DDR2設計中的應用是什么?

2021-05-26 06:11:13

你好我正在使用atlys主板,我必須在spartan-6上實現(xiàn)ddr2(MT47H64M16-25E)接口,...通過使用MIG及其示例設計,在模擬中一切正常....通過注意ddr2接口,例如

2019-10-28 07:46:43

你好 ! 我想設計一個框架,我們想出的設計具有以下特點: 1:DDR3(MT47H64M16HR-3 ofmicron inc。) 2:USB 但我不知道如何設計DDR2原理圖,而且我還沒有找到關于

2019-09-06 07:55:42

我生成了DDR2設計但是當我在硬件上運行它時,led_error輸出總是很高,表明讀回失敗。為了縮小問題范圍,我需要查看接口中的總線傳輸,但是當我嘗試將chipcope信號掛鉤到DDR2總線實現(xiàn)失敗

2019-05-10 14:25:23

,DRAM合約價也在淡季明顯上漲。6月價格預期再調(diào)漲5%據(jù)業(yè)者表示,PC DRAM合約價在第一季大漲36%后,韓系DRAM廠在4月再度全面調(diào)漲第二季合約價,其中,4GB DDR3/DDR4模組合約價大漲

2017-06-13 15:03:01

DDR2控制和FPGA實現(xiàn)

2015-07-21 19:28:14

求四片DDR2的例子,非常感謝

2014-07-14 16:33:45

本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2021-04-20 06:30:52

求指導,ddr2尾地址如何計算?

2012-05-31 22:47:25

DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別文所有權歸作者Aircity所有1什么是DDRDDR是Double Data Rate的縮寫,即“雙比特翻轉(zhuǎn)”。DDR是一種技術,中國大陸工程師

2021-09-14 09:04:30

使用CCS5.4 對EVMDM8168 DDR2 進行測試,測試結果為

第一次測試

Error at 8d033180

FAIL... error code 32... quitting

第二次

2018-06-21 11:49:55

下降的缺陷(甚至于DDR/DDR2又有著不支持單一地址訪問的限制,分別至少2/4個地址同時訪問)。但是,速度是王道,容量也是它的優(yōu)勢,這些特點是其它任何易失存儲器無法媲美的,也是它存在的唯一理由

2014-12-30 15:22:49

我們知道ddr2有速度等級和存儲量大小之分。在用altera FPGA設計的時候調(diào)用IP核到底該怎樣選擇ddr2呢?比如說640*480*8bit@60hz的視頻信號,該選擇什么ddr2呢?怎么計算

2018-01-31 11:00:13

將數(shù)據(jù)發(fā)送,接收再存儲入DDR2,再將數(shù)據(jù)以燈的形式顯示出來,燈型數(shù)據(jù)不對。自己實在找不到錯誤如果不存入DDR2,直接接收數(shù)據(jù)顯示,一切正常,加上DDR2之后,從DDR2讀取就無法正常顯示觀察燈型

2018-08-10 11:24:19

如何操作才能使得ddr2降頻,是更換晶振還是操作寄存器呢?pll2是產(chǎn)生ddr2的clk,但是手冊上說明clk=clkin2*20/2.說明軟件是改不了的嗎?

2018-08-02 09:10:45

FPGA與DDR2存儲器接口DDR2控制器的設計原理是什么?DDR2控制器的應用有哪些?

2021-04-30 06:28:13

發(fā)展而來的,能夠在時鐘的上升沿和下降沿各傳輸一次數(shù)據(jù),可以在與SDRAM相同的總線時鐘頻率下達到更高的數(shù)據(jù)傳輸率。雖然DDR2和DDR一樣,都采用相同采樣方式進行數(shù)據(jù)傳輸,但DDR2擁有兩倍于DDR

2019-05-31 05:00:05

FeaturesThe Agilent W2630 Series DDR2 BGA probes for logic analyzers and oscilloscopes enable

2010-08-01 12:14:42 6

6 DDR2名詞解釋

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技術標準,它與上一代DDR內(nèi)

2009-04-26 18:02:22 1186

1186

DDR2內(nèi)存?zhèn)鬏敇藴?nbsp; DDR2可以看作是DDR技術標準的一種升級和擴展:DDR的核心頻率與時鐘頻率相等,但數(shù)據(jù)頻率為時鐘頻率的兩倍,也

2009-04-26 18:05:40 786

786

什么是DDR2 SDRAM

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技

2009-12-17 11:17:59 623

623 DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技術標準,它與上一代DDR內(nèi)存技術標準最大的不

2009-12-17 16:26:19 731

731 DDR2內(nèi)存?zhèn)鬏敇藴?

DDR2可以看作是DDR技術標準的一種升級和擴展:DDR的核心頻率與時鐘頻率相等,但數(shù)據(jù)頻率為時鐘頻率的兩倍,也就是說在一個時鐘周期內(nèi)必須傳輸

2009-12-24 14:53:28 621

621 DDR2傳輸標準

DDR2可以看作是DDR技術標準的一種升級和擴展:DDR的核心頻率與時鐘頻率相等,但數(shù)據(jù)頻率為時鐘頻率的兩倍,也就是說在一個時鐘周期內(nèi)必須傳輸兩次

2009-12-25 14:12:57 434

434 臺灣DRAM廠商大舉轉(zhuǎn)產(chǎn)DDR3

2010年PC主流內(nèi)存標準從DDR2向DDR3的轉(zhuǎn)換正在逐步成為現(xiàn)實。據(jù)臺灣媒體報道,由于下游廠商的DDR2訂單量近期出現(xiàn)急劇下滑,多家臺系DRAM芯片

2010-01-18 09:25:13 602

602 廠商采取搭售策略 挽回DDR2銷售頹勢

全球DRAM市場正加速進行世代交替,DDR3芯片因缺貨使得價格持續(xù)上漲,DDR2價格卻嚴重下跌,且累積庫存越來越多,近期韓系DRAM大

2010-01-20 09:24:18 668

668 DDR2芯片價格有望在下半年超過DDR3

報道,威剛主席Simon Chen今天表示,隨著DRAM制造商把重點放在DDR3芯片生產(chǎn)上,DDR2芯片的出貨量將開始減少,其價格有望在今年下半

2010-02-05 09:56:18 955

955 DDR2,DDR2是什么意思

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)進行開發(fā)的新生代內(nèi)存技術標準,它與上一代DDR內(nèi)

2010-03-24 16:06:36 1381

1381 金士頓:DDR2/DDR3價格可能會繼續(xù)上漲

據(jù)報道,存儲大廠金士頓亞太地區(qū)副總裁Scott Chen近日表示,雖然1Gb DDR2/DDR3的芯片價格已經(jīng)超過了3美元大關,

2010-04-09 09:11:05 676

676 DDR2內(nèi)存瘋狂演繹 2G版沖破350元近一年間,市場主流的DDR2內(nèi)存一直演繹著瘋狂,在200元與300元之間幾經(jīng)反復。近日,DDR2內(nèi)存的瘋狂更進一步,2G的DDR2內(nèi)存的售價最高竟然已達35

2010-04-13 09:29:35 471

471 SDRAM, DDR, DDR2, DDR3 是RAM 技術發(fā)展的不同階段, 對于嵌入式系統(tǒng)來說, SDRAM 常用在低端, 對速率要求不高的場合, 而在DDR/DDR2/DDR3 中,目前基本上已經(jīng)以DDR2 為主導,相信不久DDR3 將全面取代

2012-01-16 14:53:01 0

0 ISS 的DDR2 的設計指導,雖是英文,但很有用。

2015-10-29 10:53:38 0

0 總結了DDR和DDR2,DDR3三者的區(qū)別,對于初學者有很大的幫助

2015-11-10 17:05:37 36

36 DDR2 SDRAM操作時序規(guī)范,中文版規(guī)范

2015-11-10 17:42:44 0

0 Xilinx FPGA工程例子源碼:DDR2 Controller

2016-06-07 11:44:14 24

24 本文首先列出了DDR2布線中面臨的困難,接著系統(tǒng)的講述了DDR2電路板設計的具體方法,最后給出個人對本次電路設計的一些思考。

2017-09-19 11:27:21 22

22 提出一種便于用戶操作并能快速運用到產(chǎn)品的DDR2控制器IP核的FPGA實現(xiàn),使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過IP核控制DDR2。簡單介紹了DDR2的特點和操作

2017-11-22 07:20:50 4687

4687

DDR2(Double Data Rate2)SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)制定的新生代內(nèi)存技術標準,它與上一代DDR內(nèi)存技術標準最大的不同:雖然采用時鐘的上升/下降沿同時傳輸

2017-11-25 01:41:01 3855

3855

DRAM (動態(tài)隨機訪問存儲器)對設計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統(tǒng)的存儲系統(tǒng)設計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

91644 突發(fā)長度,由于DDR3的預期為8bit,所以突發(fā)傳輸周期(BL,Burst Length)也固定位8,而對于DDR2和早期的DDR架構的系統(tǒng),BL=4也是常用的,DDR3為此增加了

2018-06-21 09:20:54 14616

14616

DDR2 設備概述:DDR2 SDRAM接口是源同步、支持雙速率傳輸。比如DDR SDRAM ,使用SSTL 1.8V/IO電氣標準,該電氣標準具有較低的功耗。與TSOP比起來,DDR2 SDRAM的FBGA封裝尺寸小得多。

2019-06-22 10:05:01 1793

1793

本文檔的主要內(nèi)容詳細介紹的是DDR和DDR2與DDR3的設計資料總結包括了:一、DDR的布線分析與設計,二、DDR電路的信號完整性,三、DDR Layout Guide,四、DDR設計建議,六、DDR design checklist,七、DDR信號完整性

2020-05-29 08:00:00 0

0 DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別作者:AirCity 2019.12.17Aircity007@sina.com 本文所有權歸作者Aircity所有1 什么是DDRDDR

2021-11-10 09:51:03 154

154 5片DDR2設計分享

2022-12-30 09:19:26 4

4

電子發(fā)燒友App

電子發(fā)燒友App

評論