引言

今天的便攜式設備通過持續的活動監測和情境感知來了解周圍環境。為了實現這個功能,設備集成了越來越多的傳感器和外設,由此產生大量數據。這反過來使得集成更強大的CPU變得很有必要,以便執行越來越多的計算。同時,必須縮小設計尺寸,降低成本和功耗,但又不犧牲最終產品不斷提升的功能要求。

傳感器中樞(Sensor hub)的概念被越來越多地采用到當今的SoC設計中,以滿足“始終運行”的傳感器/外設訪問和控制(甚至以高速率)的要求,而且不會增加功耗和設計成本。傳感器中樞可以是小型CPU內核,與傳感器/外設連接,并通過執行后臺操作并僅在需要時“喚醒”主處理器,充當功耗較大的主處理器的卸載引擎的角色。

用于傳感器采集的基于處理器的典型架構

應用在集成多個傳感器的系統中的典型基于微控制器的架構包括以下組件[1]:

a)一個微控制器單元(MCU) - 也稱為處理子系統,MCU控制系統內所有構成部分的運行并處理數據。它包括一個處理器、一個內部或外部存儲器、以及本地數據處理所需的所有外設和子系統。在典型的基于MCU的架構中,控制器執行所有傳感器數據收集、處理和存儲。

b)傳感器元件(或傳感子系統) - 一組傳感器,可以是無源或有源,數字或模擬的任意組合。這些傳感器將來自外部環境的輸入信息轉換成電信號。在大多數應用中,傳感器用于監測運動、光、氣壓、振動、流速、溫度、通風、電等。通常來說,傳感器元件在其輸出端生成電壓或電流信號。在數據被處理、存儲和傳輸之前,這些信號一般會被放大,并通過模數轉換器轉換成數字信號。

d)電源子系統 - 通常連接到電池或能量采集器。該子系統充當可控單元,可單獨打開和關閉系統構建塊的電源。它通常是MCU軟件中的一個軟件塊。電源子系統負責為每個單獨的硬件組件提供合適的電源電壓。

在具有多個傳感器的更復雜的基于微控制器的架構中,在硬件中集成了智能,用來控制各種子系統。 例如,從傳感器到存儲器傳輸數據耗時又耗電,這一部分工作其實可以從處理器轉移到直接內存存取(DMA)單元。電源管理單元(PMU)還可以被編程為對特定事件做出反應并關閉各種子系統,例如外設、傳感器和無線電。

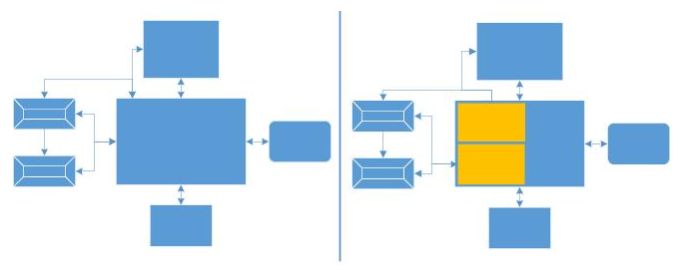

圖1. 基于微控制器的典型架構

這種先進架構的目的是盡可能減少主MCU活躍的時間。原來需要MCU干預的任務,現在可以由智能子系統執行。然而,還存在一個問題,就是每次有來自傳感器、無線電或各種子系統的事件時,MCU都需要被喚醒,因為它是唯一可以部署邏輯來處理這些事件的元件。

優化功率的技術 - 添加傳感器節點控制器

為了延長具有多個傳感器的系統的續航時間,已經提出了很多種降低功耗的技術[2],[3]。有些技術在媒體訪問控制層面進行節能[4],[5],有些技術從數據聚合或融合著手[6],[7],有的則采用芯片設計優化技術,如片上功率門控[ 8]或動態電壓調節[9]。

本文介紹了一種不同的技術,來優化多傳感器系統中的電源使用,同時將主處理器用于數據采集的喚醒時間控制到最短。該技術基于集成復雜的硬件狀態機,可以接管主處理器上的重復性任務,如傳感器輪詢和讀取,從而實現集成的低功耗傳感器中樞概念。專用硬件狀態機可以更快地喚醒,并使用更少的模塊來將數據從傳感器/外設傳輸到內存,以及反向傳輸,而主處理器保持休眠狀態。此外,傳感器中樞可以對數據執行簡單操作,因此主處理器只需要在要求復雜數據操作時喚醒。

這種方法的一個很好的例子,是集成在Dialog半導體公司的DA1469x藍牙低功耗SoC解決方案中的傳感器節點控制器(SNC)硬件模塊[10]。SNC是一種微型硬件狀態機,能運行由有限的指令集組成的微碼(μcode),有助于開發人員操控通信控制器(即SPI、I2C等)、傳感器和外設。它可以通過使用其最小指令集自動運行,無需喚醒系統的其余部分。這允許它執行眾多操作 - 例如:輪詢傳感器狀態位、比較寄存器與內存地址內容(值)、將數據從通信接口傳輸到系統RAM以及比較分支 - 同時消耗最低電流。

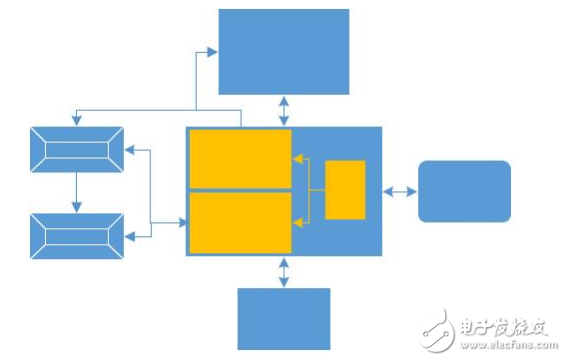

圖2. 具有傳感器節點控制器外設的應用處理器架構

SNC的主要特性如下(圖3):

·傳感器節點指令集(SeNIS),包含10條微碼生成指令,適用于:

- 輕松創建指向內存緩沖區的指針

- 輪詢串行接口狀態位

- 比較閾值

·系統RAM用于微碼存儲和數據

·DMA功能,用于將數據直接從通信接口傳輸到系統RAM

·直接訪問所有外設和寄存器

·通過PMU在中斷觸發和域上電(例如定時器、GPIO)后立即執行

·SNC到主處理器通知,以及反向通知

SNC與所有通信接口(SPI、I2C和UART)位于相同的電源域,SNC還可以控制其他電源域。它執行駐留在系統RAM中的微碼,其中SNC具有直接內存連接;以系統時鐘速度運行;并且可以生成中斷以通知PMU所有操作都已完成,從而可以關閉整個系統的電源。

圖3. 傳感器節點控制器框圖

使用此類專用硬件執行傳感器和外設數據操作的架構的主要優點是:

·主CPU睡眠時間更長,從而可以節省功耗

·節省MIPS,因為CPU不必訪問慢速外設或執行簡單的數據操作

不過它有一些缺點。SNC編程模型的非常簡單的指令集僅允許基本操作。另外,編程SNC需要使用匯編語言。最后,由于SNC是一個非常簡單的模塊,調試會變得復雜。

節省功耗和MIPS

我們已經進行了一系列測量,證明了使用SNC可以實現的功耗和MIPS節省。這些測量是在Dialog的基于ARM Cortex-M33的DA1469x SoC上進行的,并比較了只使用主CPU和在SNC支持下執行的相同任務。 第一組測量集中在訪問通常用于傳感器讀數的慢速外設(如I2C和SPI)時節省的功耗/MIPS。第二組測量著眼于使用DA1469x中包含的藍牙低功耗(BLE)通信模塊的實際應用案例。

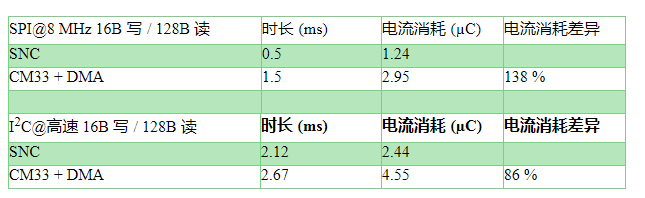

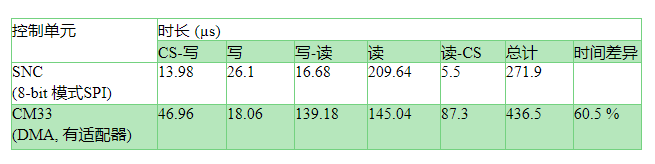

表1描述了傳輸小型SPI或I2C數據事務(如寫/讀16/128字節)時的能耗。

表1:傳輸小型數據事務時的能耗(數字為1.8 V,8-bit傳輸)

與CPU(CM33)相比,SNC執行事務所需的時間要短很多,如表2所示。由于CPU可能需要執行忙等待,因此節省了時間相當于節省了MIPS。

表2:SNC寫/讀8 bit數據所需的時間以及CPU相應所需的時間

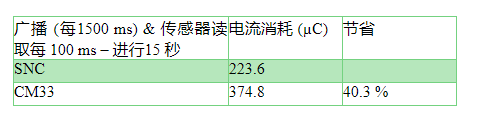

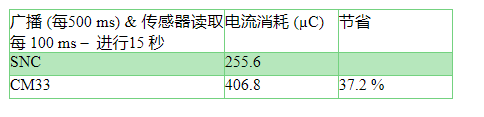

對現實生活中的使用案例,我們比較了每隔1500毫秒(表3)和500毫秒(表4)進行廣播時所消耗的功率,同時使用SPI每100毫秒讀取加速計傳感器一次。

表3:每1500毫秒進行廣播時的能耗,使用SPI每100毫秒進行一次傳感器讀取

表4:每500毫秒進行廣播時的能耗,使用SPI每100毫秒進行一次傳感器讀取

在復雜的應用中,如果需要訪問多個傳感器,考慮到緩存未命中和任務切換等問題,對MCU的占用會更大。

降低編程復雜度

上面提到過,使用集成的傳感器節點控制器時面臨的最大挑戰之一,是確保基礎系統功能的編程、調試和充分利用與采用通用MCU的方案一樣簡單。挑戰的主要方面有:

·提供對開發人員友好的抽象編程,以有效控制驅動與連接的傳感器/外設的通信接口,以及與主CPU通信相對應的基本功能。

·利用10指令匯編式編程,并提供更高級別的編程結構,以簡化和加速軟件開發。

·支持完整的系統整體調試 - 而不是單獨調試每個CPU內核,因為可能無法檢測到當內核并行運行時的系統行為錯誤。

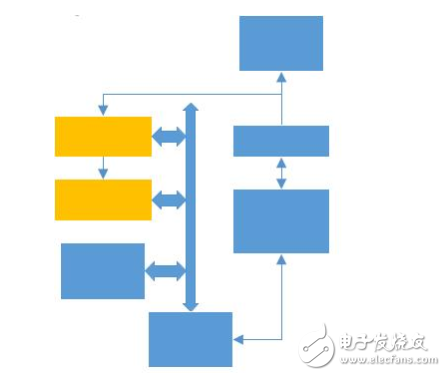

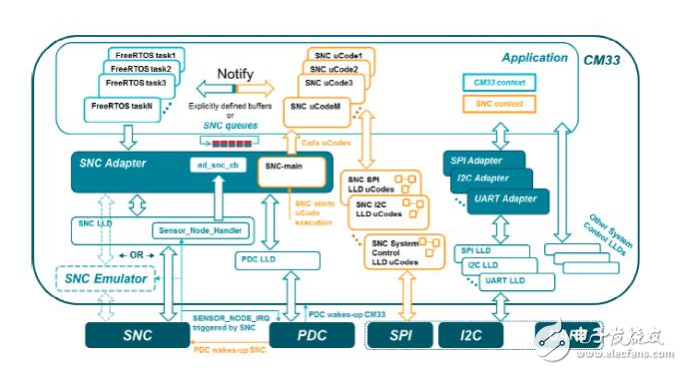

為了解決這些挑戰,我們需要一個完整、易于使用的編程框架。它必須包括抽象和程序,將并發操作系統任務的范例擴展到在SNC上執行的相應(并行)處理。我們已經為Dialog DA1469x解決方案開發了這樣的編程框架(圖4)。它具有以下特點:

·簡化的SNC微碼開發

- 通過定義基于SeNIS的類C編程語言,可以同時支持匯編和類C編程。

·用于編程的“混合”編碼模型

- 在相同的源和頭文件中同時包含針對SNC和主處理器情境(context)的代碼開發 - 使用了一個C預處理器來定義基于SeNIS的語言結構,方便開發人員。

·與驅動主處理器通信接口、交換SNC通知、和操作系統資源相關的基礎機制和功能的抽象,作為一組完整且易于使用的API程序/類C函數。

·可觀察性和高級調試機制同時應用于SNC和主處理器執行情境。

圖4. SNC編程框架

SNC編程模型的特征可歸納如下:

·DA1469x應用包括由OS任務和SNC 微碼并行執行的進程。

·SNC適配器向DA1469x系統注冊或注銷SNC微碼,從而創建一列SNC微碼,每個微碼由特定PMU事件觸發。

·SNC適配器采用特殊的SNC微碼,根據相應的微碼列表實現注冊的SNC微碼執行的調度,并通過其低級驅動器控制SNC硬件模塊。

·定義了一組基于SeNIS的結構預處理器宏,從而生成一組匯編和類C語言結構用于SNC微碼開發。

·提供一組低級驅動器SNC微碼,可用于驅動SPI、I2C等通信外設。

·為操作系統任務和SNC微碼提供了一種機制,進行交換:

- 通知

- 數據(即:SNC 隊列)

除了上述實現輕松編程SNC函數的結構之外,還提供以下內容以支持調試:

·使用SNC斷點和逐步調試區域來調試SNC微碼的機制。

·SNC仿真器,而不是SNC硬件模塊,用于改進和簡化SNC微碼調試過程。

總結

本文介紹了一種新的架構,可最大限度地降低集成了多個傳感器和外設的便攜式系統的功耗。該架構使用復雜的硬件狀態機來卸載主處理器上的一些重復性任務,例如傳感器/外設輪詢和讀取。與其他架構相比,這種新架構在功耗和MIPS優化方面具有很大的優勢,不過會使編程模型變的更復雜。因此,我們還介紹了一種對開發人員友好的編程框架來克服該問題。

作者:

Marios Iliopoulos, Fotios Kerasiotis, Nikolaos Moschopoulos

參考文獻

[1] Goran Nikoli?, Mile Stoj?ev, Zoran Stamenkovi?, Goran Pani?, Branislav Petrovi?, “Wireless Sensor Node with low power sensing”, Electronics and Energetics Vol. 27, No 3, September 2014, pp. 435 - 453

[2] V. Raghunathan, S. Ganerival, and M. Srivastava, “Emerging Techniques for Long Lived Wireless Sensor Networks”, IEEE Communication Magazine, 2006, Vol.41, No. 4, (pp. 130-141)

[3] G. Anastasi, M. Conti, M. Di Francesco, and A. Passarella, “Energy Conservation in Wireless Sensor Networks: A survey”, Ad Hoc Networks, 2009, Vol. 7, (pp. 537–568)

[4] W. Ye, J. Heidemann, and D. Estrin, “An Energy-Efficient Mac Protocol for Wireless Sensor Networks,” Proc. IEEE Infocom, New York (USA) 2002, (pp. 1567-1576)。

[5] M. Al Ameen, S.M. Riazul Islam, and K. Kwak, “Energy Saving Mechanisms for MAC Protocols in Wireless Sensor Networks”, Hindawi Publishing Corporation International Journal of Distributed Sensor Networks, Volume 2010 (2010), Article ID 163413, (pp 1-16)

[6] M. Hempstead, N. Tripathi, P. Mauro, G.-Y. Wei, and D. Brooks, “An Ultra Low Power System Architecture for Sensor Network Applications,” Proc. 32nd Annual International Symposium on Computer Architecture, Madison (USA) 2005, (pp. 208-219)。

[7] A. Boulis, S. Ganeriwal, and M. Srivastava, “Aggregation in Sensor Networks: An Energy Accuracy Trade-Off”, Ad Hoc Networks, Vol. 1, 2003, (pp. 317–331)

[8] G. Pani?, Z. Stamenkovi?, and R. Kraemer, “Power Gating in Wireless Sensor Networks”, Wireless Pervasive Computing, 2008. ISWPC2008. 3rd International Symposium on Santorini, Greece, May 2008, (pp. 499-503)

[9] T. Burd, and R. Brodersen, “Energy Efficient Microprocessor Design”, Kluwer Academic Publishers, Norwell MA, USA, 2002

[10] Dialog Semiconductor, “DA1469x Datasheet”

電子發燒友App

電子發燒友App

評論