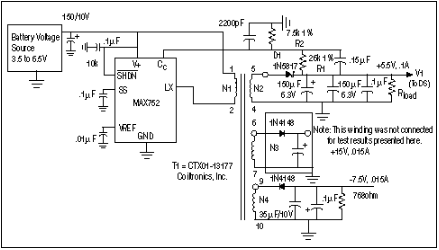

CCD 電壓非常“非標準”。高電平時鐘電壓通常大于我們用于 CMOS 邏輯的電壓,而低電平電壓通常延伸到地電位以下。

我隨機選擇了一些 CCD 數(shù)據(jù)表,為您提供一些預期的示例。如果您不明白我所說的“幀傳輸”和“行間傳輸”的含義,請務(wù)必閱讀上一篇文章。

安森美半導體的 KAI-1020:這是一款行間傳輸器件,分辨率為 1000 × 1000 活動像素。控制電壓范圍為 –9V 至 +15V。但是,應用于芯片的控制信號使用 5V 邏輯;內(nèi)部驅(qū)動器將邏輯信號轉(zhuǎn)換為電荷傳輸門所需的電壓電平。

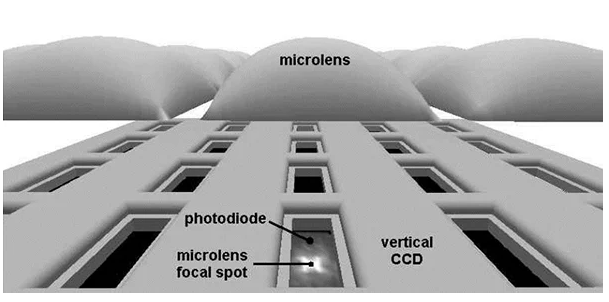

我想您可能會喜歡這個來自 KAI-1020 數(shù)據(jù)表的行間傳輸 CCD 的流暢 3D 表示。

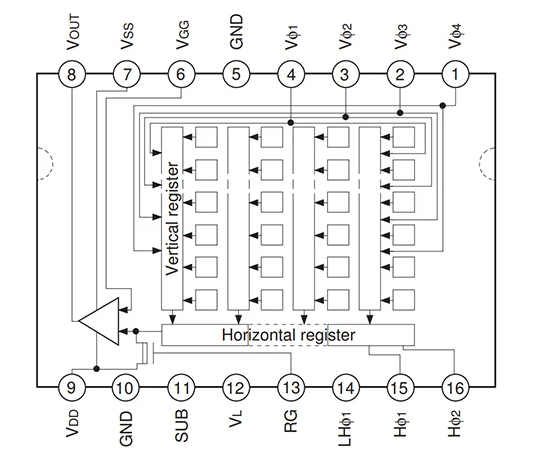

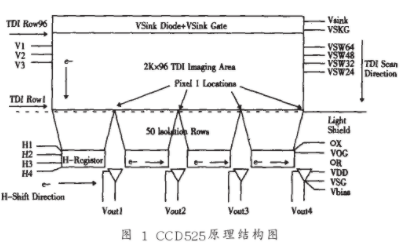

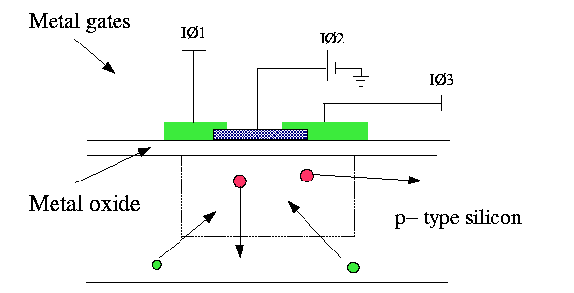

Sony 的 ICX059CL:這是一款 752 × 582 像素、行間傳輸 CCD,適用于單色攝像機。如果我正確理解數(shù)據(jù)表,它使用 15 V 將電荷包從光電二極管傳輸?shù)酱怪币莆?a href="http://www.nxhydt.com/tags/寄存器/" target="_blank">寄存器,使用 –8.5 V 到 0 V 進行垂直傳輸時鐘,使用 0 V 到 5 V 進行水平傳輸。下圖傳達了該設(shè)備的整體架構(gòu)。

圖表取自 ICX059CL數(shù)據(jù)表。

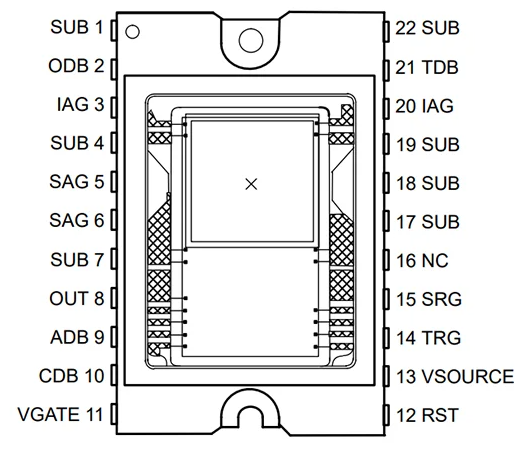

Texas Instruments 的 TC281:這款 1000 × 1000 像素圖像傳感器采用幀傳輸架構(gòu)。大多數(shù)時鐘的低電平為 –10 V,高電平為 +2 V。

帶×符號的部分是感光像素陣列,下半部分是存儲陣列。該圖取自 TC281數(shù)據(jù)表。

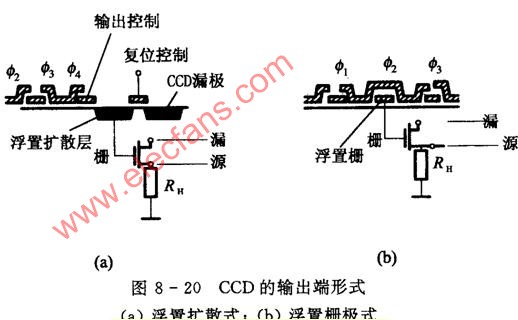

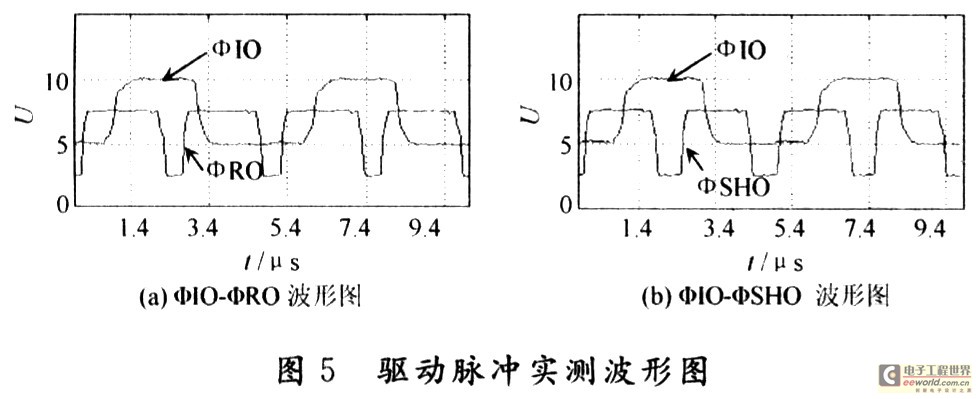

讀出時鐘配置

讓我們回到半導體層面,討論如何準確地說服電荷包從像素移動到輸出端子。我們知道,這是通過施加電壓序列來實現(xiàn)的,電壓序列依次創(chuàng)建勢阱和勢壘序列,但事實證明,有幾種不同的方法可以創(chuàng)建必要的電勢變化。

四相時鐘

直接的方法使用四個時鐘相位。我們將詳細考慮四階段方法,然后我將簡要提及其他方案。

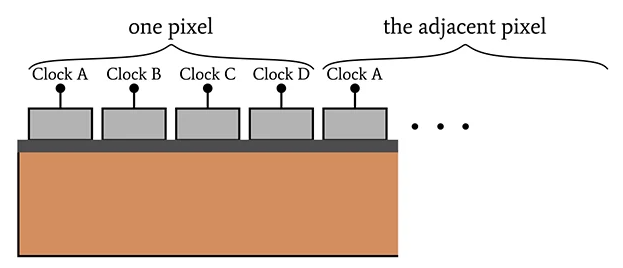

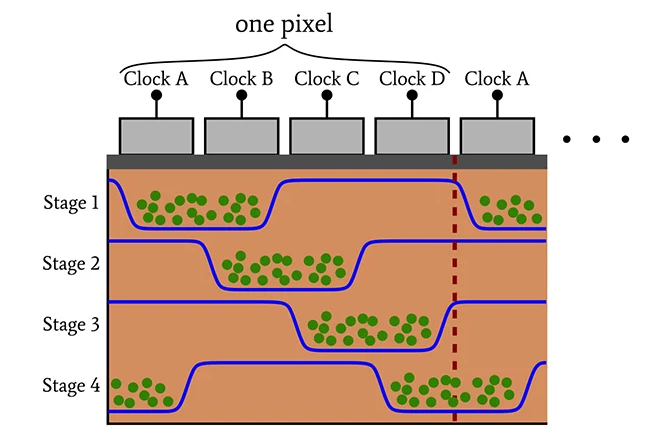

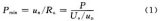

如下圖所示,四相 CCD 每個像素有四個門。因此,需要施加到像素的四個不同部分的四個單獨的時鐘信號來將電荷包移動到相鄰像素中。

(請注意,如果這是行間傳輸 CCD,我們可能會說“移位寄存器部分”而不是“像素”,因為電荷包不會穿過行間傳輸架構(gòu)中的光敏區(qū)域。)

該過程從我們所說的階段 1 開始。時鐘 A 和時鐘 B 為高電平,時鐘 C 和時鐘 D 為低電平。(請記住,“高”意味著更高的電壓,會產(chǎn)生吸引電子的勢阱,而“低”會產(chǎn)生阻擋電子的勢壘。)

在繼續(xù)之前,請先看一下下圖,并在我們完成接下來的三個階段時參考它。

在階段,電荷在A門和B門下方的勢阱中積累,并且由于被C門和D門下方的勢壘阻擋而無法移動。

在階段 2中,時鐘 A 變低,時鐘 C 變高。時鐘 B 和 D 不變。這會將所有電子向右移動一步,因為現(xiàn)在在門 B 和 C 下有一個阱,在門 A 和 D 下有一個勢壘。

在階段 3中,時鐘 B 變低,時鐘 D 變高。我們再次將電子向右推了一步,因為現(xiàn)在勢阱位于門 C 和 D 下方。

在第 4 階段,時鐘 A 變高,時鐘 C 變低。現(xiàn)在我們有一個勢阱,從一個像素的柵極 D 延伸到下一個像素的柵極 A。

階段5與階段1相同。電荷完全轉(zhuǎn)移到相鄰像素,并且循環(huán)繼續(xù)。

三相、兩相和單相時鐘

四相方案的問題是傳感器分辨率受到每個像素需要四個門的限制。我們可以通過減少電荷傳輸所需的時鐘數(shù)量來減小像素尺寸,從而提高像素密度,但為了減少時鐘數(shù)量,所施加的電壓必須變得更加復雜。

四相控制的替代方案是三相、偽兩相、真兩相和虛擬相(即單時鐘)控制。以上述 CCD 傳感器為例,KAI-1020 使用兩相時鐘,ICX059CL 使用四相時鐘,TC281 使用 TI 描述的“專有虛擬相位”時鐘方案。

電子發(fā)燒友App

電子發(fā)燒友App

評論